STM32从设置IO输入上下拉到寄存器GPIOx_BSRRGPIOx_BRR

Posted 何事误红尘

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STM32从设置IO输入上下拉到寄存器GPIOx_BSRRGPIOx_BRR相关的知识,希望对你有一定的参考价值。

1. 问题概述

因为一些原因使用寄存器方式进行开发,设置IO状态时发现:

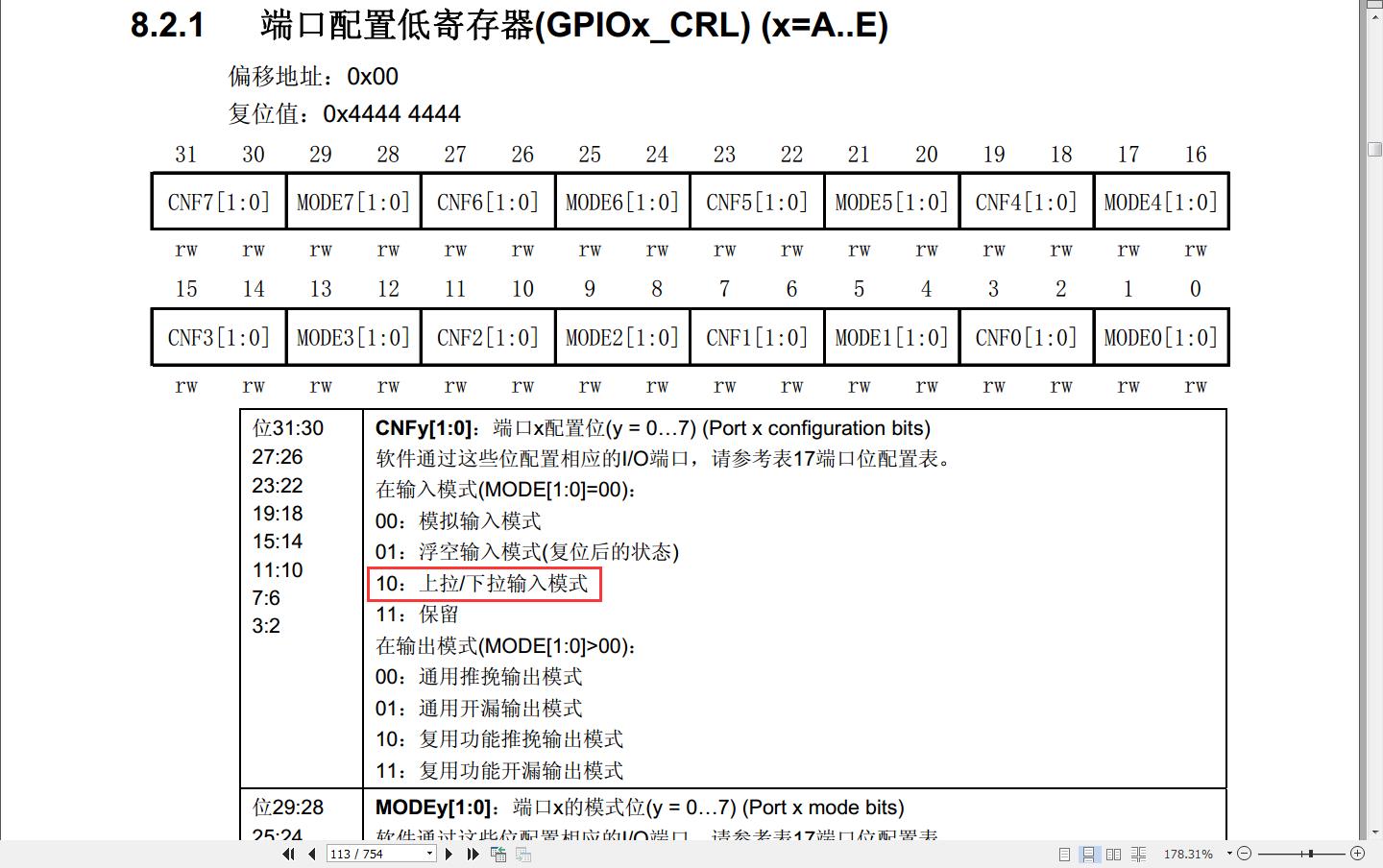

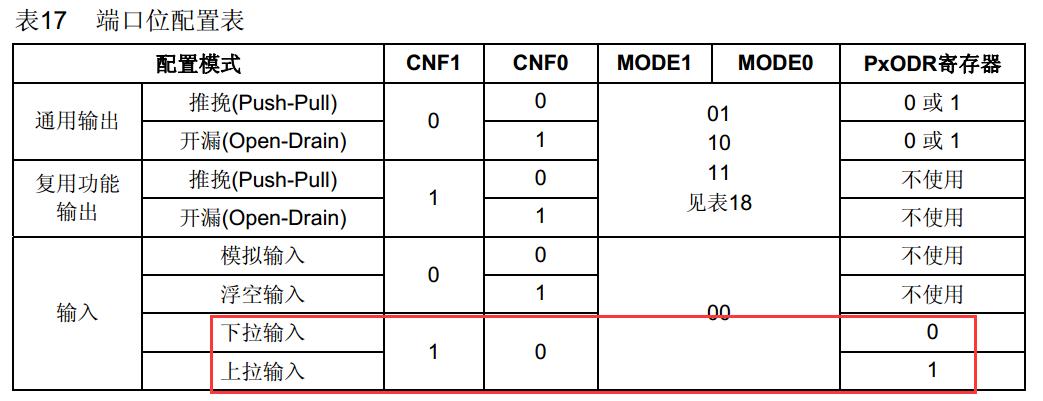

表格中10表示上拉/下拉输入模式,到底是上拉还是下拉呢?以往使用库方式开发没有关系过这个问题,现在使用寄存器方式开发,到底该如何设置上下拉?

表格中提到请参考表17端口位配置表,不过也可以先去标准库看一看,对照查看加深理解。

2. 标准库中查找

首先想到去标准库中对照看下是如何配置的。标准库中通过枚举定义出支持的IO模式:

/**

* @brief Configuration Mode enumeration

*/

typedef enum

{ GPIO_Mode_AIN = 0x0,

GPIO_Mode_IN_FLOATING = 0x04,

GPIO_Mode_IPD = 0x28,

GPIO_Mode_IPU = 0x48,

GPIO_Mode_Out_OD = 0x14,

GPIO_Mode_Out_PP = 0x10,

GPIO_Mode_AF_OD = 0x1C,

GPIO_Mode_AF_PP = 0x18

}GPIOMode_TypeDef;

可以看出上下拉是要区分配置的,然后查找函数

void GPIO_Init(GPIO_TypeDef* GPIOx, GPIO_InitTypeDef* GPIO_InitStruct)的定义,其中IO模式部分如下:

/* Reset the corresponding ODR bit */

if (GPIO_InitStruct->GPIO_Mode == GPIO_Mode_IPD)

{

GPIOx->BRR = (((uint32_t)0x01) << pinpos);

}

else

{

/* Set the corresponding ODR bit */

if (GPIO_InitStruct->GPIO_Mode == GPIO_Mode_IPU)

{

GPIOx->BSRR = (((uint32_t)0x01) << pinpos);

}

}

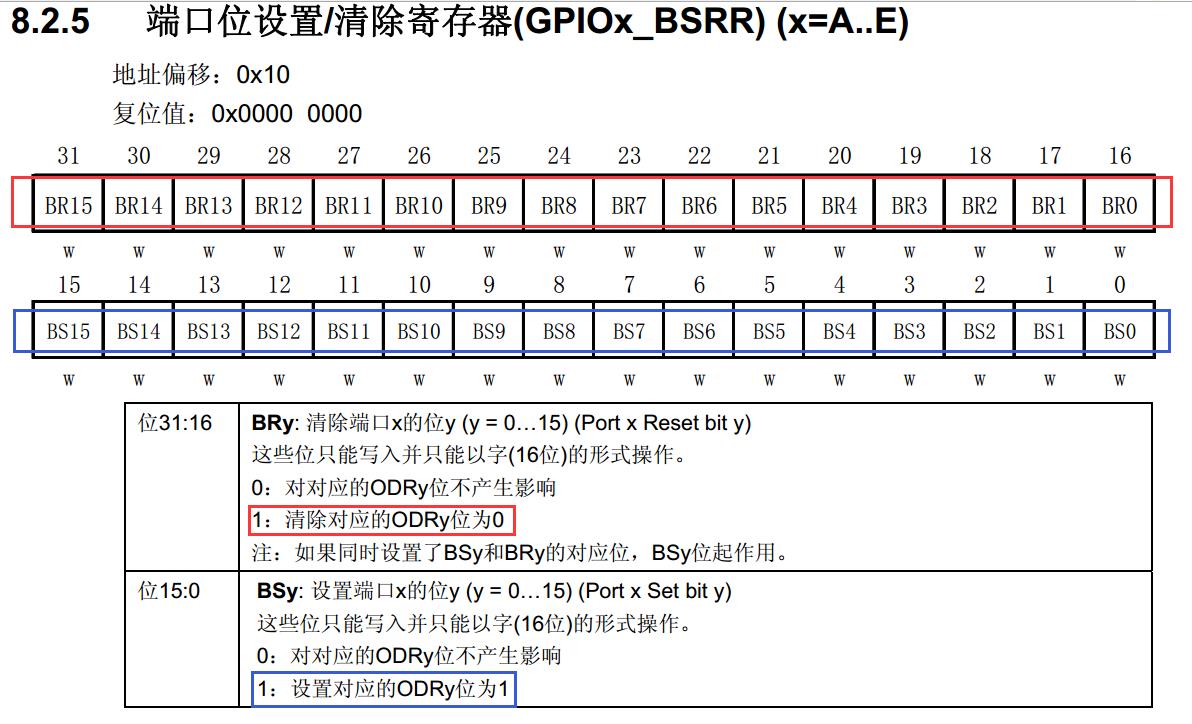

可以看出需要GPIOx_BSRR和GPIOx_BRR两个寄存器来具体配置上下拉。

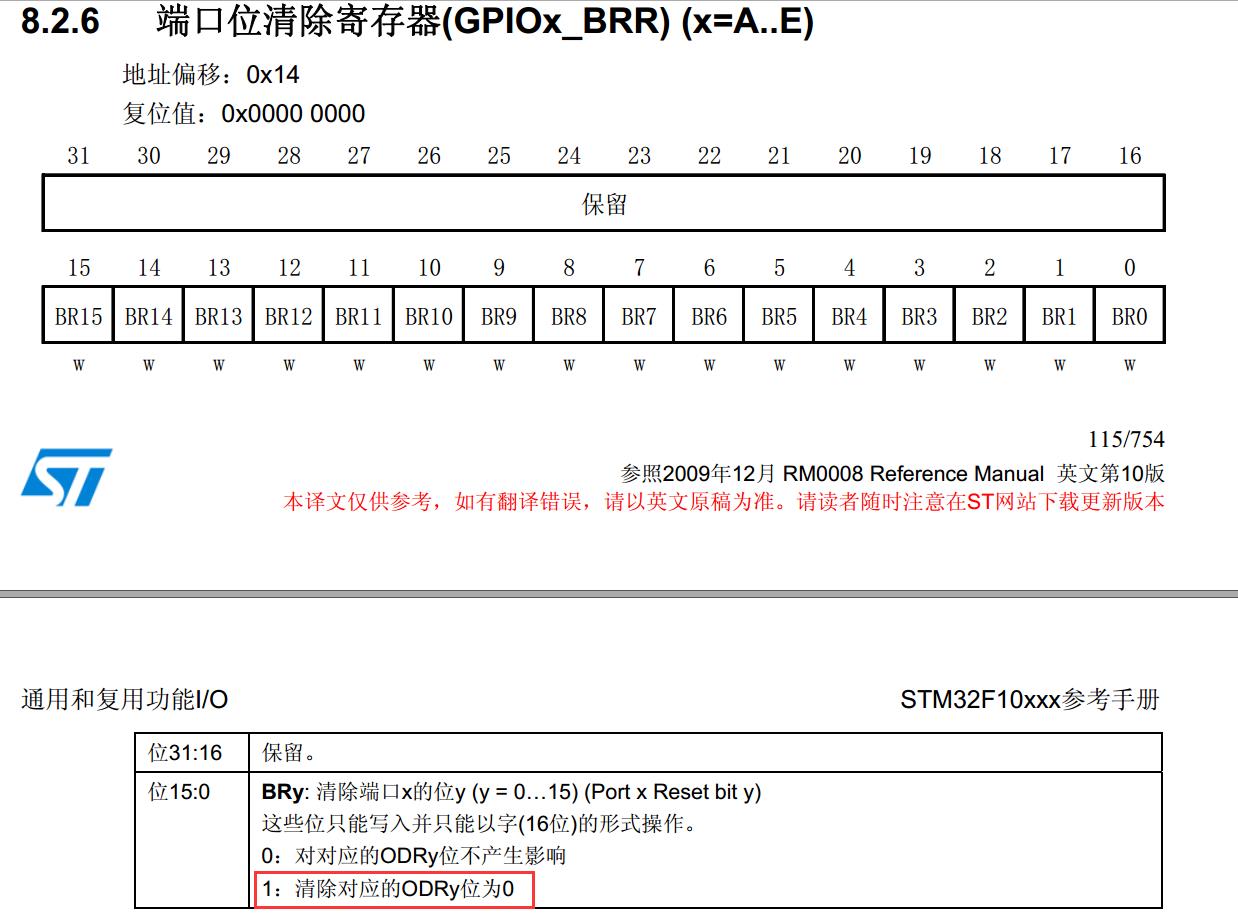

3. GPIOx_BSRR和GPIOx_BRR

在手册中查看两个寄存器的定义:

GPIOx_BSRR的高16位已经实现了GPIOx_BRR寄存器的功能,那为什么还要有一个GPIOx_BRR呢?一种说法是:

这个设计跟IC设计者和用户习惯都有关系,有些用户就习惯set 和 reset 分开操作两个不同的寄存器,IC设计者需要照顾他们的习惯。

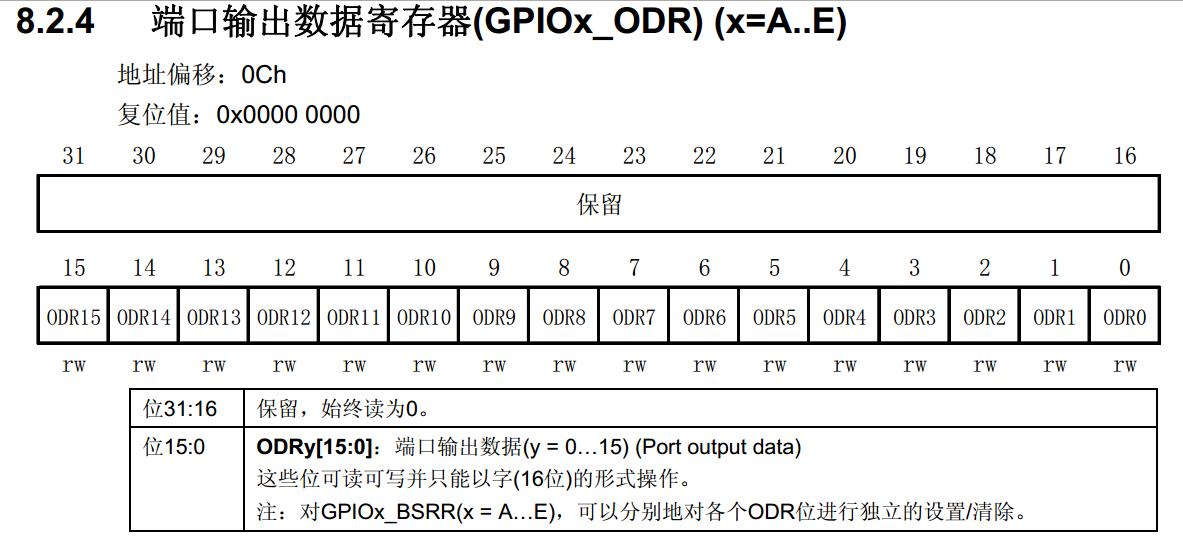

GPIOx_BSRR和GPIOx_BRR这两个寄存器是用来修改GPIOx_ODR寄存器的,其定义如下:

想把IO配置成输入上拉/下拉,怎么还需要配置端口输出数据寄存器呢?

端口位配置表

前面先到标准库中绕了一圈,现在回到手册中查找表17:

这里直接给出了上拉和下拉的区别配置。表格中CNF1、CNF0、MODE1、MODE0即对应本文开头GPIOx_CRL的4 bit,而PxODR也就是上面的端口输出数据寄存器(GPIOx_ODR)。

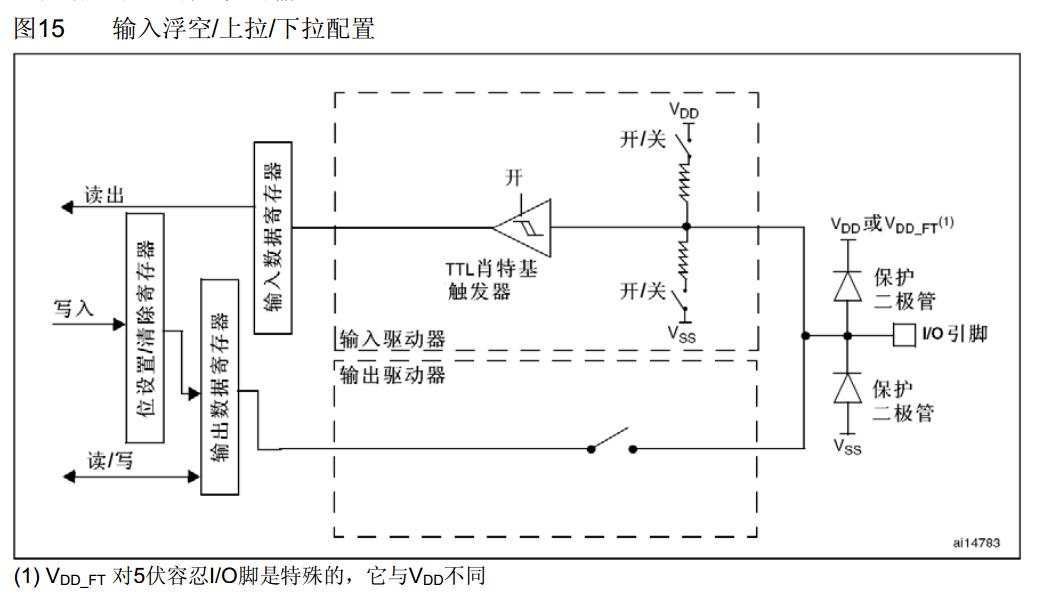

查看IO端口输入配置:

哪位大佬看到可以指点下,端口输出数据寄存器是如何影响输入上下拉的?

以上是关于STM32从设置IO输入上下拉到寄存器GPIOx_BSRRGPIOx_BRR的主要内容,如果未能解决你的问题,请参考以下文章