数字电路个人实验

Posted HEYUL

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路个人实验相关的知识,希望对你有一定的参考价值。

代码

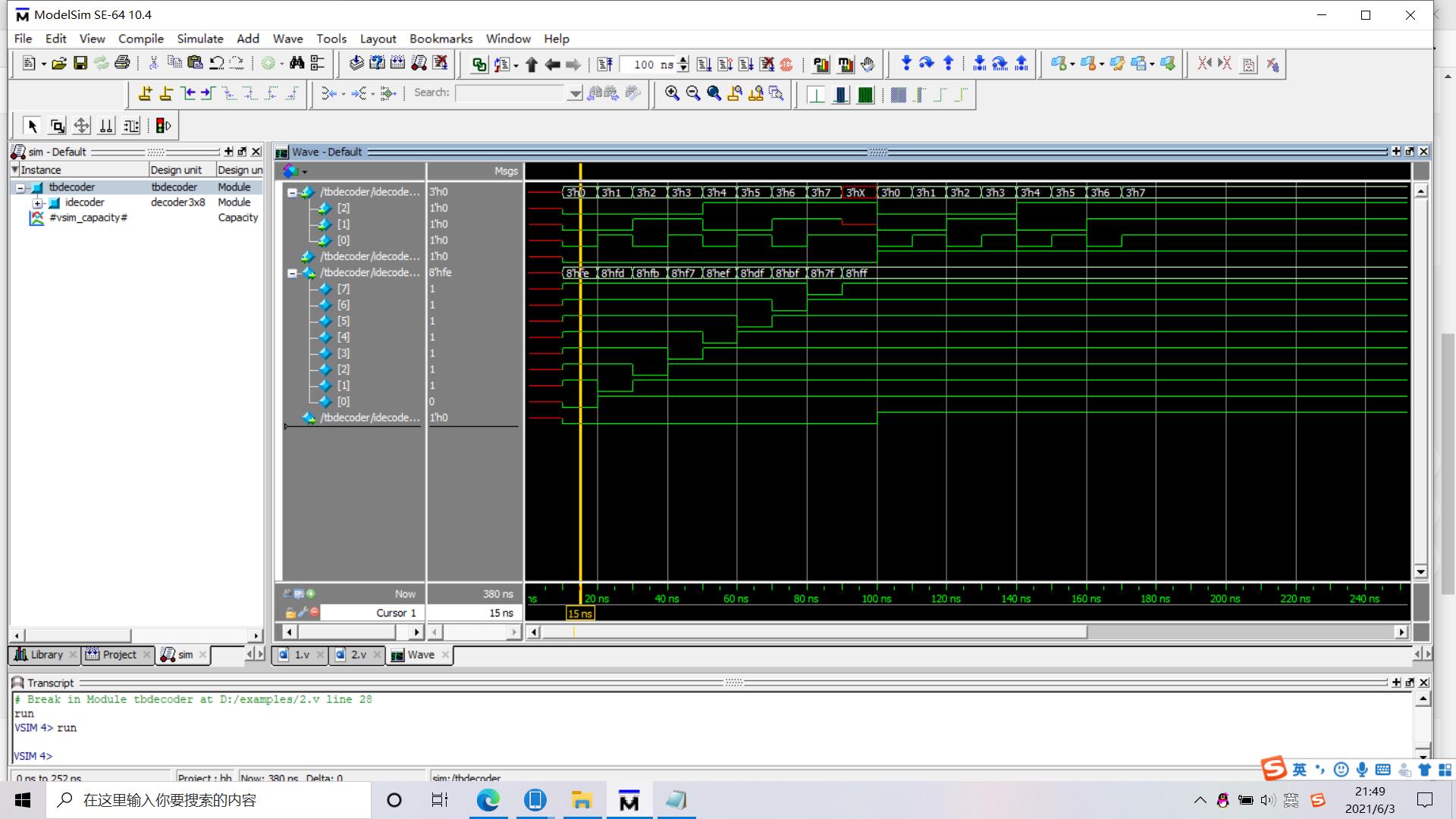

module decoder3x8 (din, en, dout,ex) ;input [2:0] din; input en; output[7:0] dout; output ex; reg [7:0] dout; reg ex; always @ (din or en) if (en) begin dout=8'b1111_1111; ex=1'b1; end else begin case (din) 3'b000:begin dout=8'b1111_1110; ex=1'b0; end 3'b001:begin dout=8'b1111_1101; ex=1'b0; end 3'b010: begin dout=8'b1111_1011; ex=1'b0; end 3'b011:begin dout=8'b1111_0111; ex=1'b0; end 3'b100: begin dout=8'b1110_1111; ex=1'b0; end 3'b101:begin dout=8'b1101_1111; ex=1'b0; end 3'b110:begin dout=8'b1011_1111; ex=1'b0; end 3'b111:begin dout=8'b0111_1111; ex=1'b0 ; end default:begin dout=8'b1111_1111; ex=1'b0; end endcase

end

endmodule

测试文件

module tbdecoder;reg [2:0] din;

reg en;

wire [7:0] dout;wire ex;

initial

begin

#10 en=0;din=3'b000;

#10 en=0;din=3'b001;

#10 en=0;din=3'b010;

#10 en=0;din=3'b011;

#10 en=0;din=3'b100;

#10 en=0;din=3'b101;

#10 en=0;din=3'b110;

#10 en=0;din=3'b111;

#10 en=0;din=3'b1x1;

#10 en=1;din=3'b000;

#10 en=1;din=3'b001;

#10 en=1;din=3'b010;

#10 en=1;din=3'b011;

#10 en=1;din=3'b100;

#10 en=1;din=3'b101;

#10 en=1;din=3'b110;

#10 en=1;din=3'b111;

#10 $stop;

end

decoder3x8 idecoder (din, en, dout,ex) ;

endmodule

代码

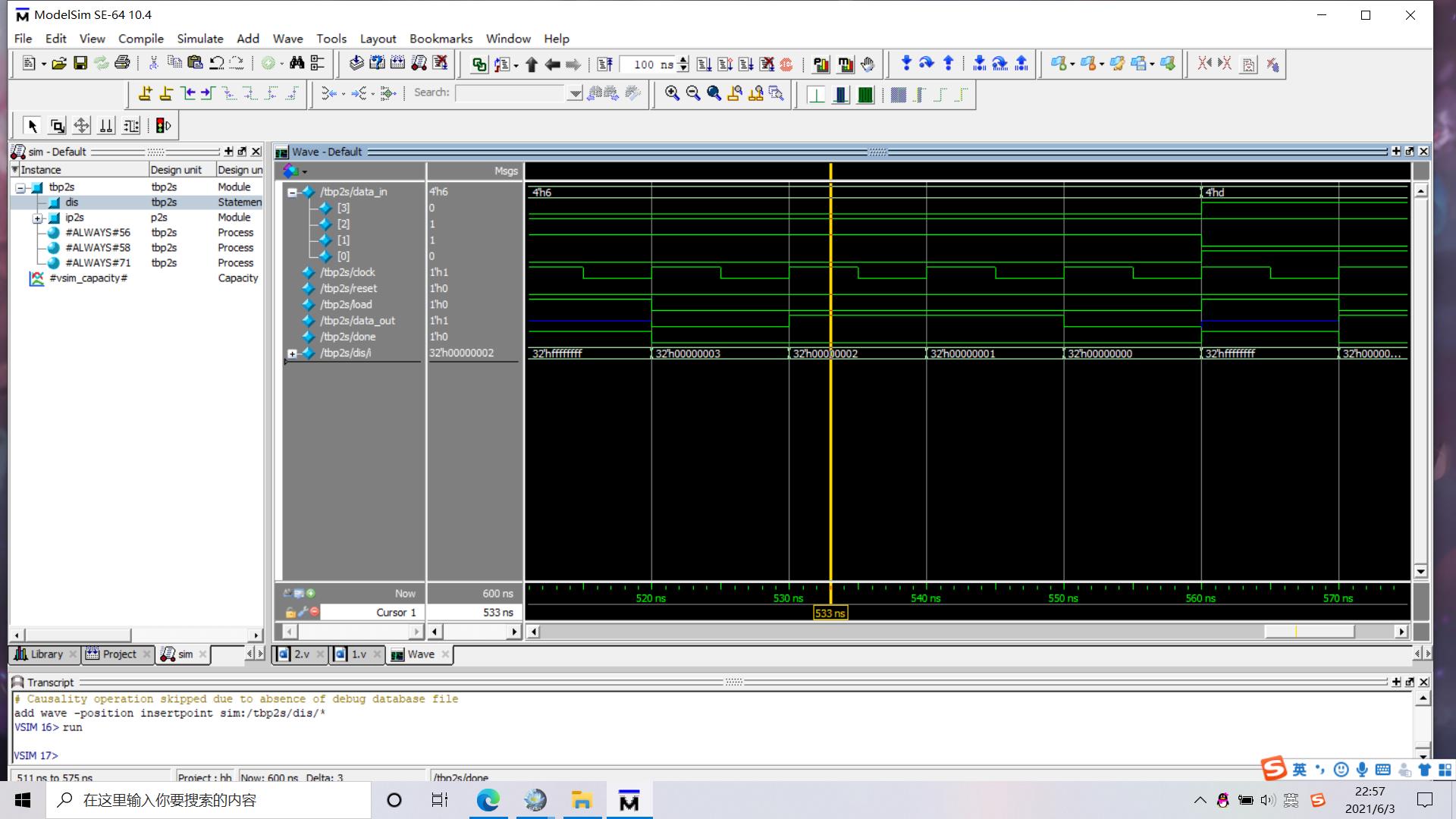

module p2s (data_in,clock,reset,load,data_out,done) ;

input [3:0] data_in;

input clock, reset, load;

output data_out;

output done;

reg done;

reg [3:0] temp;

reg [3:0] cnt;

always@ (posedge clock or posedge reset )begin

if (reset)

begin

temp<=0;

cnt<=0;

done<=1;

end

else if(load)

begin

temp<=data_in;

cnt<=0;

done<=0;

end

else if (cnt==3)

begin

temp <={temp[2:0],1'b0};

cnt<=0;

done<=1;

end

else

begin

temp <={temp[2:0],1'b0};

cnt<=cnt+1;

done<=0;

end

end

assign data_out=(done==1)?1 'bz:temp[3];

endmodule

测试文件

module p2s(data_in,clock,reset,load,data_out,done);

input [3:0] data_in;

input clock,reset,load;

output data_out;

output done;

reg done;

reg [3:0] temp;

reg [3:0] cnt;

always@(posedge clock or posedge reset )

begin

if(reset)

begin

temp<=0;

cnt<=0;

done<=1;

end

else if(load)

begin

temp<=data_in;

cnt<=0;

done<=0;

end

else if(cnt==3)

begin

temp <= {temp[2:0],1'b0};

cnt<=0;

done<=1;

end

else

begin

temp <= {temp[2:0],1'b0};

cnt<=cnt+1;

done<=0;

end

end

assign data_out=(done==1)?1'bz:temp[3];

endmodule

module tbp2s;

reg [3:0] data_in;

reg clock,reset,load;

wire data_out;

wire done;

initial

begin

reset=1;

#15 reset=0;

end

initial clock=1;

always #5 clock=~clock;

always @(done)

begin

if(done==1)

begin

data_in=$random%16;

load=1;

end

else

begin

load=0;

end

end

always @(posedge clock)

if(load==1)

begin:dis

integer i;

i=3;

repeat(4)

begin

@(posedge clock)

if(data_out==data_in[i])

$display("Output Right!");

else

$display("Bed Output!data_out= %b ,but data_in[%d]= %b",data_out,i,data_in[i]);

i=i-1;

end

end

p2s ip2s(data_in,clock,reset,load,data_out,done);

endmodule

————————————————

版权声明:本文为CSDN博主「HEYUL」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_53156932/article/details/117536582

以上是关于数字电路个人实验的主要内容,如果未能解决你的问题,请参考以下文章