An 8Bit 4GS/s 120 mW CMOS ADC

Posted 夏风喃喃

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了An 8Bit 4GS/s 120 mW CMOS ADC相关的知识,希望对你有一定的参考价值。

An 8Bit 4GS/s 120 mW CMOS ADC

作者:Hegong Wei, Peng Zhang, Bibhu Datta Sahoo and Behzad Razavi

机构:Electrical Engineering Department, University of California, USA

期刊:IEEE JOURNAL OF SOLID-STATE CIRCUITS(JSSC)

时间:2014

摘要

时间交错ADC采用四个流水线时间交错通道,以及新的时序失配检测算法和高分辨率可变延迟线。数字背景校准技术抑制了通道间时序不匹配,在65nm CMOS工艺中实现了44.4dB的SNDR和219 fJ/转换步长的品质因数。

关键词

模数转换、交错、流水线模数转换器(ADC)、时间误差检测和校正、时序校准、可变延迟线

文章目录

一. 介绍

对于给定的分辨率,ADC的功耗随着速度的增加而线性上升,直到某个点,然后开始以越来越高的速率上升。因此,对于较慢的设计,品质因数(FOM)保持相对恒定,对于较快的转换器,品质因数往往会下降。另一方面,通过时间交错,每个通道被给予更长的转换周期,从而返回到线性功率速度区域。例如,[1]–[3]使用交错来达到GHz的采样速率,分辨率为10至12位,但它们依赖于精心的布局来最小化通道间的不匹配。

本文介绍了一种8 bit 4 GS/s交错ADC,结合了一种新的时序失配校准技术。所提出的技术不需要数字乘法,因此适合于低功率、低复杂度的实现。还介绍了一种低抖动、高精度的定时校正方法。通过四个交错流水线通道,该ADC在65nm CMOS工艺中实现了219 fJ/转换周期的FOM。

第二节提供了这项工作的背景,处理交织问题和可容忍的不完善之处。第三节描述了建议的时序失配校准技术。第四节介绍了ADC的实现。第五节总结了实验结果。

二. 背景

A. 交错考虑

ADC架构通常会带来“时序开销”,这种开销只会随着功耗的增加而微弱地增加。例如,在流水线系统中,子ADC响应、DAC建立时间、时钟的非重叠时间以及时钟的上升和下降时间最终由工艺决定,即使功耗不重要,也会给转换周期设置下限。例如,在[6]中描述的用于每个通道的1 GHz ADC设计在65 nm技术中表现出以下值:180 ps的子ADC响应、45 ps的DAC时间常数、50 ps的非重叠时间和20 ps的时钟跃迁。因此,由于DAC建立大约需要六个时间常数,即使每一级中的残余放大器承担线性功率-速度权衡,也很难适应远低于500 ps的转换时间。

这种情况自然需要交织,理想情况下交织的系数足够大,使得弱可伸缩的时间开销仅占每个信道周期的一小部分。这样的选择将允许在线性功率-速度区域操作,从而提供最低的FOM。然而,有几个因素反对增加通道的数量:1)直接的面积惩罚;2)成比例更高的输入电容,这可能需要耗电的缓冲器;以及3)由于模拟输入和时钟相位到通道的路由而导致的额外不匹配。因此,妥协是必要的。这项工作采用了四个通道。

交错带来通道间不匹配,要求校准技术。失调和增益不匹配的校正相当简单,但时序不匹配带来了更大的挑战,是本工作的关注点。

B. 可容忍的不完美

在开发时序不匹配的校准算法之前,我们必须确定系统校准后剩余的最大容许缺陷。具体来说,我们必须决定:1) hog失配是可接受的,以及2)如果在模拟域中执行,时序校正会产生多大的抖动。

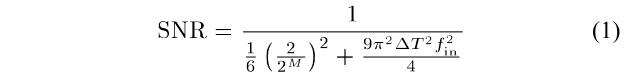

为了解决第一点,我们计算由时序不匹配引起的信噪比(SNR)损失。可以看出,对于检测频率为

f

i

n

f_{in}

fin正弦输入的四个M-bit交错ADC,我们有

其中

Δ

T

\\Delta T

ΔT表示第二、第三和第四通道相对于第一通道的均方根失配。图1描绘了如果

M

=

8

M=8

M=8和

f

i

n

=

2

G

H

z

f_{in}=2GHz

fin=2GHz时,对不同SNR损失最大容许值

Δ

T

\\Delta T

ΔT。我们观察到1 dB的损失表示为

Δ

T

<

180

f

s

\\Delta T <180 fs

ΔT<180fs。实际上,我们的目标是更小的残余失配,因为时钟抖动和ADC电子噪声等其他缺陷也需要在(1)的分母中有自己的预算。

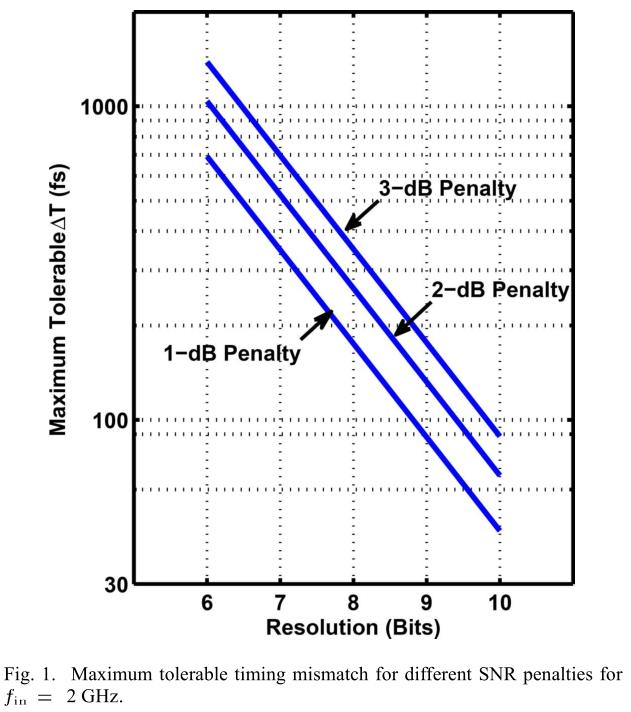

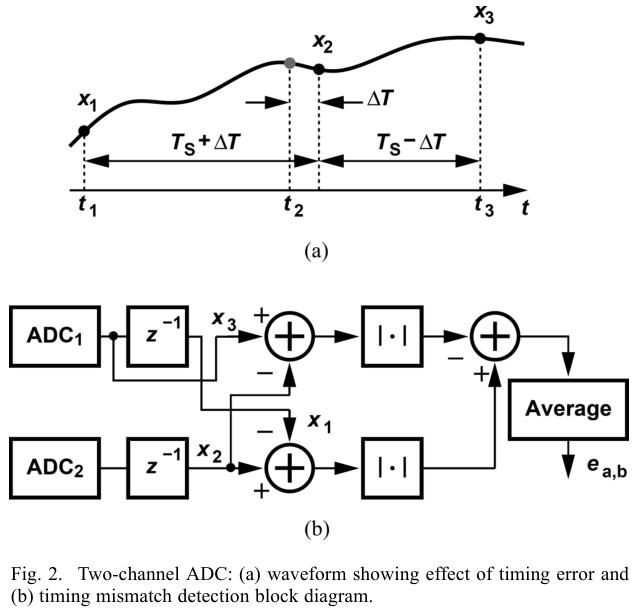

对于第二点,即抖动引起的信噪比(SNR)损失,我们还写道

其中

σ

t

\\sigma_{t}

σt为均方根抖动。在这种情况下,如果

M

=

8

M=8

M=8和

f

i

n

=

2

G

H

z

f_{in}=2GHz

fin=2GHz,1 dB的损失表示

σ

t

<

130

f

s

\\sigma_{t}<130 fs

σt<130fs。出于与上述相同的原因,校正电路产生的抖动必须远低于该值。

三. 建议的时间-失配校准

针对交错式ADC,已经提出了许多时序失配技术。其中,工作[9]和[16]需要额外的通道进行校准,工作[19]的输入带宽有限,工作[5],[9]–[11]需要数字乘法器,工作[7]和[13]采用长FIR滤波器。

与其他类型的错误一样,时序不匹配可以通过执行两个功能来消除,即检测和校正,前者更适合数字领域。对于后者,我们可以选择:1)数字域,因此在输出数据路径中有一个足够长的高速FIR滤波器[7],这可能会消耗高功率;或者2)模拟域,并且因此使用会增加抖动的可变延迟线(VDL)。在这项工作中,检测和校正分别在数字和模拟域中实现,并在后台运行。

A. 时序不匹配检测

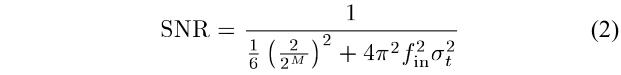

所提出的检测方法仅包含寄存器和数字加法器。我们首先描述两个交错通道的概念。假设,如图2(a)所示,通道1在

t

=

t

1

t=t_1

t=t1和

t

3

t_3

t3处对模拟输入

x

(

t

)

x(t)

x(t)进行采样,通道2在

t

=

t

2

t=t_2

t=t2处,其

t

2

t_2

t2相对于理想值的偏移为

Δ

T

\\Delta T

ΔT。这意味着样本

x

1

x_1

x1和

x

2

x_2

x2之间的时间差比

x

2

x_2

x2和

x

3

x_3

x3之间的时间差多(或少)

2

Δ

T

2\\Delta T

2ΔT秒。现在让我们形成两个差

x

2

−

x

1

x_2-x_1

x2−x1和

x

3

−

x

2

x_3-x_2

x3−x2,并直观地注意到,如果

Δ

T

\\Delta T

ΔT为零,则它们的平均值会相等。换句话说,我们猜测

∣

x

2

−

x

1

∣

−

∣

x

3

−

x

2

∣

|x_2-x_1|-|x_3-x_2|

∣x2−x1∣−∣x3−x2∣的平均值与

Δ

T

\\Delta T

ΔT成正比(绝对值是必要的,以确保连续样本不会相互抵消)。很难直接证明这个猜想,但是如果我们用平方函数来近似绝对值运算,我们就可以发展一些见解。

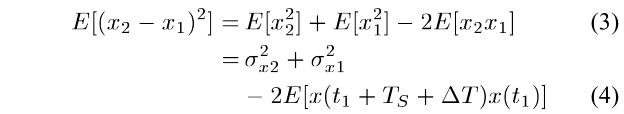

我们的目标是证明

(

x

2

−

x

1

)

2

(x_2-x_1)^2

(x2−x1)2和

(

x

3

−

x

2

)

2

(x_3-x_2)^2

(x3−x2)2之间的平均差值与

Δ

T

\\Delta T

ΔT成比例。我们把

(

x

2

−

x

1

)

2

(x_2-x_1)^2

(x2−x1)2期望写成

其中

T

S

T_S

TS表示标称采样周期,

σ

2

\\sigma^2

σ2是平均功率。因为(4)右边的期望实际上是

x

(

t

)

x(t)

x(t)的自相关,

R

(

τ

)

R(\\tau)

R(τ)在

T

S

+

Δ

T

T_S+\\Delta T

TS+ΔT处评估,我们有

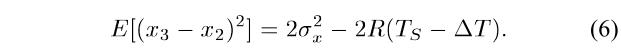

同样,

(

x

3

−

x

2

)

2

(x_3-x_2)^2

(x3−x2)2的平均值等于

对于较小的

Δ

T

\\Delta T

ΔT,

R

(

T

S

±

Δ

T

)

≈

R

(

T

S

)

±

Δ

T

d

R

/

d

τ

R(T_S±\\Delta T)≈R(T_S)±\\Delta TdR/d\\tau

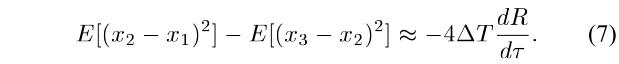

R(TS±ΔT)≈R(TS)±ΔTdR/dτ,得出平均值之间的差值为

因此,如果

d

R

/

d

τ

dR/d\\tau

dR/dτ不是在

τ

=

T

S

\\tau=T_S

τ=TS处消失,这种差异揭示了时序不匹配的幅度和符号。在附录一中提到,对于带宽受限于

f

S

/

2

f_S/2

fS/2的信号,自相关导数不能在

τ

=

T

S

\\tau=T_S

τ=TS处为零。前面的分析表明,两个通道之间的时序失配可以通过执行四个操作来获得:1)延迟

x

1

x_1

x1和

x

2

x_2

x2

T

S

~T_S

TS秒;2)分别从

x

2

x_2

x2