51单片机并行接口P0~P3

Posted 学工科的皮皮志^_^

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了51单片机并行接口P0~P3相关的知识,希望对你有一定的参考价值。

前言

学习51单片机,IO口可以说是重中之重,在应用设计中应该理解,计算机内部是由数字电路组成的,只存在TTL电平,高电平3.5V~5V和低电平0V对应数字1和0,外设的状态输入要通过电路转换成高低电平,计算机才能识别。根据外设的需要的电平输出1或0,这就是程序控制外设的核心。

根据外设的需要的电平输出1或0,这就是程序控制外设的核心。

一、并行接口P0

① 并口与数据存储器统一编址,作为数据存储器的特殊功能寄存器来访问,寄存器名分别为:P0、P1、P2、P3;

② P0、P1、P2、P3各对应8位双向I/O口,每个端口可以按字节输入或输出,也可以按位进行输入或输出,四个口共32根口线,用作位控制十分方便;

③ P0、P1、P2、P3均可作准双向I/O口用,同时在单片机扩展外部存储器时,P0口还可作低8位地址和数据总线,P2口还可作高8位地址总线,P3口还具有第二特殊功能;

④ P0、P1、P2、P3均由锁存器、输出驱动电路和输入缓冲器组成,P0口能带8个TTL电路;P1、P2、P3口负载能力为4个TTL电路。

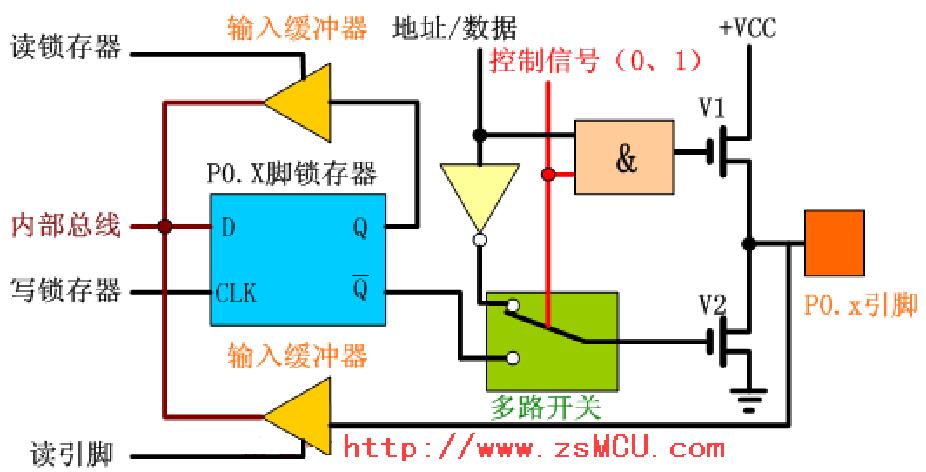

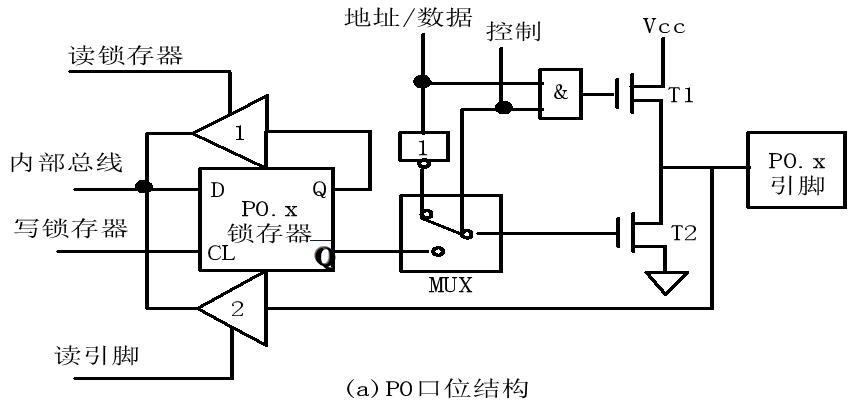

(1)P0口

P0口的字节地址为80H,位地址为80H~87H。

P0口是漏极开路的准双向口或做为低8位地址/数据总线口

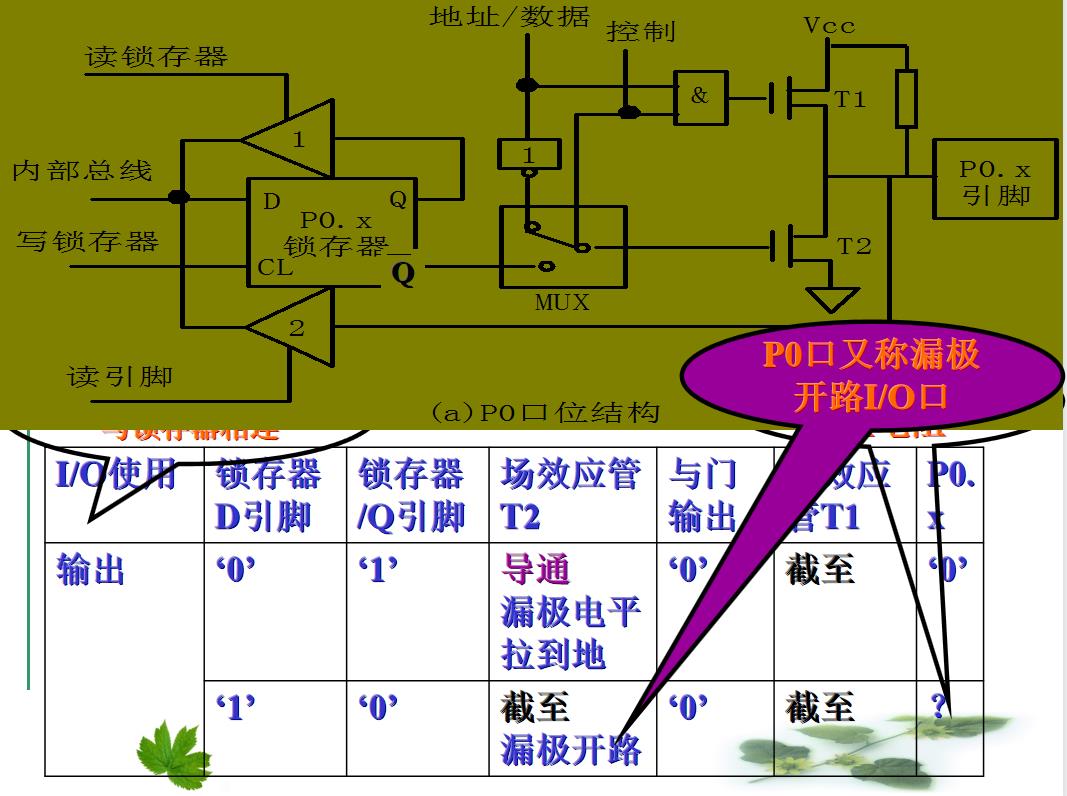

P0口作为地址/数据总线

P0口用于低8位地址/数据复用总线时,可用于扩展外部程序存储器和外部数据存储器。

1. 输出地址和数据时,控制线=1,MUX与地址和数据总线相连,锁存器和引脚断开,锁存器的值不影响引脚电平;

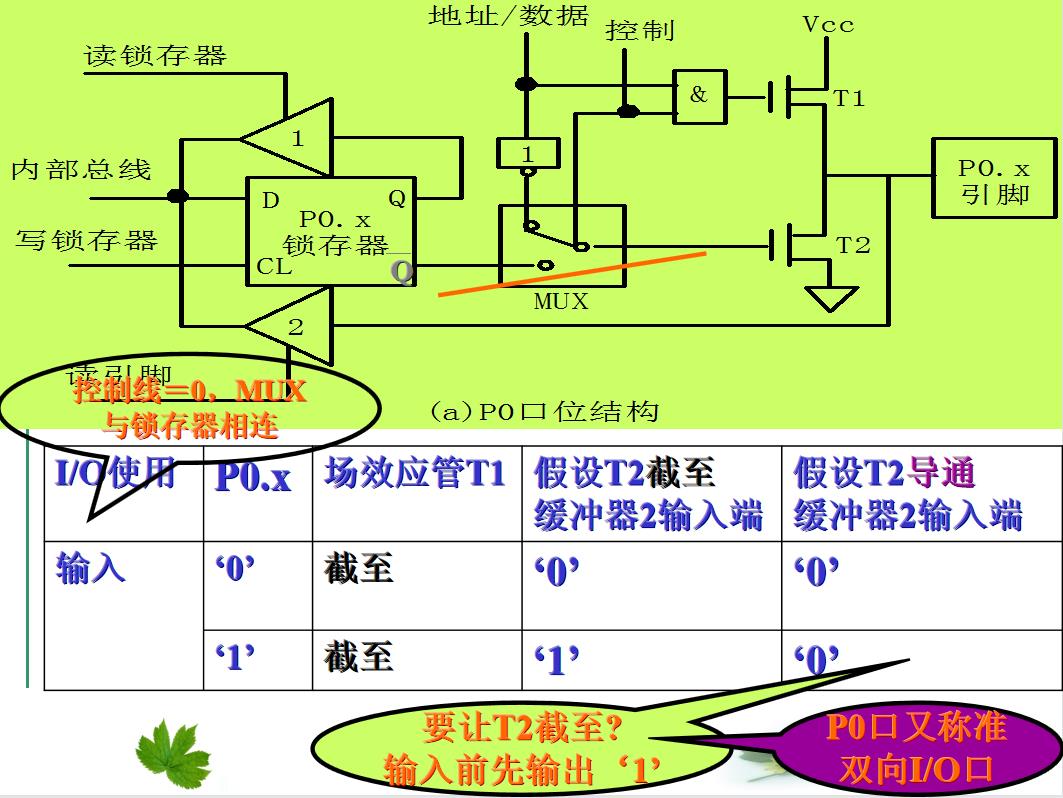

2. 输入数据时,控制线=0,MUX与锁存器相连,此时CPU将自动向P0口输出0FFH,T1和T2均关断,输出驱动电路由于处于高阻状态,不影响输入。

(2)、P0口作为通用I/O口

注意:对P0口操作时,写P0口时写锁存器和写引脚是一致的,其实质都是写锁存器;但在读P0口时,读锁存器和读引脚就不一样了,因为锁存器和引脚的值有时是不同的。

读引脚操作称读引脚指令 例:MOV A,P0

读锁存器操作称读-修改-写指令 例:ANL P0,A

(注:以上同适合P1、P2、P3口)

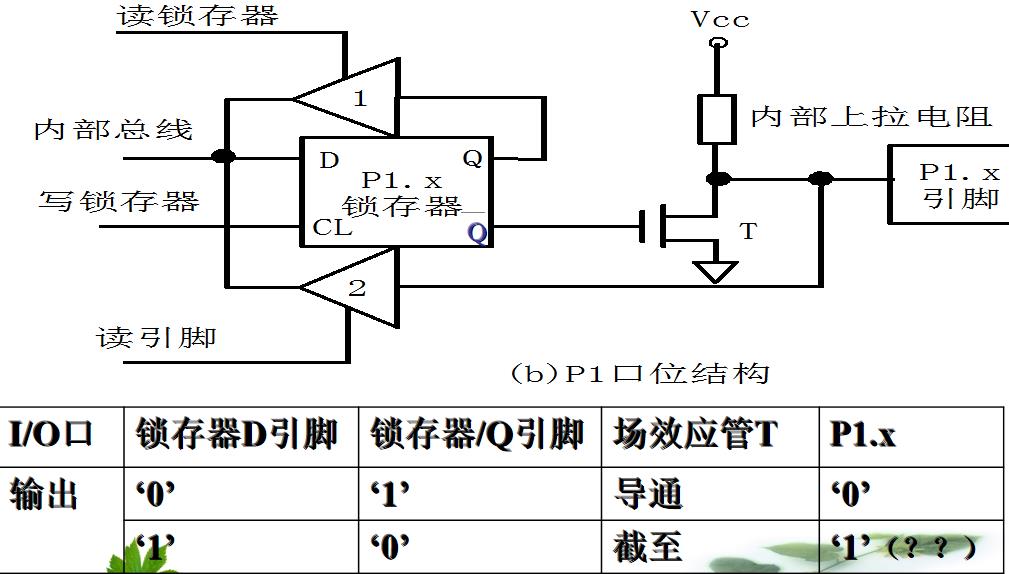

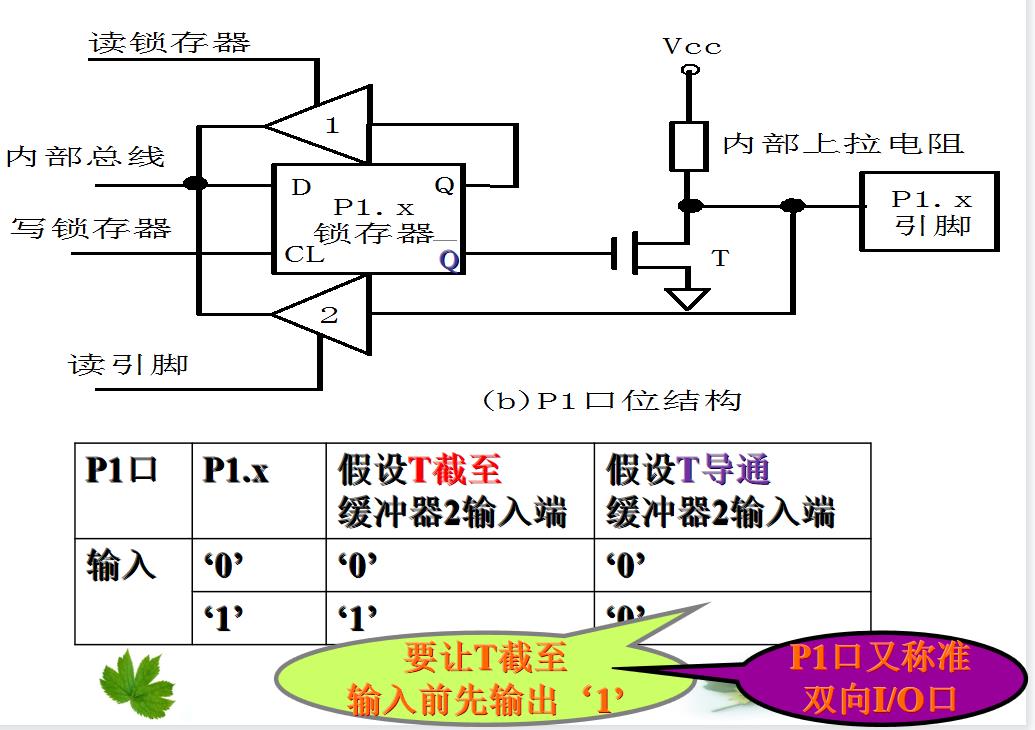

二、并行接口P1

P1口的字节地址为90H,位地址为90H~97H。

P1口是带上拉电阻的8位准双向I/O口

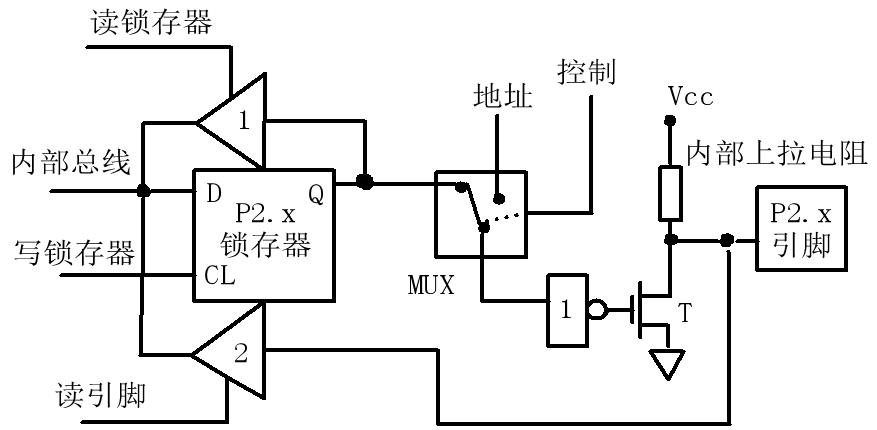

三、并行接口P2

P2口的字节地址为A0H,位地址为A0H~A7H。

1、P2口用于高8位地址总线时,可用于扩展外部程序存储器和外部数据存储器。 输出地址时,MUX与地址总线相连,锁存器和引脚断开,锁存器的值不影响引脚电平。

2、当P2口做通用I/O口时,多路开关MUX接锁存器;内部有上拉电阻。

用于输出:输出1时,引脚为高电平,输出0时,引脚为低电平;

用于输入:由于输入时T不能影响输入,故T必须截止,因此作输入时,要人为的将P2的锁存器置1(所以称为准双向I/O口)

应当注意:当P2口的几位作地址线使用时,剩下的P2口线不能作I/O口线使用。

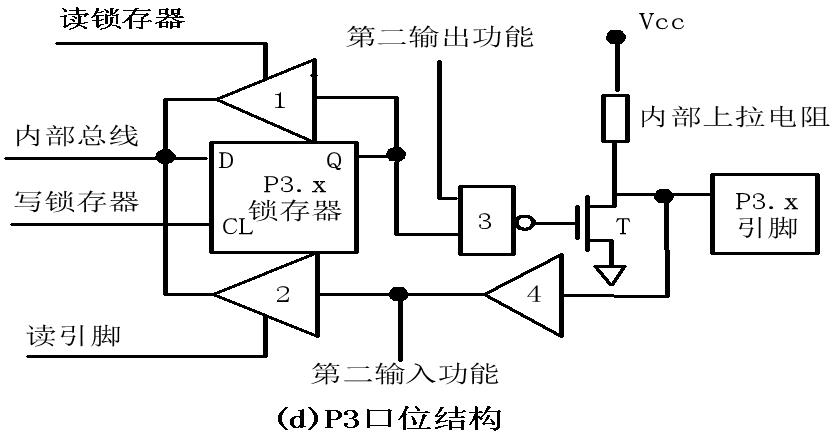

四、并行接口P3

P3口的第二特殊功能引脚分配:

P3.0-(10脚)RXD:串行数据接收端

P3.1-(11脚)TXD:串行数据发送端

P3.2-(12脚)INT0:外部中断0请求端,低电平有效

P3.3-(13脚)INT1:外部中断1请求端,低电平有效

P3.4-(14脚)T0:定时计数器0外部时钟输入端

P3.5-(15脚)T1:定时计数器1外部时钟输入端

P3.6-(16脚)WR:外部数据存储器写选通信号,低电平有效

P3.7-(17脚)RD:外部数据存储器读选通信号,低电平有效

归纳四个并行口使用的注意事项如下:

1.如果单片机内部有程序存贮器,不需要扩展外部存贮器和I/O接口,单片机的四组口均可做I/O口用。

2.四组口在做输入口使用时,均应先对其写“1”,以避免误读。

3.P0口做I/O口使用时应外接10K的上拉电阻,其它口则可不必。

4.P2可某几根线作地址使用时,剩下的线不能作I/O口线使用。

5.P3口的某些口线作第二功能时,剩下的口线可以单独作I/O口线使用。

以上是关于51单片机并行接口P0~P3的主要内容,如果未能解决你的问题,请参考以下文章