单片机原理(AT89S51)|最新更新5.23

Posted Eric%258436

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了单片机原理(AT89S51)|最新更新5.23相关的知识,希望对你有一定的参考价值。

本章讲述主要是MCS-51单片机(支持国产STC,拒绝卡脖子)

简单、容易上手,很多人推荐新手学习,所以整理了此学习文档。但是我本人是不太建议大家去学习的,建议初入门的高中生暑假没啥事干,或者感兴趣的初中生玩。毕竟总是要走到stm32那条路的,直接上,一样学!感兴趣的可以看我的stm32的博客(超链接附上):本人stm32博客

如果想了解硬件,可以看我另一个博客,20件硬件工程师必知必会的基础元器件(超链接附上):本人基础元器件博客

什么是单片机:半导体硅片集成:中央处理单元(CPU)、存储器(ARM、ROM)、并行I/O、串行I/O、定时器/计数器,中断系统、系统时钟电路及系统总线的用于控制目的的控制器。具有微机的属性(运行程序),因而被称为单片微型计算机,简称单片机。体积小,成本低。(最近贵了起来2021.5.22,啧啧啧)

主要用于测控领域。通常是处于测控系统的核心地位并嵌入其中,国际上称嵌入式控制器(EMCU),或微控制器(MCU)。我国习惯称“单片机”。是计算机技术发展史上的一个重要里程碑,标志计算机正式形成了通用计算机系统和嵌入式计算机系统两大分支。

发展历程及应用领域不再赘述,可看单片机原理的慕课。

与C51的区别:最直接的一点下载采用SPI

硬件结构

单片机的软硬件结合非常强,在实际开发中,如果只懂单独的一部分,很难做到很好的开发效果。这不同于软件开发的前后端分离,由于硬件的架构不同,所带来的对程序的优化就不一样,这种细节的大体量的繁琐细碎的知识,决定了硬件工程师的学习培养周期非常长,没有程序员所谓的35岁中年危机,其实程序员也没有中年危机,国外大龄码农比比皆是,只是国内起步晚。

本节行文逻辑:

硬件结构

引脚功能

存储器结构

特殊功能寄存器功能

4个并行I/O口的结构和特点

复位电路和时钟电路设计

节电工作模式

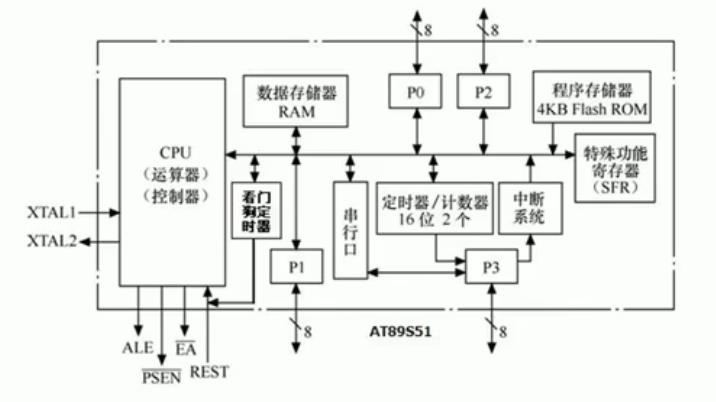

硬件结构图:把控制应用所必须的基本功能部件都集成在一个电路芯片上。

51单片机功能部件

1)八位微处理器(CPU):包括运算器和控制器两部分,还有位处理功能

2)数据存储器(RAM):128B,最大可扩64KB,片内RAM为高速RAM,可加快速度和降低功耗

3)程序存储器(ROM):4KB Flash,如不够,片外可外扩至64KB

4)4个八位并行I/O口(P1\\P2\\P3\\P0口):四个八位并行I/O口

5)1个全双工异步串口:四种工作方式。可进行串行通信,扩展并行I/O口,可与多个单片机构成多机系统

6)2个16位定时器/计数器(52系统有3个,4种工作方式)

7)1个看们狗定时器(WDT):当CPU由于干扰使程序陷入死循环或跑飞时,WDT可使程序恢复正常运行

8)中断系统:5个中断源,1个中断向量(5个中断源,2级中断优先权)

9)特殊功能寄存器(SFR)26个:对片内个功能部件管理、控制和监视。是各功能部件的控制寄存器和状态寄存器,映射在片内RAM区80H~FFH内。

10)低功耗的空闲模式和掉电模式

11)3个程序加密位

引脚功能

采用40只引脚双列直插,如图所示

按照功能分类

电源及时钟引脚

电源引脚

(1)Vcc(40P):+5V电源。

(2)Vss(20P):数字地。

时钟引脚

(1)XTAL1(19P):输入端。使用片内振荡器时,应接外部石英晶体和微调电容。外接时钟源时,该脚接外部时钟晶振器的信号

(2)XTAL2(18P):片内振荡器反相放大器的输出端

使用片内振荡器:该脚连接外部石英晶体和微调电容。

当使用外部时钟源时,脚悬空控制引脚

(1):RST(RESET,9脚):复位信号输入,加持续时间大于2个及其周期的高电平,可使单片机复位。正常工作应≤0.5V。当看门狗定时器溢出输出时,该脚将输出长达96个时钟振荡周期的高电平

(2):EA`/VPP(Enable Address/Voltage Pulse of Programing,31脚)

EA`

第一个功能:允许访问外部程序存储器控制。

a.EA`=1

PC值≤0FFFH时,单片机读片内4kb Flash中的程序。

PC值≥0FFFH时(超出片内4KB Flash地址范围时),转向读取片外60kb(1000H~FFFFH)程序存储器空间的程序

b.EA`=0

只读取外部程序存储器中内容,读取地址范围0000H~FFFFH,片内4kb Flash无效

Vpp

第二功能:对片内Flash 编程,接编程电压

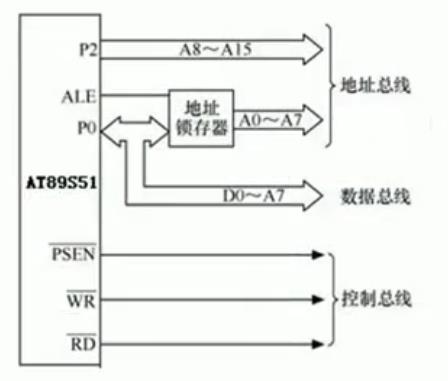

(3):ALE/PROG`(Address Latch Enable/PROGramming,30脚)

ALE:第一功能

为访问外部存储器提供低8位地址锁存信号,将低8位地址锁存在片外地址锁存器中。

原理如下图

单片机运行时,ALE端一直有正脉冲信号输出,频率为时钟的Fosc的1/6。每当AT89S51访问外部RAM时(执行MOVX类指令),要丢失一个ALE脉冲。如需要,可将特殊功能寄存器AUXR(地址为8EH)的第0位(ALE禁止位)置1,来禁止ALE操作,但访问外部程序存储器或外部数据存储器指令“MOVC”或“MOVX”时,ALE仍然有效。即ALE禁止位不影响对外部存储器的访问。

PROG`:第二功能,对片内Flash 编程的编程脉冲输入

PSEN`(Program Strobe ENable,29脚):片外程序存储器读选通信号,低有效。并行I/O口引脚

(1)P0口:8位,漏极开路的双向I/O口

可作为系统总线低8位地址总线及数据总线分时复用端口,也可做普通I/O口,需加上拉电阻,可驱动8个LS型TTL负载

(2)P1口:8位,准双向I/O口,具有内部上拉电阻

准双向I/O口,作为I/O输入时,应先向端口锁存器写1。可以驱动4个LS型TTL负载。

P1.5/MOSI、P1.6/MISO、P1.7/SCK 可对片内FLash存储器串行编程和校验,分别是串行数据输入、输出和位移脉冲引脚

(3)P2口:8位,准双向I/O口,具有内部上拉电阻。

当外扩存储器及I/O口时,P2口输出高八位地址。

P2口也可作为通用I/O使用。当作输入时,应先向端口输出锁存器写1。可以驱动4个LS型TTL负载

(4)P3口:8位,准双向I/O口,具有内部上拉电阻。

可作为通用的I/O口使用。作为通用I/O输入,应先向端口输出锁存器写入1。可以驱动4个LS型TTL负载

P3口还可提供第二功能,定义如图

综上所述:P0口可作为总线口,为双向口。作为通用I/O使用时,为准双向口,这是需要加上拉电阻。P1,P2,P3均为准双向口。

双向口与准双向口的区别。

准双向口仅有两个状态。而P0口作为总线使用,口线内无上拉电阻,处于高阻“悬浮”态,故P0口为双向三态I/O口。

为什么P0口要有高阻“悬浮态”,而准双向I/O则无高阻的“悬浮状态”?

P0直接与cpu相连,不交互数据的时候,需要隔离起来,防止错误数据读入PS:准双向口作为I/O输入,要向该口先写“1”。

熟记40引脚每一功能,硬件电路设计十分重要

下期更新 AT89S51单片机硬件结构后续内容

以上是关于单片机原理(AT89S51)|最新更新5.23的主要内容,如果未能解决你的问题,请参考以下文章