Simulink HDL Coder FPGA初级开发实践FFT以及CORDIC算法进行信号相位校正

Posted 肆拾伍

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Simulink HDL Coder FPGA初级开发实践FFT以及CORDIC算法进行信号相位校正相关的知识,希望对你有一定的参考价值。

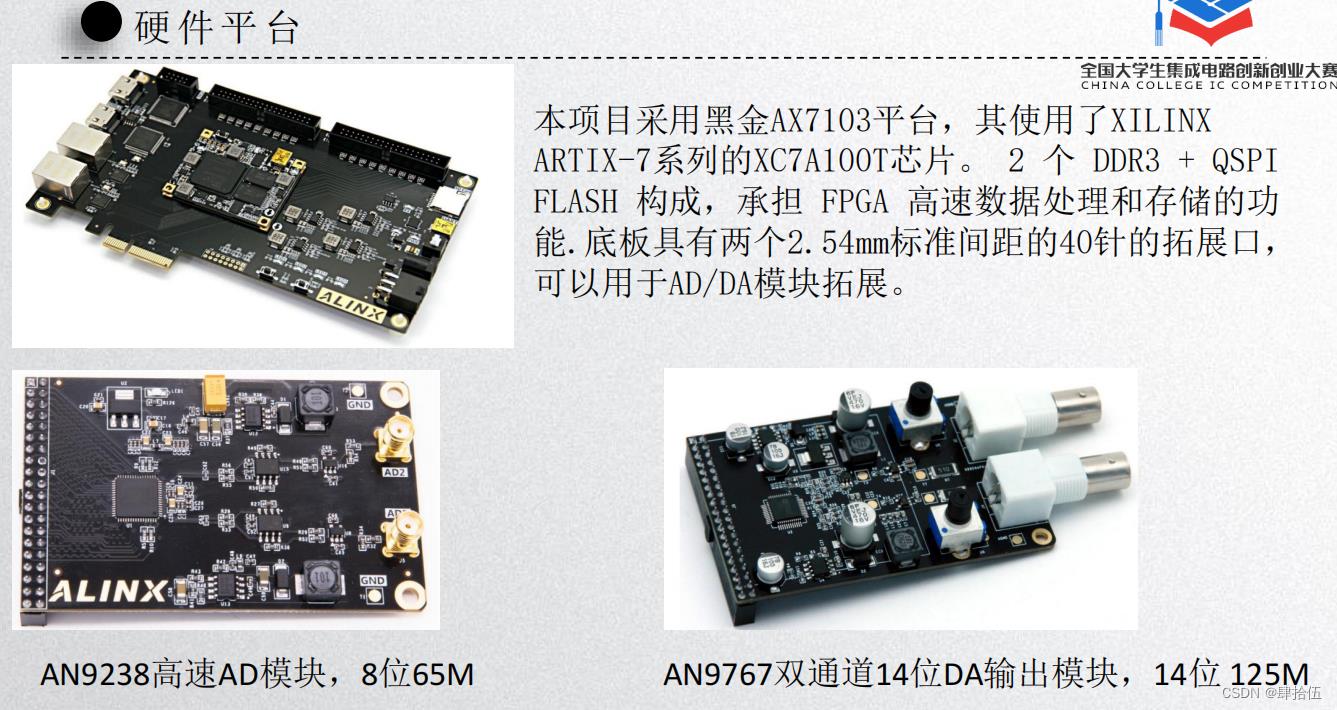

前言: 本栏目除特别说明以外,均采用的黑金AX7103开发板,该开发板时钟频率为200M,并且是双端时钟,因此在每个项目中都有一段原语将双端时钟变成200MHz的单端时钟。文章仅作为学习记录,如有不足请在评论区指出,博主不会对各位的问题作出解答,请谅解。博主深知网络上关于HDL Coder的资料十分稀少,特别是中文资料几乎没有,并且官方给出的例子大多挺难不适合入门,因此将自己摸索的过程记录下来,希望给后人一些启发。

文章目录

1. 项目背景

- 本项目是2022年全国大学生集成电路创业创新航天微电子杯的赛题,由于自己时间精力有限,所以特意尝试了一下全部用Simulink完成项目设计,最后发现结果还是很不错的,整个模型2天就搭好并通过测试仿真。相对于初赛花了2周来学习各种ip核的使用,然后手工来写Testbench,Simulink能够节省大量时间。

- 赛题要求如下图:

由于疫情影响,我是拿自己手上的AX7103板卡进行实验的,决赛才会发板子。所以没有用到射频部分,同时GTH以及DDR3都不能在Simulink里面模拟仿真。 算法原理可以简单描述为:

- AD采样信号分为两路,一路传入数据处理模块,一路传入数据储存模块(可以是RAM也可以是DDR3)。

- 数据处理模块计算两路输入AD信号的相位差,首先FFT找到频谱幅度最大值对应的索引以及实部和虚部。比较两路信号在该频点上的相位差,相位计算可以通过Atan2函数,该函数使用CORDIC硬件加速算法。得到相位差之后计算采样点偏移,即应该偏移多少个采样点才能将两路AD信号信号对齐,相位对应的其实就是时间平移量,找到这个偏移量输出给数据储存模块。

- RAM通过读取和写入的地址偏差控制AD信号的输出,将两路信号对齐。算法流程可以描述为下图:

当然,相位差校正还有不少其他的方法,比如相关法,滤波法等等。

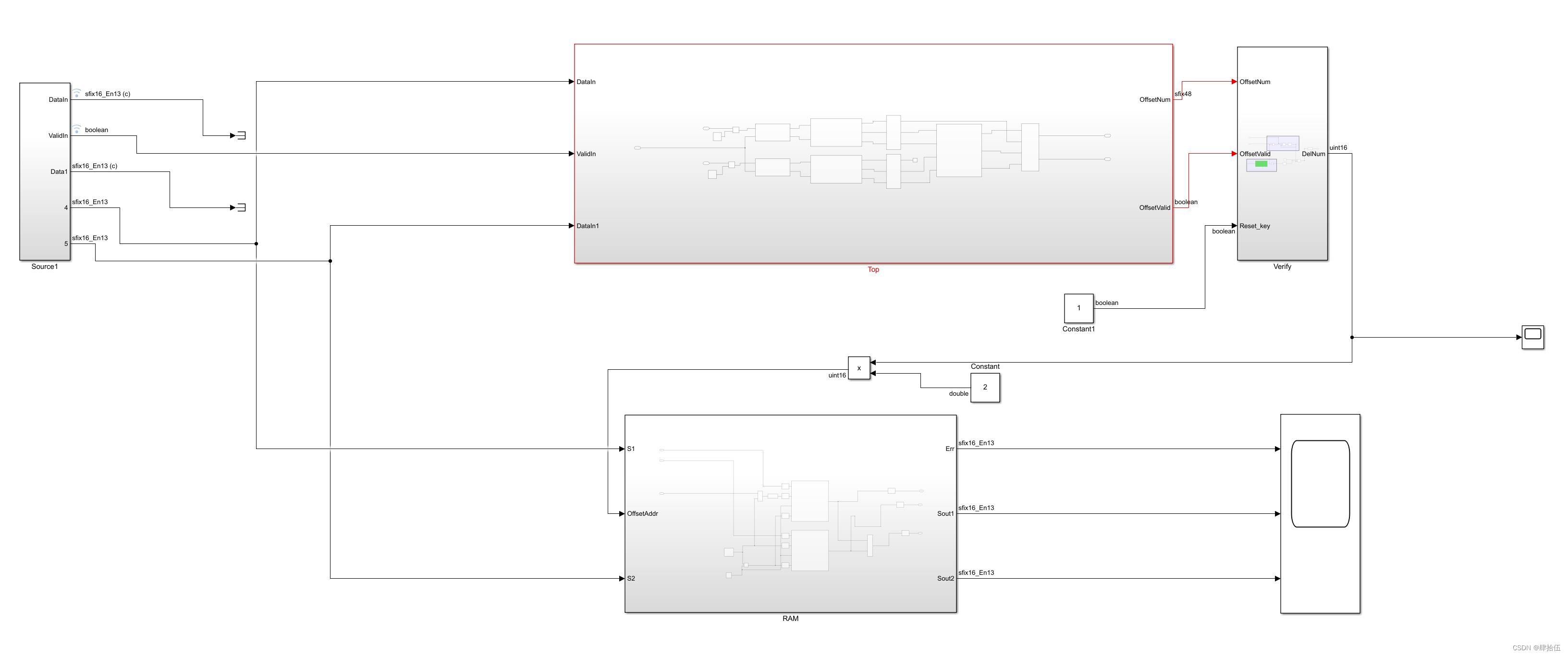

2. Simulink模型

我这里解释一下为什么后面偏移量我乘了一个系数2,这里是因为给Top模块的有效信号周期为2,但是Simulink本身的时钟周期是1,也就是说,如果你查看外部的输入信号是 1 1 2 2 3 3 4 4,Top收到的信号实际是1 2 3 4,你查看信号波形就明白了。

我找不到最初的模型了,一共写了很多版的代码,这个是比较早的版本,我觉得要清晰一些。

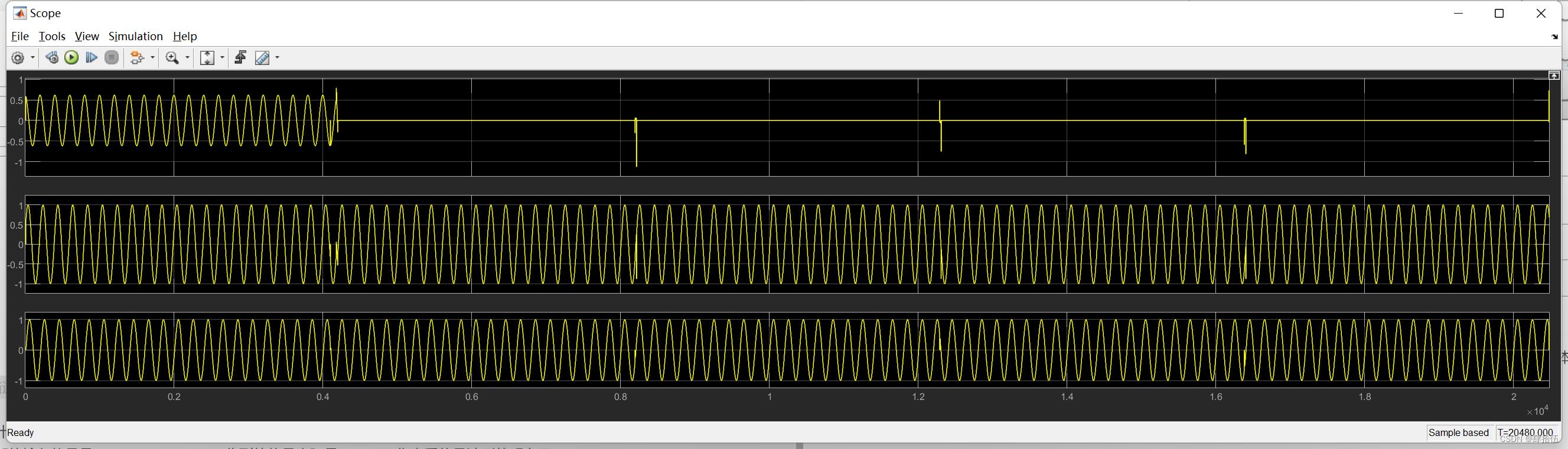

这是仿真结果。

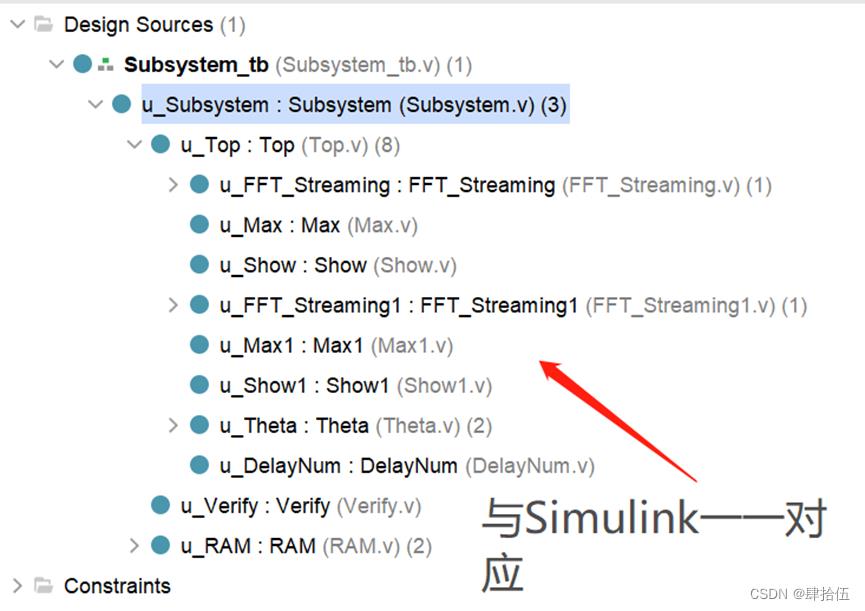

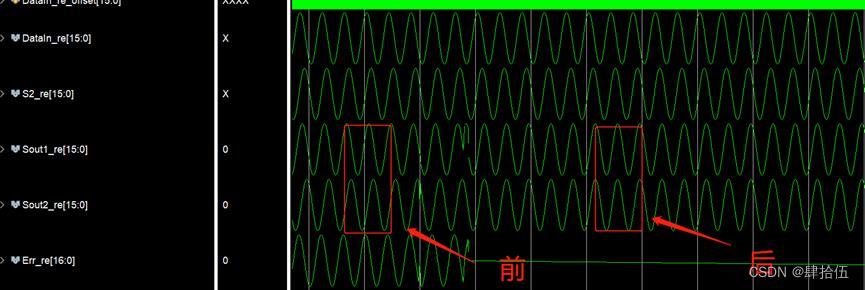

3. Vivado 仿真

我生成HDL 代码的时候是一个模块一个模块的生成单独测试的,不像之前的时候都是封装成一个顶层模块。也就是每次点 的时候,都要选中要生成的模块。或者你们再将里面所有的模块,除了信号源意外都再封装成一个子系统。

的时候,都要选中要生成的模块。或者你们再将里面所有的模块,除了信号源意外都再封装成一个子系统。

上面的仿真是直接生成TestBench的仿真结果,可以看到是可以实现功能的。不过对应的Simulink文件可能被我删掉了,我找不到了。

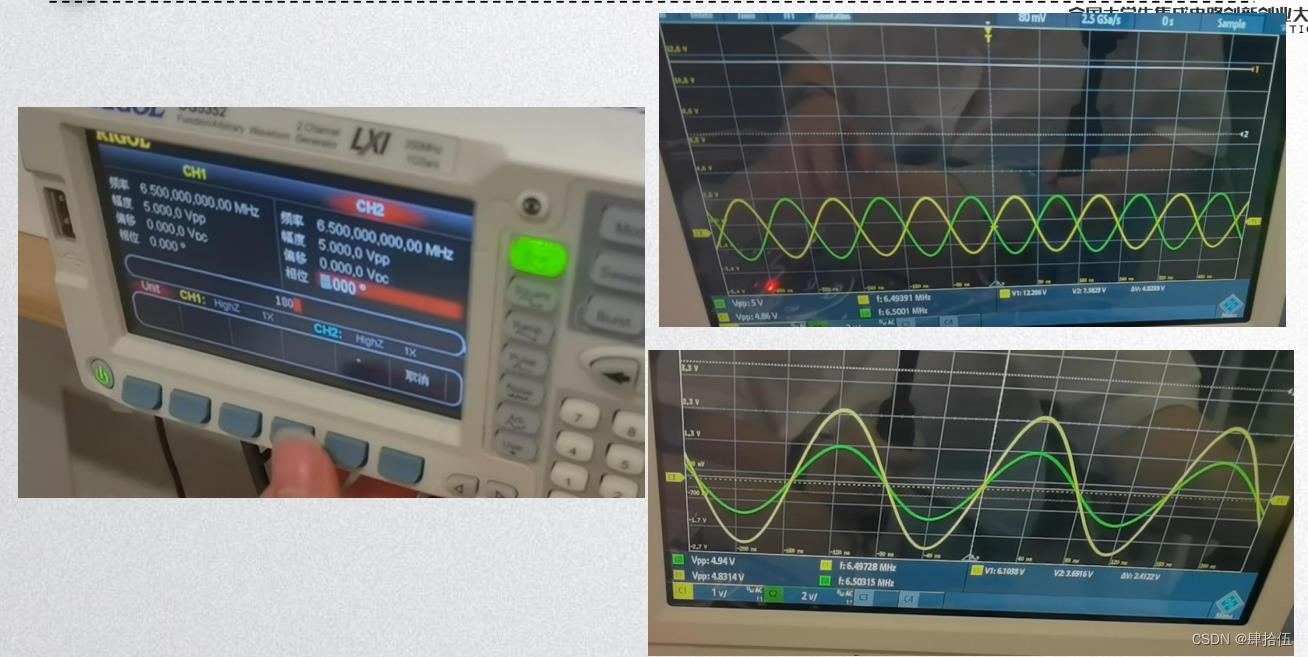

4. 实际效果

5. 文件下载

我给出一份可以直接使用的模型,以及对应的Vivado工程,没有Vivado测试文件,直接可以下载到AX7103的,管脚都已经配好了。 用了AD/DA模块:

我想应该没人会上板测试,两个模块都插到拓展口上,具体位置可以看看约束文件,我忘了,大概是AD J11,DA J13. 不知道有没有加按键功能,如果没有校正效果,看看按板卡上的两个按键有没有效果。

主要是让大家下载之后看看Simulinlk模型,我有点懒,讲的不太清楚,有问题再问吧。等下次看看会不会弄一个比较详细的新工程。

链接:https://pan.baidu.com/s/1_4m0sWSaNs_5eRDs2489wA?pwd=1111

提取码:1111

–来自百度网盘超级会员V6的分享

以上是关于Simulink HDL Coder FPGA初级开发实践FFT以及CORDIC算法进行信号相位校正的主要内容,如果未能解决你的问题,请参考以下文章