计算机基础学习笔记:操作系统篇之硬件结构,存储层次结构

Posted adventure.Li

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机基础学习笔记:操作系统篇之硬件结构,存储层次结构相关的知识,希望对你有一定的参考价值。

二、存储器的层次结构

本文知识来源小林Coding阅读整理思考,原文链接请见该篇文章

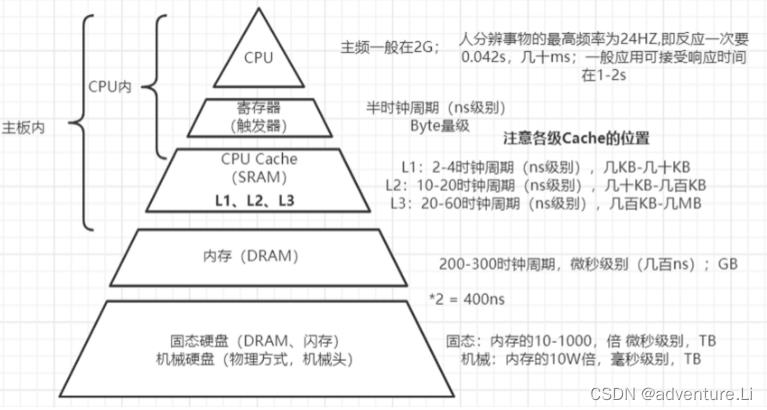

存储层次

- 寄存器

- 高速缓存,Cache 1-3级

- 内存

- 磁盘(SSD,HDD)

关键点

- 各层次的存储的 介质、速度、容量 以及工作层次

- 理解CPU Cache的作用,三级缓存的位置

- 结合软件开发中的性能需求–响应时间,调优工作(追求高性能,很大程度上则体现在响应速度)

- 结合CPU的指令执行周期去理解读取指令过程的时间开销

寄存器

速度:n秒级别,容量:byte级别;

组成:由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。

寄存器的访问速度非常快,一般要求在半个 CPU 时钟周期内完成读写,CPU 时钟周期跟 CPU 主频息息相关,比如 2 GHz 主频的 CPU,那么它的时钟周期就是 1/2G,也就是 0.5ns(纳秒)。

CPU 处理一条指令的时候,除了读写寄存器,还需要解码指令、控制指令执行和计算。【寄存器的访问速度至关重要】

CPU Cache

速度:ns级别,容量:KB 至MB间

组成:缓存基本上都是采用SRAM存储器,SRAM是英文Static RAM的缩写,它是一种具有静态存取功能的存储器,不需要刷新电路即能保存它内部存储的数据。不像DRAM内存那样需要刷新电路,每隔一段时间,固定要对DRAM刷新充电一次,否则内部的数据即会消失。

在 SRAM 里面,一个 bit 的数据,通常需要 6 个晶体管。

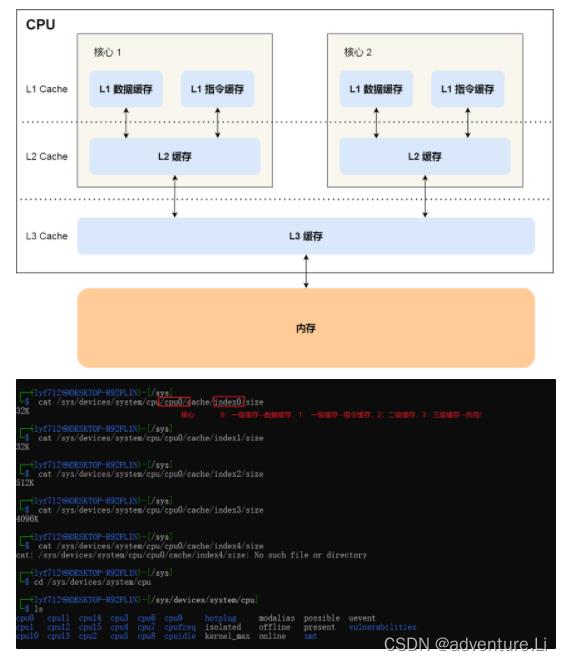

注意Cache的层次划分!下图重要!【多个竞争,共用则设计并发控制处理,后续的缓存一致性问题】

L1缓存

速度:2-4个时钟周期;容量:几十KB到几百KB。

L1 高速缓存的访问速度几乎和寄存器一样快,通常只需要 2-4个时钟周期,而大小在几十 KB 到几百 KB 不等。

L2缓存

速度:10-20个时钟周期;容量:几百KB至MB。

L3缓存

访问速度相对也比较慢一些,访问速度在 20-60个时钟周期,容量:几 MB 到几十 MB 不等

内存

速度:内存速度大概在 200~300个 时钟周期【0._ms】之间 ,容量:GB

采用DRAM存储。

DRAM 存储一个 bit 数据,只需要一个晶体管和一个电容就能存储,但是因为数据会被存储在电容里,电容会不断漏电,所以需要「定时刷新」电容,才能保证数据不会被丢失,这就是 DRAM 之所以被称为「动态」存储器的原因,只有不断刷新,数据才能被存储起来。

硬盘

内存的读写速度比 SSD 大概快10-1000倍【us级别】,是机械硬盘的10 0000倍【ms级别了】左右。

固态硬盘(Solid State Disk或Solid State Drive,简称SSD),又称固态驱动器,是用固态电子存储芯片阵列制成的硬盘。

固态硬盘的存储介质分为两种:

机械硬盘即是传统普通硬盘,主要由:盘片,磁头,盘片转轴及控制电机,磁头控制器,数据转换器,接口,缓存等几个部分组成。

磁头可沿盘片的半径方向运动,加上盘片每分钟几千转的高速旋转,磁头就可以定位在盘片的指定位置上进行数据的读写操作。信息通过离磁性表面很近的磁头,由电磁流来改变极性方式被电磁流写到磁盘上,信息可以通过相反的方式读取。硬盘作为精密设备,尘埃是其大敌,所以进入硬盘的空气必须过滤。

以上是关于计算机基础学习笔记:操作系统篇之硬件结构,存储层次结构的主要内容,如果未能解决你的问题,请参考以下文章

计算机基础学习笔记:操作系统篇之硬件结构,CPU的基本工作原理

小林Coding阅读笔记:操作系统篇之硬件结构,CPU Cache一致性问题