基于FPGA的高速数据采集系统实现

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA的高速数据采集系统实现相关的知识,希望对你有一定的参考价值。

欢迎订阅《FPGA学习入门100例教程》、《MATLAB学习入门100例教程》

目录

一、理论基础

高速数据采集在军用民用领域都有着广泛的应用。高速数据采集系统在自动控制、电气测量、地质物探、航空航天等工程实践中有着极为广泛的应用。如何对高速的信号进行实时采集、实时存储,保证信号不丢失,以满足工业现场的需要,一直是高速数据采集系统研究的一个重要方向。数据采集系统是信号与信息处理系统中不可缺少的重要组成部分,同时也是软件无线电系统中的核心模块。

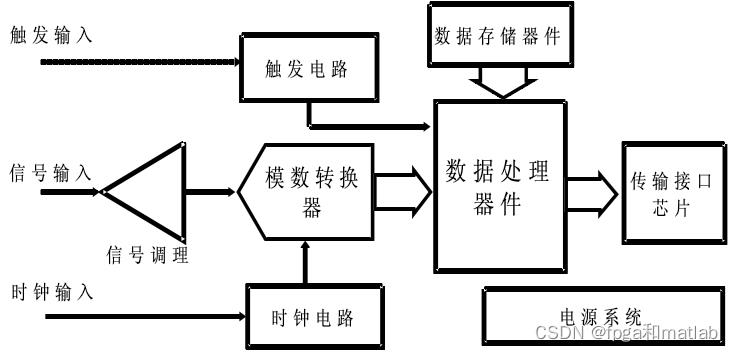

高速数据采集系统主要包括以下几个部分:模拟信号调理电路、模数转换器、数据处理器件、数据存储器件、时钟电路、触发电路、传输接口芯片和电源系统等,如图1所示。

图1 高速数据采集系统结构图

其中,模拟信号调理电路是用来将模拟信号放大调整到ADC的采样量程之内,这样既能充分发挥ADC的性能,又能保证采样数据的完整性;ADC是高速数据采集系统的核心器件,模拟信号输入,数字信号输出;数据处理器件有很多种,可以根据实际的不同需要进行选择;数据存储器件主要用于存储数据,可以进行显示,回放和数据处理等操作;时钟电路是比较重要的,时钟的稳定性和精确性决定着数据采集的结果,所以一般的做法是单独设计稳定的时钟电路;触发电路实现外部对数据采集频率和次数的控制,传输接口用于将数据传输给计算机进行后处理。

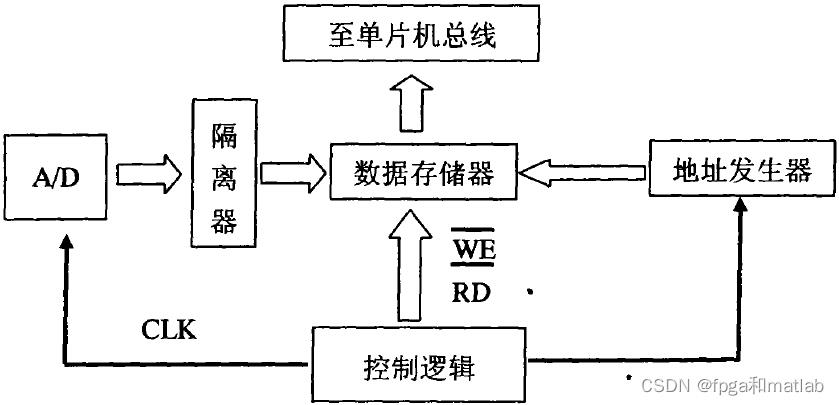

采用单路高速A/D转换器以及存储器构成串行采集系统系统框图如图2所示:

图2 单路高速数据采集框图

采用单路高速AD转换器和高速存储电路来构成字串行采集系统,系统的采样就属于实时采样,适用于任何形式的信号波形,重复的或不重复的,单次的或连续的。又由于所有采样点是以时间为顺序,因而易于实现波形显示功能。但是采用单片高速A/D芯片和高速存储器件,会大大提高系统开发成本。同时系统的采样率就受到A/D转换器最高转换速率以及存储器写入速度的限制。因此,单通道数据采集系统的采集速度受器件自身参数的限制,很难再大幅度提高其转换速度。

二、核心程序

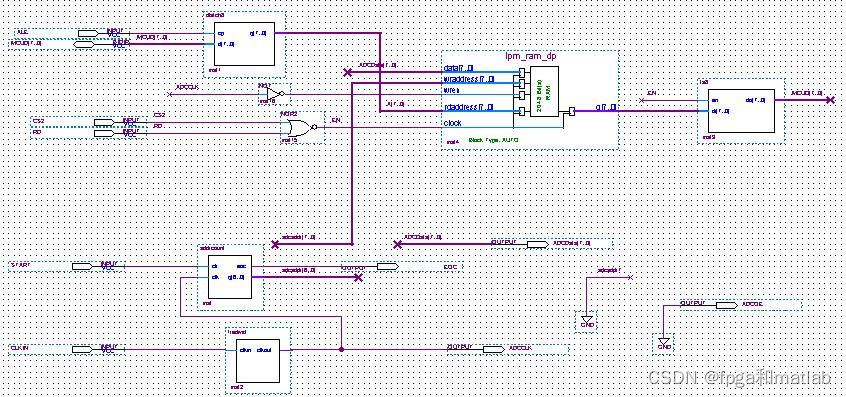

其整体结构如下所示:

2.1锁存器模块

系统工作的时候要对数据进行锁存,然后进行传输,通常这样做可以使系统更加稳定的工作,其工作原理比较简单,实现代码如下所示:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity dlatch8 is

port(

cp: in std_logic;

d: in std_logic_vector(7 downto 0);

q: out std_logic_vector(7 downto 0)

);

end dlatch8;

architecture one of dlatch8 is

begin

process(cp,d)

begin

if(cp='1') then

q<=d;

end if;

end process;

end;2.2双口地址计数器模块

地址计数器用来给RAM存储器产生地址信号。由RAM的写入时钟来控制,每当时钟上升沿到来一次,地址计数器就自动加1,直到进行至RAM的底部,表示此时RAM已经写满。下面给出由VHDL语言实现的地址计数器部分源代码。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity addrcount is

port(

clr:in std_logic;

clk:in std_logic;

eoc: out std_logic;

q: buffer std_logic_vector(6 downto 0)

);

end;

architecture beha of addrcount is

begin

process(clr,clk)

begin

if(clk'event and clk='1') then

if clr='0'then

q<="0000000";

elsif(q="1111111")then

q<="1111111";

else

q<=q+1;

end if;

end if;

end process;

process(q)

begin

if(q="1111111") then

eoc<='0';

else

eoc<='1';

end if;

end process;

end beha;2.3双口RAM模块

对于高速数据接收,一般发送端和接收端的时钟是异步的,这就涉及到异步时钟域数据的传输的问题,此外在不同时钟控制的时钟域中传递数据时,了避免发生亚稳态和产生毛刺,应该做好异步时钟域之间的隔离处理。通常,可采用DPRAM以数据缓冲的形式来作为异步时钟域之间的隔离接口。

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY altera_mf;

USE altera_mf.all;

ENTITY lpm_ram_dp IS

PORT

(

clock : IN STD_LOGIC ;

data : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

rdaddress : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

wraddress : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

wren : IN STD_LOGIC := '1';

q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

END lpm_ram_dp;

ARCHITECTURE SYN OF lpm_ram_dp IS

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DOWNTO 0);

COMPONENT altsyncram

GENERIC (

address_aclr_a : STRING;

address_aclr_b : STRING;

address_reg_b : STRING;

indata_aclr_a : STRING;

intended_device_family : STRING;

lpm_type : STRING;

numwords_a : NATURAL;

numwords_b : NATURAL;

operation_mode : STRING;

outdata_aclr_b : STRING;

outdata_reg_b : STRING;

power_up_uninitialized : STRING;

read_during_write_mode_mixed_ports : STRING;

widthad_a : NATURAL;

widthad_b : NATURAL;

width_a : NATURAL;

width_b : NATURAL;

width_byteena_a : NATURAL;

wrcontrol_aclr_a : STRING

);

PORT (

wren_a : IN STD_LOGIC ;

clock0 : IN STD_LOGIC ;

address_a : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

address_b : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

q_b : OUT STD_LOGIC_VECTOR (7 DOWNTO 0);

data_a : IN STD_LOGIC_VECTOR (7 DOWNTO 0)

);

END COMPONENT;

BEGIN

q <= sub_wire0(7 DOWNTO 0);

altsyncram_component : altsyncram

GENERIC MAP (

address_aclr_a => "NONE",

address_aclr_b => "NONE",

address_reg_b => "CLOCK0",

indata_aclr_a => "NONE",

intended_device_family => "Cyclone",

lpm_type => "altsyncram",

numwords_a => 256,

numwords_b => 256,

operation_mode => "DUAL_PORT",

outdata_aclr_b => "NONE",

outdata_reg_b => "CLOCK0",

power_up_uninitialized => "FALSE",

read_during_write_mode_mixed_ports => "DONT_CARE",

widthad_a => 8,

widthad_b => 8,

width_a => 8,

width_b => 8,

width_byteena_a => 1,

wrcontrol_aclr_a => "NONE"

)

PORT MAP (

wren_a => wren,

clock0 => clock,

address_a => wraddress,

address_b => rdaddress,

data_a => data,

q_b => sub_wire0 ); END SYN;

2.4时钟分频模块

一般在高速系统中,时钟的生产有两种方法实现,PLL锁相环法和计数器分频法。下面我们对两种方法做简单的介绍。

计数器分频器的设计比较简单,其主要通过计数器来控制时钟发现跳板的周期,这里我们对其工作原理就不做介绍了。本系统由于使用的分频器比较简单,因此在这个系统中,我们将实用计数器分频器来设计时钟。

其实现的VHDL代码如下所示:

LIBRARY IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fredivid is

port(

clkin:in std_logic;

clkout: out std_logic

);

end fredivid;

architecture one of fredivid is

signal q:std_logic_vector(1 downto 0);

begin

process(clkin)

begin

if(clkin'event and clkin='1')then

if(q="11")then

q<="00";

else

q<=q+1;

end if;

end if;

end process;

process(q)

begin

if(q(1)='1') then

clkout<='1';

else

clkout<='0';

end if;

end process; end;三、测试结果

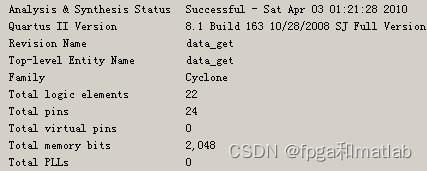

最后,对于设计完成的系统,我们得对其资源做分析。本系统其资源实用情况如所示:

图1 资源使用分析

本系统,我们共实用逻辑单元2048个。

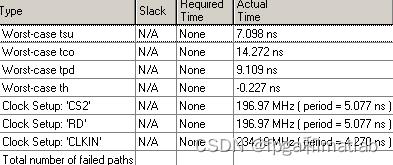

图2 时序分析报表

其中tsu,tco,tpd,th分别为7.098ns,14.272ns,9.109ns,0.227ns。后面的输入信号频率基本在200M左右,达到高速传输的要求。

A28-35

以上是关于基于FPGA的高速数据采集系统实现的主要内容,如果未能解决你的问题,请参考以下文章