实现FPGA Verilog HDL与NIOS II的通信数据交换——利用AVALON总线

Posted 蒲公英291

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了实现FPGA Verilog HDL与NIOS II的通信数据交换——利用AVALON总线相关的知识,希望对你有一定的参考价值。

平时用FPGA基本都是全程用Verilog HDL编程,当遇到液晶的时候,发现Verilog的还不如C语言来的方便,但是用Nios来编写的时候,实现NIOS与Verilog的通信又是一个问题,今天用了两种方法实现Verilog与NIOS通信的方法。

第一:利用AVALON总线,自定义IP核,将Verilog部分挂到AVALON总线,利用AVALON总线与NIOS通信,在NIOS中利用函数读取AVALON总线数据即可;

首先需要编写符合AVALON总线的要求的Verilog代码(xxx.v文件)。

1、添加信号

input sys_cs_n; //总线读片选,低电平有效

input sys_rd_n; //总线读使能信号,低电平有效

output[7:0] sys_rddata; //总线读取数据input sys_cs_n; //总线读片选,低电平有效

input sys_wr_n; //总线写使能信号,低电平有效

input[7:0] sys_wrdata; //总线写入数据以上是两组信号,至少需要添加一组。 第一组是读总线数据需要添加的信号,第二组是写入总线数据的信号。

数据宽度可以选择8位 16位 32位。

然后在Verilog代码中编写逻辑代码。

以下以数码管显示为例,将数码管模块写入AVALON总线,以下是数显显示模块的一个顶层文件。其它类似

module seg(

clk,rst_n,

row_scan_sig,

col_scan_sig,

sys_cs_n,

sys_wr_n,

sys_wrdata

);

input clk;

input rst_n;

output [7:0] row_scan_sig;

output [3:0] col_scan_sig;

input sys_cs_n; //总线读片选,低电平有效

input sys_wr_n; //总线写使能信号,低电平有效

input[15:0] sys_wrdata; //总线写入数据

reg [13:0] num;

wire wrcs_n = sys_cs_n | sys_wr_n;

//总线地址译码锁存

always @(posedge clk or negedge rst_n)

if(!rst_n) num <= 8'd0;

else if(!wrcs_n) num <= sys_wrdata;

seg_display U4(

.clk(clk),

.rst_n(rst_n),

.row_scan_sig(row_scan_sig),

.col_scan_sig(col_scan_sig),

.data(num)

);

endmodule

注意以下,是显示的数据是num变量,这个变量接受来自总线的数据sys_wrdata。当片选信号sys_cs_n与读使能信号sys_wr_n都有效的情况下,开始传数据给num。

以下是自定义IP核步骤:

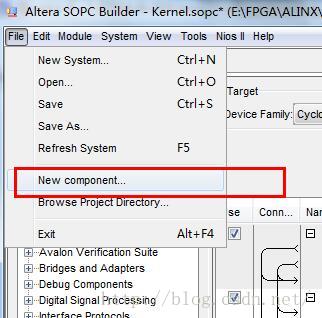

1、打开sopc

file——>now componnet

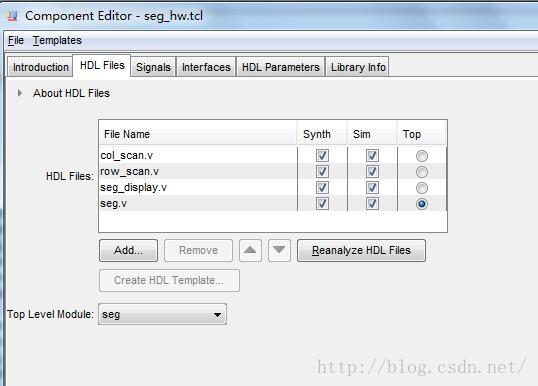

2、然后点击next 点击ADD 添加Verilog文件,选择顶层文件。系统会自动编译

3、signal一栏 这一栏比较重要。

系统的信号需要选择为avalon_slave_0,时钟是clock ,复位要选择reset,输出信号需要选择conduit_end singnal Type一栏也要选择对用的信号类型。next

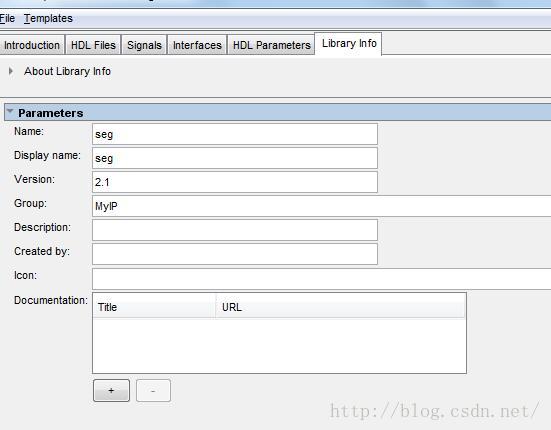

4、设置个人信号,IP名字,版本信息,看个人了

完成一个自定义IP核的设计。

在NIOS中需要调用使用一下语句。

IOWR(SEG_0_BASE, 0, data);

以上是关于实现FPGA Verilog HDL与NIOS II的通信数据交换——利用AVALON总线的主要内容,如果未能解决你的问题,请参考以下文章