[架构之路-56]:目标系统 - 平台软件 - 总体架构概述

Posted 文火冰糖的硅基工坊

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了[架构之路-56]:目标系统 - 平台软件 - 总体架构概述相关的知识,希望对你有一定的参考价值。

目录

前言:

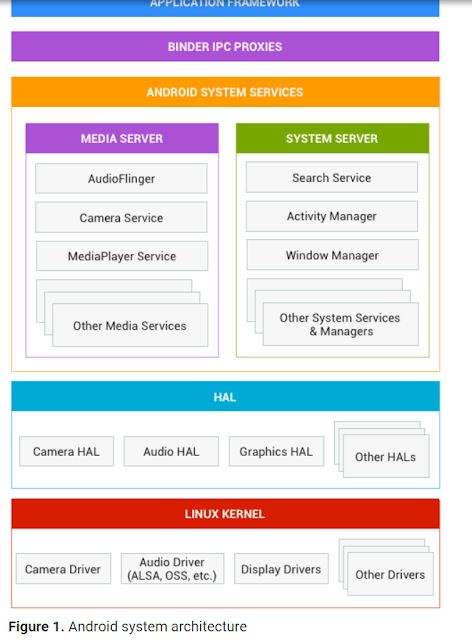

在嵌入式系统中,硬件驱动分为内核驱动和用户空间驱动。内核驱动以ko的形式存在,用户空间驱动以so的方式存在。它们都完成了对嵌入式系统中的硬件外设的访问,包括硬件的配置、状态监控、数据的接收和发送。

其中内核驱动负责,硬件与业务无关基本功能的配置、中断、逻辑地址到物理地址的映射、把硬件设备挂接到Linux内核的各种驱动程序框架中,使得用户空间的驱动程序能够通过Linux标准的文件系统接口可以访问硬件,我各个把它归属在Linux内核一部分。这部分,在前面的文章中已经探讨过。

用户空间驱动:负责对硬件设备与业务相关的功能配置(主要通过配置芯片的寄存器来实现)、与业务相关功能状态的监控、在用户空间数据的收发、以及为应用软件提供硬件抽象层的接口(HAL:硬件抽象层接口)。以便于应用软件不需要关注具体硬件的型号、硬件寄存器的定义等硬件相关的细节。为应用程序使用嵌入式系统的各种硬件服务提供便利。

中间件层:负责对Linux OS和libc库提供的CPU计算相关的服务进行封装,为应用程序使用嵌入式系统的各种软件服务提供便利。

第1章 嵌入式硬件架构案例

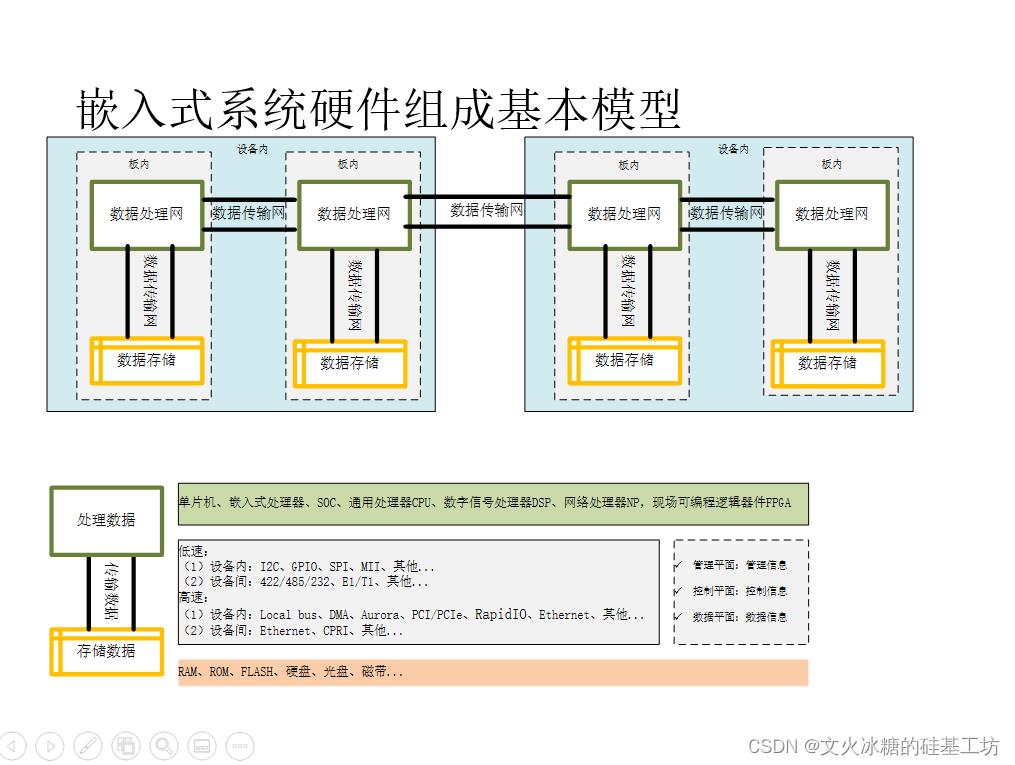

1.1 通用的嵌入式硬件架构

[架构之路-20]:目标系统 - 硬件平台 - 嵌入式系统硬件电路基础:架构、设计流程、总线、外设、基本电路、编码_文火冰糖的硅基工坊的博客-CSDN博客_系统硬件架构设计

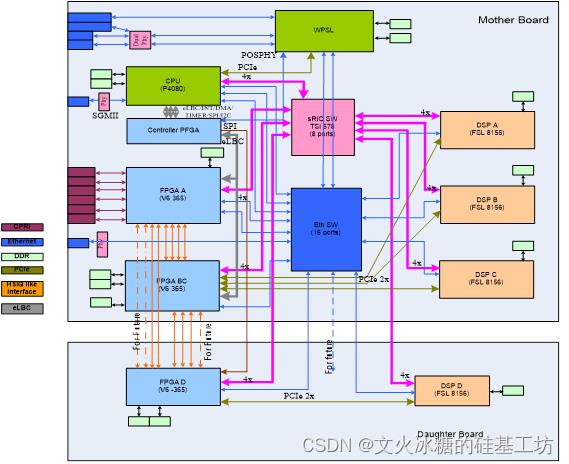

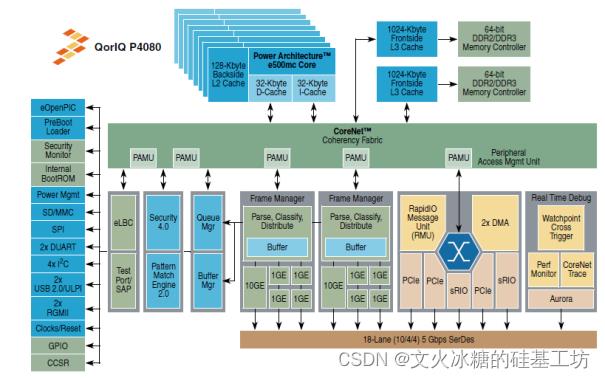

1.2 基站设备硬件架构示例

上图是一个单板基站的硬件架构示意图,实际的宏基站系统比这个要复杂很多,这里仅仅示例

(1)主板

- (1)CPU (P4080) :高性能主控CPU芯片,运行Linux操作系统、硬件抽象层软件HAL(本文探讨的重点)、中间件软件、TCP/IP网络应用层协议(TCP/IP协议栈在Linux操作系统中)、应用软件(基站OAM管理软件、RRU OAM管理软件、基站空口L2/L3软件等)

- (2)DSP_A/B/C:基站空口L2/L3软件等

- (3)RapidIO Switch:一种板内高速互联总线(远程内存访问的高速总线)

- (4)Ethernet Switch:以太网高速互联总线(使用二层以太网帧通信)

- (5)Controller FPGA:硬件启动相关电路、时钟同步相关电路、电源管理相关电路等硬件通用逻辑控制。

- (6)FPGA_A :BBU与RRU之间高速互联通道CPRI协议链路控制器。

- (7)FPGA_BC:BBU主控板与基带板之间高速互联通道HSIQ协议链路控制器。

- (8)WPSL:基站后传接口高速数据网络加速器(包括IPSec的加解密)

- (9)PHY:以太网PHY芯片,提供多个1G的RF45或SFP以太网接口。

- (10)其他电路:I2C设备温度监控设备、I2C SFP设备、UART、GPS receiver等等.....

(2)扩展卡

- (1)FPGA_D:基带扩展子卡之间的HSIQ协议链路控制器。

- (2)DSP_D:基站空口L1软件。

备注:

(1)CPU SOC芯片:其内部的外设控制器的驱动,芯片厂家已经提供相关的SDK。

(2)其他的硬件:FPGAx功能/CPRI控制器/以太网Swtich/RapidIO Switch/I2C设备、GPS receiver等,都需要用户空间驱动程序驱动这些设备,应用程序(OAM、L2/L3)业务软件监控这些设备提供硬件无关的接口。这部分软件就是本文探讨的重点:硬件抽象层软件HAL。

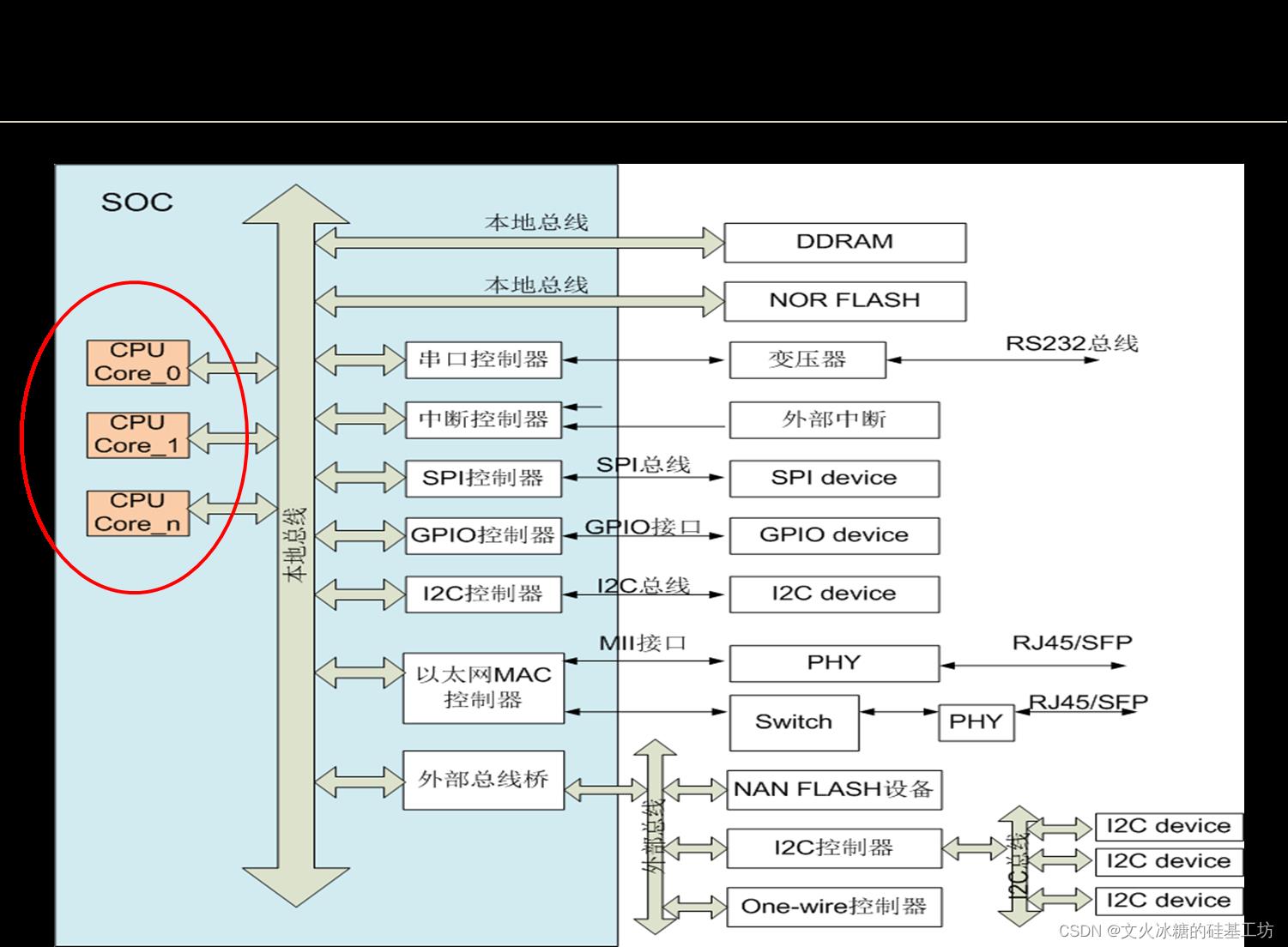

1.3 嵌入式SOC通用架构

现代的SOC, 不仅仅集成多个ARM CPU Core,还会集成多个DSP的核、特有业务应用领域所需要的各种加速器(如加密、编码、图像处理等)。

1.4 SOC芯片案例

P4080多核处理器是飞思卡尔新QorIQ产品线的标志性成员,基于45纳米处理技术。它集成了增强的Power Architecture™内核、三级缓存分层、创新CoreNet™片上结构和数据路径加速,可在最大30W的功率电路内提供卓著性能。

P4080 SoC内置八个增强型Power Architecture® e500mc内核,目标直指1.5 GHz 的最高频率。每个内核都有其自己的专用128KB L2后端缓存,并能够接入2MB共享前端L3缓存。完全的处理器独立性(包括启动和重置各单个e500mc内核的能力)是该器件最显著的特征。内核可以作为八个对称多处理(SMP)内核、八个完全不对称多处理(AMP)内核,或者它们也可以SMP和AMP组的组合且以不同程度的独立性进行运行。此外,内核还能够运行不同操作系统(OS)或者在无OS情况下运行,为用户提供了在控制、数据路径和应用处理间进行分区的极大灵活性。

整体性能通过数据路径加速架构(DPAA)得以增强,而DPAA同时又提供高联网性能,降低软件复杂性。该加速架构与内核一起,管理分组路由、安全、服务质量和深度分组检测,让内核把注意力集中到增值服务和应用处理上来。由于消除了其他多核方法中常见的一些与共享总线/共享存储器架构有关的总线争夺、瓶颈和延迟问题,CoreNet结构因此也提高了性能。

参考:

备注:

P4080内部控制器的驱动程序由飞思卡尔提供,作为嵌入式设备常见,不需要太多的关注如何实现SOC芯片内部控制器的驱动,设备厂家更多的是关注SOC外部的FPGA的驱动,因为FPGA内部的功能逻辑,是设备厂家私有的功能,设备厂家的硬件驱动程序也主要关注这些硬件设备 。

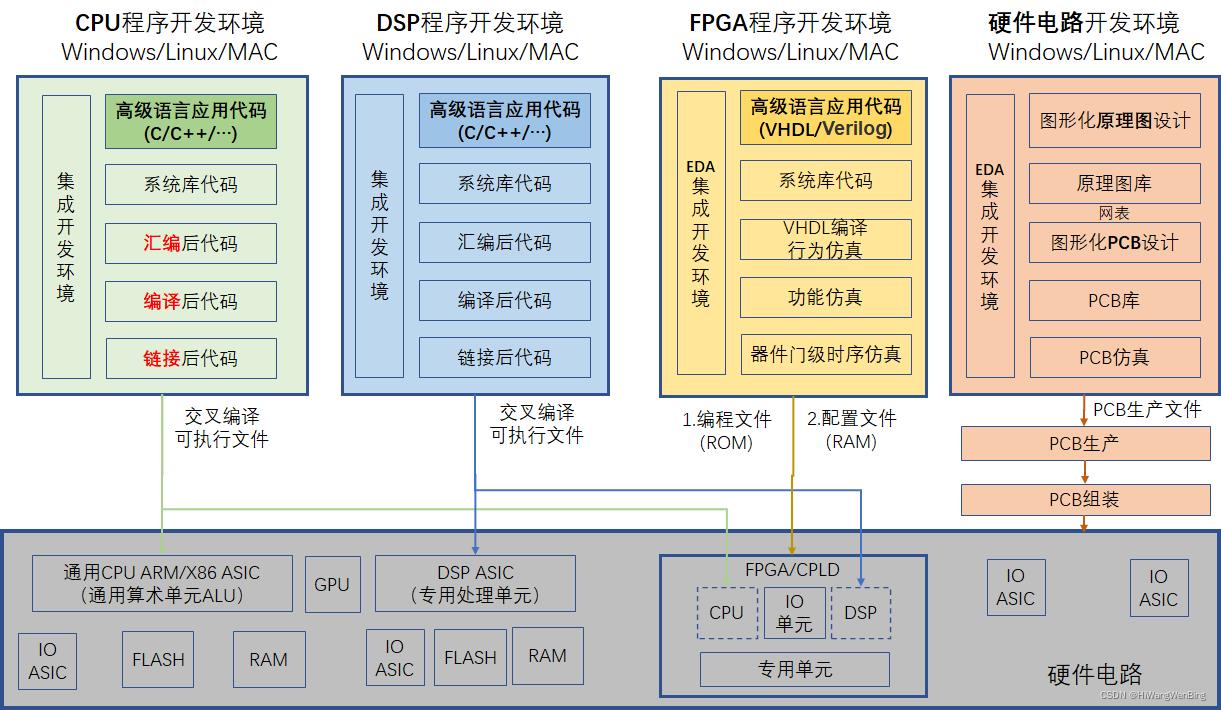

第2章 嵌入式软件总体架构

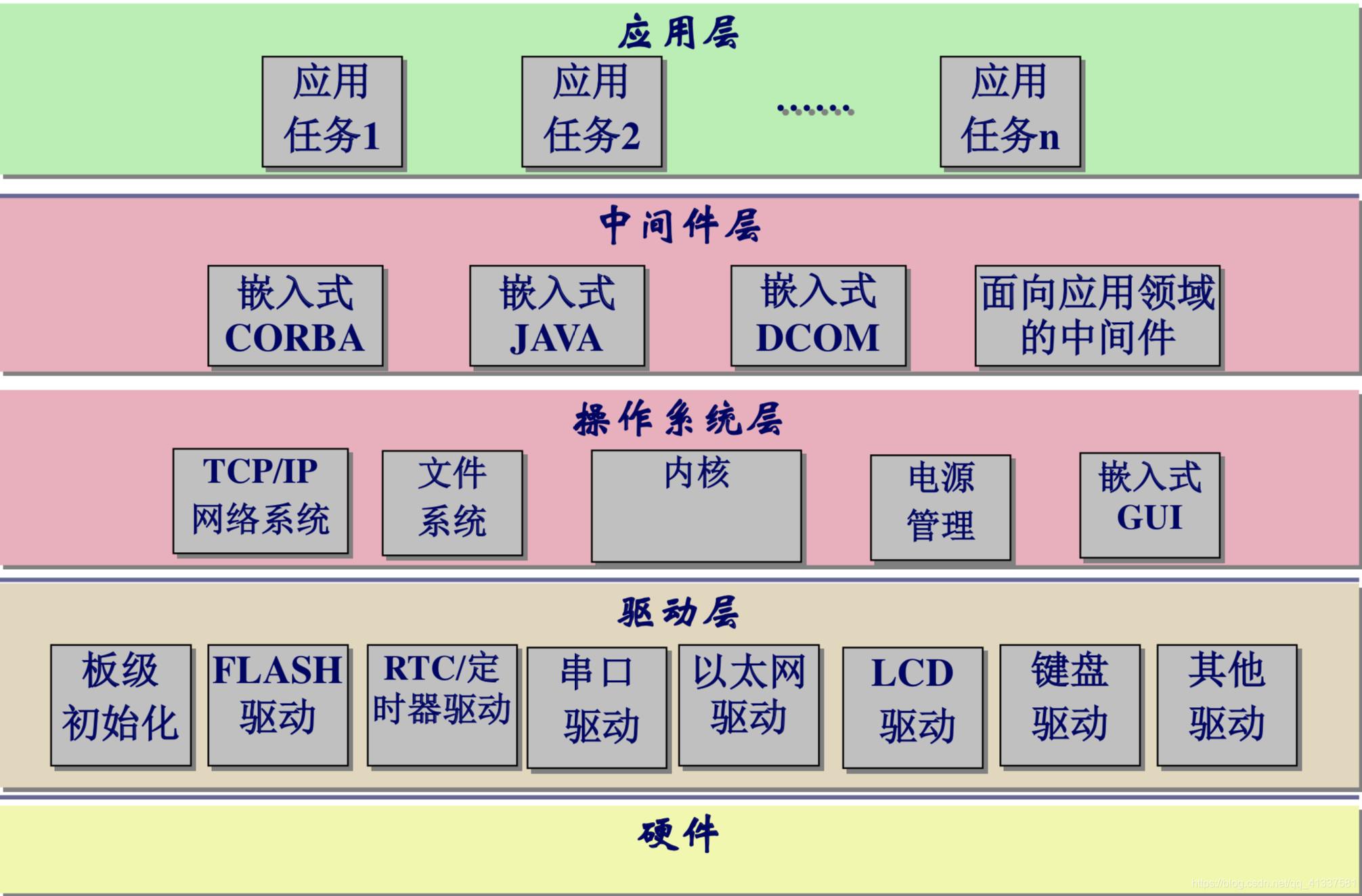

2.1 嵌入式软件的开发框架

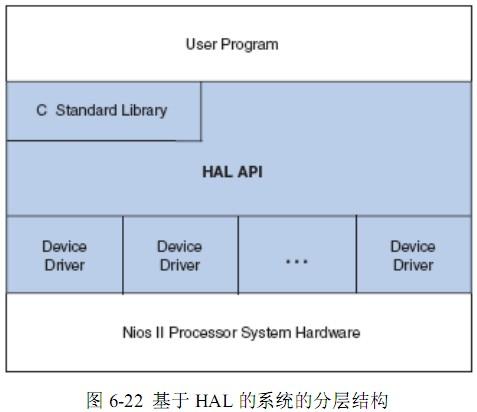

2.2 嵌入式软件的通用架构之硬件抽象层

这里的硬件抽象层是指位于操作系统内核与应用程序之间的接口层,其目的在于将硬件抽象化。

(这里的硬件抽象层与Linux内核的硬件抽象层不是一回事)

中间件与硬件抽象层的目的都是为上层的应用程序提供一个通用的接口。

中间件:为应用层软件屏蔽操作系统各种服务或库(如定时器、signal、消息队列、进程间通信等)接口,避免应用软件直接调用C或C++的标准库接口或线程库接口或其他库接口。

硬件抽象层:屏蔽的硬件寄存器细节,避免应用软件要了解硬件寄存器的细节,为应用程序提供访问硬件寄存器的通用接口,其主要特征包括:

- 为应用程序访问硬件提供了通用的与硬件无关的接口

- 硬件的用户空间驱动(业务相关的驱动实现:so代码)

- 调用标准的Linux文件系统接口访问内核空间的驱动(挂载Linux内核驱动框架:ko代码)

2.3 嵌入式软件的通用架构之中间件层

中间件是介于应用系统和系统软件之间的一类软件,它使用系统软件所提供的基础服务(功能),衔接网络上应用系统的各个部分或不同的应用,能够达到资源共享、功能共享的目的。它并没有很严格的定义,但是普遍接受IDC的定义:中间件是一种独立的系统软件服务程序,分布式应用软件借助这种中间件软件在不同的技术之间共享资源,中间件位于客户机服务器的操作系统之上,管理计算的计算资源和网络通信。从这个意义上可以用一个等式来表示中间件:中间件=OS服务 + 通信服务,这也就限定了只有用于分布式系统中才能叫中间件,同时也把它与支撑软件和实用软件区分开来。

备注:

广义上讲:硬件外设的用户空间的驱动程序抽象层HAL也是中间件的一部分,它为应用程序访问计算机或嵌入式系统的硬件外设提供了用户空间的接口。

狭义上讲:HAL可以从中间件中剥离出来,成为相对独立的一部分。这是因为这部分主要与硬件外设相关,需要有硬件电路的技术背景和硬件所实现的业务知识,而传统的中间件(包括操作系统平台和网络平台),是纯计算机领域的技能。

第3章 基站平台软件架构

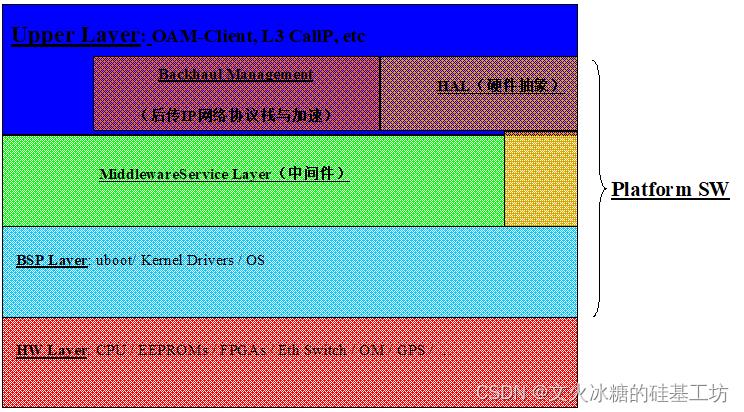

3.1 基站平台软件架构

(1)最底层为硬件层

(2)中间是uboot和Linux OS内核

(3)再向上就是中间件

(4)硬件抽象层可以与中间件并列,也可以调用中间件提供的服务。

(5)后传TCP/IP网络协议栈,又称为传输层transport协议栈。

3.2 平台软件的主要功能

(1)Linux内核

(2)RootFS

(3)内核或操作系统线程:如initd、sshd、dhcpd、syslogd、launcher、schedtd、lecmon。

(4)平台中间件:如消息队列、定时器、内存分配、进程、线程。

(5)平台硬件抽象和用户空间驱动。

(6)后传(backhual)TCP/IP网络协议栈

备注:

Linux内核与文件系统,在前文中已经探讨过。

后续重点探讨:硬件驱动与中间件。

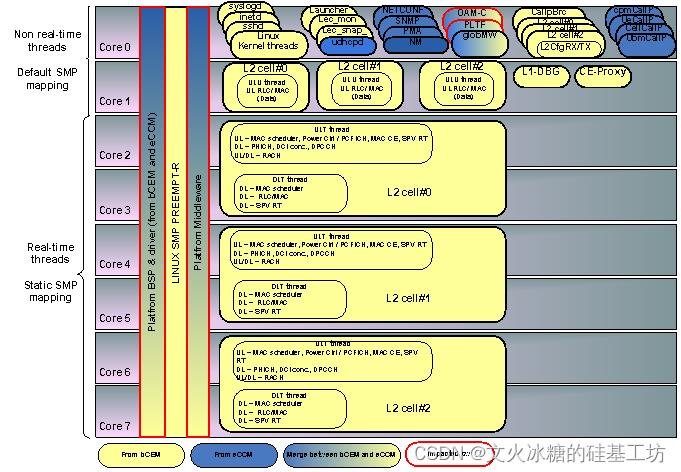

3.3 基站软件功能模块部署

从上图可以看出:

(1)Core0

- Linux内核的主要线程

- Linux的守护进程

- DHCP服务(为RRU分配IP地址)

- 中间件

- HRAL

- L3/CallP

- L2 Cell

(2)Core1

- L2 RLC/MAC

(3)Core2&3

- Core2:小区0的L2 上行调度MAC PS、上行随机接入、下行控制信道等

- Core3:小区0的L2 下行调度MAC PS、下行RLC/MAC、下行实时

(4)Core4&5

- Core4:小区1的L2 上行调度MAC PS、上行随机接入、下行控制信道等

- Core5:小区1的L2 上行调度MAC PS、下行RLC/MAC、下行实时

(5)Core6&7

- Core6:小区2的L2 上行调度MAC PS、上行随机接入、下行控制信道等

- Core7:小区2的L2 上行调度MAC PS、下行RLC/MAC、下行实时

备注:

- 空口协议栈MAC/RRL/PDCP/RRC都属于应用程序。

- 空口协议栈L1由DSP承担

- RRU和BBU, BBU内部模块之间通过CPRI连接,由CPRI/HSIQ FPGA承担。

- 平台软件负责在不同的CPU核上加载不同的应用程序。

3.4 存储器分区

在嵌入式系统中,通常三种存储设备:

(1)Boot Flash

- boot0/1:存放uboot,支持uboot主从备份

- others:存放uboot环境变量、存放网络MAC地址

(2)USB Flash

- fs0、fs1:Linux Kernel(支持主从备份)、Rootfs(支持主从备份)

- scd:安全加密存储空间,存放ssh keys, passwd files

- store:存放动态生成的log,掉电保存。

- data:存放软件的版本信息和配置参数信息(主从分区共享)

(3)RAM

- rmem:非易失性RAM, 用于存放crash上下文、Coredump文件、重启原因等,确保系统重启前的信息得以及时保存(使用Flash存放,速度不够)

- rdata:存放软件所需要的默认配置参数(主从分区共享)

- tmp:临时空间

- pmfs:其他用途

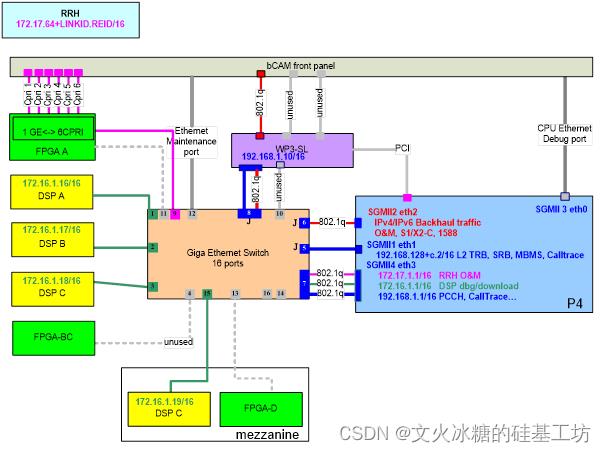

3.5 板内以太网络

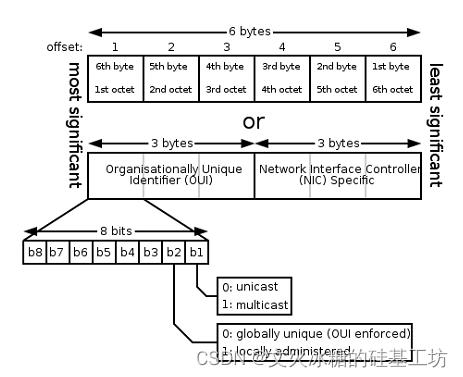

(1)内部MAC地址

每个以太网接口,都需要设定一个MAC地址,该MAC地址是厂家特有的,确保MAC地址是唯一的,否则多个设备放在一个局域网内组网,会导致MAC地址冲突。

基站内部大量的接口都需要MAC地址:FPGA-x、DSP_x、SOC_x等。

(2)内部VLAN

VLAN的目的是隔离板内没有相互通信需求的Traffic。

VLAN设置可能会影响两个节点:

- 交换机配置

- Linux的以太网interface(带vlan id)

(3)内部IP地址

- 用于设备内板间通信(FPGA、SOC、DSP)

- 用于SOC内部不同接口的通信

- 用于本地调试

- RRU与BBU之间的接口地址

(4)外部IP地址

- 后传接口:管理面、数据面、控制面、同步面可以共享相同的地址,也可以使用不同的地址。

以上是关于[架构之路-56]:目标系统 - 平台软件 - 总体架构概述的主要内容,如果未能解决你的问题,请参考以下文章