计算机四级嵌入式知识点——《计算机组成与接口》

Posted DO_Tonight

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机四级嵌入式知识点——《计算机组成与接口》相关的知识,希望对你有一定的参考价值。

前言

2020年版 《计算机组成与接口》印刷错误

P29页------SUB应该是减法的意思

P34页------DI应该与ES连用,而不是DS

第一章 计算机系统概述

1.1 计算机的基本组成

1.1.1 硬件系统

1.1.1.1 冯诺依曼计算机的特点

- 组成:运算器,存储器,控制器,数入和输出设备

- 机器以运算器为中心,输入输出设备与存储器之间的数据传输通过运算器完成(这是原始的冯·诺依曼结构,现已经改成以存储器为中心的结构)

1.1.1.2 哈佛计算机的特点

- 存储器分为两部分:指令存储器和数据存储器

- 现,都取长补短,主存储器采用冯诺依曼结构,并设置Cache,采用哈佛结构

1.1.2 软件系统

1.1.2.1 系统软件

1.1.2.2 应用软件

1.1.3 计算机系统层次结构

1.2 计算机硬件的主要技术指标

1.2.1 机器字长

1.2.2 主存储量

1.2.3 运算速度

- 执行时间(响应时间、延迟时间)和吞吐率(执行速度)是衡量计算机性能的基本指标

1.3 数据信息的表示

1.3.1 常用计数制及其相互转换

-

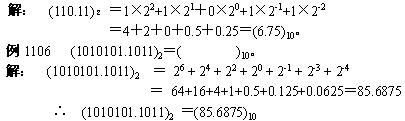

非十进制小数转化为十进制小数

采用加权系数的展开式来进行计算,例:

-

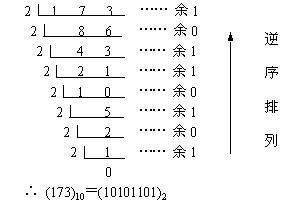

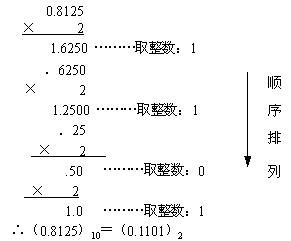

十进制小数转化为非十进制小数

整数部分逆序排列,小数部分顺序排列,例:

1.3.2 真值与机器数

- 把符号“数字化”的数叫做 机器数;把带‘+’和‘-’符号的数叫做真值,例如真值为+0.1011,机器数为0.1011,真值为-0.1011,机器数为1.1011.

1.3.3 二一十进制编码

有权码(BCD码)和无权码(余3码和格雷码)

1.3.4 ASCII码

数字0 - 9 的范围是30H - 39H

字母A - Z 的范围是41H - 5AH

字母a - z 的范围是61H - 7AH

1.3.5 定点数的表示

- 定义:小数点的位置固定的数叫做定点数-----区别于浮点数

1.3.5.1 原码、反码、补码、移码

原码:符号位加上真值的绝对值。

反码:正数的反码是原码,负数的反码是原码的基础上,符号位不变,其余各位取反

补码:正数的补码是原码,负数的补码是反码+1

移码:用来表示浮点数的阶码,只表示整数,它与补码的数值位相同,符号位相反

x = +0.1101 原码是0.1101,反码是0.1101,补码是0.1101

x = -0.1101 原码是1.1101,反码是1.0010,补码是1.0011

x = +1101 原码是01101,反码是01101,补码是01101

x = -1101 原码是11101,反码是10010,补码是10011

1.3.6 浮点数的表示

1.3.6.1 浮点数的表示

-

表示方法:数符+阶符+阶码数值+尾数数值

数符+尾数数值 = 尾数

阶符+阶码数值 = 阶码

-

尾数用定点小数表示,决定了浮点数表示的精度

-

阶码用整数表示,决定了浮点数表示的范围,阶符为正,实际小数点在尾数小数点的右边,反之。

-

由于机器字长是一定的,因此尾数与阶码形成了互相制约的关系,使用者需要在浮点数的精度与表示范围之间做一个权衡

1.3.6.2 浮点数的规格化

1.3.6.3 浮点数的表示范围

1.4 CPU的基本结构和工作原理

1.4.1 CPU的基本结构

1.4.1.1 CPU的基本组成

- 构成:数据通路(Data Path) + 控制单元(Control Unit)

- CU从存储器里面取出指令,译码指令,将数据从存储器或IO设备移入CPU内部总线,或将数据从CPU北部总线移到存储器和IO设备。

1.4.1.2 CPU中的主要寄存器

- 通用寄存器

- 专用寄存器

- 存储器缓冲寄存器(MBR)

- 存储器地址寄存器(MAR)

- 程序计数器(PC)

- 指令寄存器(IR)

- 状态寄存器(PSW)

- OF (over)溢出标志,溢出置1

- SF (sign)符号标志,负数置1

- ZF (zero)零标志,结果为0,置1

- AF (auxiliary)辅助进位标志,低4位有向高4位进位就置1

- PF (parity)奇偶标志,低8位“1”的个数为偶数就置1

- CF (carry)进位标志,有进位置1

- DF (direction)方向标志,地址递减,置1

- IF (interrupt)置1表示允许“外部可屏蔽中断”

- TF (trap)陷阱标志,置1,表示每执行完一条指令都会产生一次中断,DEBUG就是利用的这个

1.4.2 指令和指令周期

1.4.2.1 指令信息

-

操作码 + 源操作数或地址 + 操作结果的存放地址 + 下一条指令的地址

-

指令格式:四地址指令、三地址指令、二地址指令、一地址指令、零地址指令

1.4.2.2 指令和数据的寻址

-

指令寻址方式

- 顺序寻址(PC+1)

- 跳跃寻址(中断)

-

操作数寻址方式

- 立即数寻址

- 直接寻址

- 间接寻址

- 寄存器寻址和寄存器简介寻址

- 相对寻址、基址寻址、变址寻址

1.4.2.4 指令周期

- 指令周期

- 取址阶段(取址、分析)

- 执行阶段(执行)

- CPU周期(机器周期)

- 时钟周期(脉冲)

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-MjZHloe3-1662779227770)(F:\\计算机4级\\picture\\IMG_20220901_194303_edit_33170772859000.jpg)]

- 所有指令的取址阶段是完全一样的,具体的流程图请看教材P22

1.4.3 指令流水线技术

1.4.3.1 顺序方式

1.4.3.2 重叠方式

-

一次重叠、二次重叠

-

取址合并到分析阶段(从寄存器中取址花费时间很少)

-

先行控制技术

1.4.3.3 流水线控制方式

-

背景:从重叠方式发展起来

-

分为填入、满载、排空三个阶段

1.4.3.4 流水线的主要性能

-

吞吐量

-

单位时间内流水线上完成指令的数量

-

最大吞吐量(满载)

-

实际吞吐量

-

当执行指令的条数远大于一条指令的段数,T实际吞吐量 == T最大吞吐量

-

-

加速比

-

流水线的工作速率 / 顺序方式的工作速率

-

在执行指令的条数远大于一条指令的段数的情况下,一条指令的段数越大,加速比越大

-

-

效率

- 流水线上各功能段的利用效率 = TP * ▲t

1.4.3.5 造成流水线冲突的主要因素

-

资源相关

- 两条指令同时访问造成资源的冲突,解决方法:往后延迟一个时钟或哈佛结构

-

数据相关

ADD R1,R2,R3 ;(R2) + (R3) --> (R1)

SUB R4,R1,R5 ;(R1) - (R5) --> (R4)

应该要先得到R1的值,才能去执行下一条指令,但是在流水线中

IF ID EX MEM WB

IF ID EX MEN WB

在这里,先写后读无法实现,所以造成了冲突

-

- 解决方法:延迟后推或采用定向技术

-

控制相关

- 转移指令的存在,一般在MEN之后才生成转移指令,因此要停顿三个节拍

1.4.4 8086CPU

1.4.4.1 8086CPU的功能结构

-

简介

- 16根数据线,20根地址线(于是引入了偏移地址)

-

总线接口单元(BIU)

- 负责CPU与存储器、IO端口的数据传送(包括发和收)

- 包括

- CS 16位的代码段寄存器

- DS 16位的数据段寄存器

- SS 16位的堆栈段寄存器

- ES 16位的扩展段寄存器

- IP 16位的指令指针寄存器,存放偏移地址,与CS连用,确定下一代码的物理地址

- 地址加法器,用来形成20位的地址

- 1个6字节的指令队列缓冲器

- 总线控制部件

-

执行单元(EU)

- 包括

- ALU

- 暂存器

- 16位通用寄存器 AX、BX、CX、DX,可以拆开使用

- SP 堆栈指针寄存器

- BP 基址指针寄存器,存放堆栈的偏移地址

- SI 源变址寄存器,与DS连用,确定数据段某一单元的地址

- DI 目的变址寄存器,与ES连用,去欸的那个扩展段某一段元的地址

- PSW

- 控制电路

- 包括

1.4.4.2 8086CPU的工作时序

-

时钟周期

-

总线周期

- 一个最基本的总线周期由4个时钟周期组成,T1,T2,T3,T4,可以插入若干个等待周期Tw

- T1:CPU在多路复用总线上发出地址信息,以指出要寻址的存储单元或外围设备端口的地址

- T2:CPU从总线上撤销地址,使低16位浮置高阻状态,为传输数据做准备

- T3:总线的最高4位(A19~ A16)提供状态信息,低16位上传输数据

- TW:等待状态,只穿插在T3和T4之间

- T4:总线结束周期

- 一个最基本的总线周期由4个时钟周期组成,T1,T2,T3,T4,可以插入若干个等待周期Tw

-

系统复位和启动操作

- 复位要求4个时钟周期以上的高电平

-

最小模式下的读总线周期

-

最小模式下的写总线周期

-

最小模式下的总线保持和总线响应周期

-

最大模式下的读写总线周期

1.4.5 Pentium 微处理器

1.4.5.1 Pentium微处理器结构

- 总线接口单元(BIU)64位数据线,32位地址线,众多控制线

- U、V流水线

- 数据Cache和指令Cache

- 指令预取部件、指令译码器、控制ROM、分支目标缓冲器(BTB)

- 控制部件,作用于ID和EX之间

- 浮点运算单元

- 分段与分页部件,存储的地址管理部件

1.4.5.2 Pentium的内部寄存器

-

通用寄存器

- EAX、EBX、ECX、EDX、ESP、EBP、ESI、EDI

-

指令指针寄存器(EIP)

-

段寄存器

- CS、DS、SS、ES、FS、GS

-

控制寄存器

- CR0

- PE,置1进入保护模式

- MP,置1,在执行WAIT指令时会产生一个协处理器无效信号

- EM,置1,使所有指令都产生一个协处理器无效信号,只有EM == 0,才会使协处理器指令在协处理器上运行

- TS,置1,表示任务切换

- NE,置1,表示执行浮点运算时出现错误

- WP,置1,对用户执行写保护

- AM,置1,表示对存储器访问时已经实现了校准

- NW,置1,表示用回写方式对Cache操作

- CD,置1,片内Cache被禁止

- PG,置1,启动片内分页部件工作

- CR0

-

- CR2和CR3

- 用于分页和分段管理机制的使用

- CR3用于保存页目录的起始物理地址,PCD == 1,禁止片外Cache,PWT == 1,访问Cache通写方式

- CR2和CR3

-

- CR4

- MCE == 1,表示允许机器检查异常

- PSE == 1,页面大小为4MB否则为4KB

- DE == 1,表示允许断点设置

- TSD == 1,表示使读时间计数器指令可在任何时间执行,否则只允许在系统级执行

- PVI == 1,表示在保护模式下允许中断

- VME == 1,表示允许虚拟8086方式

- CR4

-

调试寄存器

-

描述符表寄存器

-

附加寄存器

-

标志寄存器

1.4.5.3 Pentium的工作模式

- 实地址模式

- 保护模式

- 虚拟8086模式

- 系统管理模式(SMM)

- 四种模式间的相互转换

1.4.5.4 Pentium的内存保护技术

- 每个描述符中都有一个2位的DPL标志,0为最高优先级

第二章 存储器

2.1 概述

2.1.1 存储器的分类

2.1.1.1 按存储介质分

- 半导体存储器

- 磁表面存储器

- 磁芯存储器

- 光盘存储器

2.1.1.2 按存取方式分

- 随机存取存储器(RAM)

- 只读存储器(ROM)

- 顺序存取存储器(SAM)磁带

- 直接存取存储器(DAM)磁盘机

2.1.1.3 按信息的可保存性分

- 易失性存储器

- 非易失性存储器

2.1.1.4 按存储器在计算机系统中的作用分

-

高速缓冲存储器(Cache)

-

主存储器

-

辅助存储器

2.1.2 存储器的层次结构

- 存储容量、存储速度、每位价格 是存储器的三大性能指标

2.1.3 高速存储技术

2.1.3.1 单体多字系统

- 常规的主存是单体单字存储器,一个存储体,一个周期智能存储一个字

- 改成单体多字后可以明显提高速度,但是有一个很明显的缺陷,遇到跳转指令效果不显著

2.1.3.2 多体并行系统

- 高位交叉编址

- 连续的地址分布在同一存储体中,一个存储体存满才转到下一个存储体去

- 低位交叉编址

- 连续的地址分布在相邻的存储体中,同一存储体内的地址都是不连续的,其地位地址用来表示体号,高位地址用来表示体内地址,大大增加了存储器的带宽

2.1.4 虚拟存储技术(主存-辅存)

2.1.4.1 虚拟存储器的基本概念

- 只是一个大容量的逻辑模型,不是任何实际的物理存储器

- 虚拟存储器指的是主存——辅存层次

- 在实际的物理存储层次上,所编写的程序和数据在操作系统的管理下,先装入磁盘,然后操作系统将当前运行所需要的部分调入主存,供CPU使用,其余暂不运行的部分留在磁盘中

2.1.4.2 页式虚拟存储器

- 虚地址 = 虚页号 + 页内地址;实地址 = 实页号 + 页内地址

- 实页和虚页的页内地址都是一样的,只需要查找页表,将虚页号向实页号进行一个转换

- 这种页式虚拟存储器会有页内碎片,且无法实现程序的共享和保护

2.1.4.3 段式虚拟存储器

- 这里的段是根据程序结构划分的,每个段的长度因程序而异

2.1.4.4 段页式虚拟存储器

2.1.4.5 快表和慢表

-

要想使访问虚存的速度接近访问主存的速度,需要加快查表的速度

-

于是页表也增加了Cache的东西

2.1.5 地址映像技术(Cache-主存)

2.1.5.1 全相联映像方式

- 主存中的任何一个块都可以映射到Cache里面,块冲突率低,但是地址变换速度慢

2.1.5.2 直接相联映像方式

- 主存中的每一个块只能被装入Cache中的特定位置

2.1.5.3 组相联映像方式

- 两种方式的相结合

2.1.6 替换策略

- 替换策略是解决冲突的一种方法(算法)

2.1.6.1 先进先出(FIFO)

- 最先调入Cache的块作为被替换的块,但是不呢个提高Cache的命中率

2.1.6.2 近期最少使用(LRU)

2.1.6.3 随机法

2.1.7 保护模式下Pentium微处理器的存储管理

2.1.7.1 保护模式下的分段管理

-

由段选择符里面的13位段索引字段 确定 段描述符在段表中的位置,然后根据这个位置取出基地址。线性地址 = 基地址 (32位)+ 偏移地址(32位)

-

解释一下前面所说的Pentium微处理器的最大的虚拟存储空间是64TB

- 首先是32位的线性地址由4GB

- 其次是段选择符的高14位的描述符,可以决定16KB

- 所以总共的虚拟空间可以达到64TB

-

段选择符

- 高13位是某个段描述符在描述符表中的偏移地址,TI == 0,表示选择全局描述符表,否则是局部描述符表,RPL是请求特权层的级别

- 段选择符 = 高13位 + TI + RPL

- 存在一个段描述符高速缓存寄存器(64位),用来保存段选择符指向的64位的段描述符

-

段描述符

- 程序段描述符

- 系统段描述符

-

门描述符

-

全局描述符表及寄存器

-

局部描述符表及寄存器

2.1.7.2 保护模式下的分页管理

- 页表

- 页目录

- 页变换过程

- 首先将虚地址通过分段管理部件转换为线性地址,然后通过分页管理部件转换为物理地址

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-UTnAowjn-1662779227770)(F:\\计算机4级\\picture\\IMG_20220902_211850_edit_74154222679830.jpg)]

2.2 主存储器

2.2.1 主存储器的基本结构和指标

2.2.1.1 主存中存储单元地址的分配

2.2.1.2 主存的技术指标

- 存储容量 = 存储单元个数 * 存储字长

- 存储速度

- 存取时间(工作全程)

- 存取周期(两次工作间隔)

- 主存带宽(单位时间内传输的字节数)

2.2.2 随机存取存储器

2.2.2.1 静态随机存取存储器(SRAM)

-

六管静态RAM存储元电路

-

SRAM的组成

- 存储体

- 地址译码器

- 单译码方式,适用于小容量存储器

- 双译码方式,适用于大容量存储器

- 驱动器

- IO电路

- 片选与读/写控制电路

- 输出驱动电路

-

SRAM芯片实例(2114)

-

2114RAM读写时序

2.2.2.2 动态随机存取存储器(DRAM)

-

四管DRAM存储元电路

-

靠栅极电容存储信息,需要不时的刷新才能存储信息,这个操作也称为假读

-

单管DRAM存储元电路

-

DRAM的刷新

- 刷新间隔

- 刷新方式

- 集中式刷新方式:存取速度高,但是存在死区

- 分布式刷新方式:在每一个刷新周期内进行刷新,这样增加了系统的存储周期,降低了整机的速度

- 异步式刷新方式:每隔一定的时间安排一次刷新,结合了前面两种方法的优点

2.2.3 只读存储器

2.2.3.1 掩膜式ROM

2.2.3.2 一次可编程ROM(PROM)

2.2.3.3 可擦除可编程ROM(EPOROM)

2.2.3.4 闪速存储器(Flash)

- 既可以长期保存信息,又可以快速进行擦除改写

2.2.4 存储器与CPU的连接

2.2.4.1 存储容量的拓展

-

位拓展

- 相当于存储芯片的重叠,64K * 1 --> 64K * 8

-

字拓展

- 增加地址线,可以把64K的看成是更高的的容量

-

字位拓展

2.2.4.2 存储器与CPU的连接

2.3 辅助存储器

2.3.1 硬磁盘存储器

2.3.1.1 硬磁盘存储器的分类

-

固定磁头的磁盘存储器

-

移动磁头的磁盘存储器

2.3.1.2 硬磁盘存储器的结构

-

磁盘驱动器

-

磁盘控制器

-

盘片

2.3.1.3 硬磁盘的磁道记录格式

-

定长记录格式

- 即使主机只需要读取一个字节,也必须将这个字节所在的扇段的全部信息载入主存

- 定位信息:台号 + 磁道号 + 盘面号 + 扇段号

-

不定长记录格式

- 每个记录包括计数区、关键字区、数据区,因此也成为CKD结构

-

硬磁盘存储器的主要性能指标

- 存储密度

- 存储容量

- 硬盘转速

- 平均存储时间

- 数据传输率

2.3.2 光盘存储器

-

只读型光盘(CD-ROM)

-

一次写入型光盘(WORM)

-

可擦写型关盘

2.3.2.1 光盘的存取原理

2.3.2.2 光盘存储器的组成

第三章 汇编语言程序设计

- 由于之前有课程学过汇编语言,这里只做简单的记录

3.1 概述

3.2 8086微处理器的寻址方式

3.2.1 立即数寻址

3.2.2 寄存器寻址

3.2.3 直接寻址

3.2.4 寄存器间接寻址

3.3 8086汇编指令系统

3.3.1 传送类指令

-

MOV DST, SRC

- 这里的DST不能是CS和IP

- 如果要把一个常数传送到存储器中,必须用伪指令WORD PTR 或者是BYTE PTR来指定要传输的常数字是以8位还是以16位来传输的

- DST和SRC不允许同时为存储器地址

- 错误写法:

- MOV CS, AX

- MOV WORD PTR[DI], WORD PTR[SI]

- MOV [200], [100]

- MOV WORD PTR[200], 100 方括号里面应该是寄存器

- MOV AX, BL 大小不匹配

- MOV AL, DX 大小不匹配

-

PUSH与POP

-

XCHG 交换指令

3.3.2 算数类指令

-

ADD、ADC和SUB、SBB

-

INC和DEC

-

MUL SRC和IMU SRC

- 如果SRC是8位的,那么 = (AL)*(SRC)–> AX;

- 如果是16位的, = (AX) * (SRC)–> DX(高位),AX(低位)

-

DIV和IDIV

- 如果SRC是8位的,(AX)/ (SRC)–> AX,AL放商,AH放余数;

- 如果SRC是16位的,(DX)(AX)/ SRC --> DX,AX,AX放商,DX放余数

-

CMP

3.3.3 逻辑运算和移位指令

-

AND

-

TEST 也是与操作,但是结果不放入DST

-

OR

-

XOR

-

NOT

-

NEG 取补操作,将操作数按位取反后加1

-

非循环移位指令

- SAL、SHL,两个的移动方法完全一样

- SAR、SHR,算数右移(SAR)左边补0,逻辑右移补符号位

-

循环移位指令

- ROL、ROR 不带进位

- RCL、RCR 带进位,CF位去进行补充

3.3.4 串操作指令

3.3.5 CPU控制类指令

3.3.6 输入输出类指令

3.3.7 转移类指令

3.3.8 不可执行指令

3.3.8.1 常量定义伪指令

- STR EQU Num

3.3.8.2 变量定义伪指令

- DB、DW、DD

3.3.8.3 存储类型定义伪指令

- BYTE PTR

- WORD PTR

- DWORD PTR

3.3.8.4 标号距离定义伪指令

3.4 汇编程序

3.4.1 汇编程序的基本结构

DATAS SEGMENT

DATAS ENDS

STACKS SEGMENT

STACKS ENDS

ATTACTS SEGMENT

ATTACTS ENDS

CODES SEGMENT

ASSUME CS:CODES, DS:DATAS, SS:STACKS, ATTACKS:ES

START:

MOV AX, DATAS

MOV DS, AX

CODES ENDS

END START

3.4.2 顺序程序结构

- 例1:设有三个无符号变量A = 78, B = 21, C = 66,求其平均值N和余数M

DATAS SEGMENT

A DB 78

B DB 21

C DB 66

N DB 0

M DB 0

DATAS ENDS

CODES SEGMENT

ASSUME CS:CODES, DS:DATAS

START:

MOV AX, DATAS

MOV DS, AX

XOR AX, AX ;初始化DS段寄存器

MOV AL, A

ADD AL, B

ADD AL, C

DIV AX, 3

MOV N, AL

MOV M, AH

CODES ENDS

END START

3.4.3 分支程序结构

- 例2:设有8个有符号的数,求其中大于0的个数,并存入变量PLUS中。假设数据为8位数,其中最左边一位为符号位。

DATAS SEGMENT

NUM DB 78H,89H,0,21H,0A8H,98H,33H,66H

PLUS DB 0

DATAS ENDS

CODES SEGMENT

ASSUME CS:CODES, DS:DATAS

START:

MOV AX, DATAS

MOV DS, AX

LEA SI, NUM

MOV DX, 8

AGAIN:

MOV AL, [SI]

INC SI

CMP AL, 0

JLE AGAIN_ONE

INC PLUS

AGAIN_ONE:

DEC DX

JNZ AGAIN

CODES ENDS

END START

3.4.4 循环程序结构

- 例3:计算1到20的和

CODES SEGMENT

ASSUME CS:CODES

START:

MOV CX, 20

XOR AX, AX ;寄存器清0

MOV BX, 1

AGAIN:

ADD AX, BX

INC BX

LOOP AGAIN ;CX计数寄存器,在LOOP中充当隐含的计数器

CODES ENDS

END START

3.4.5 子程序结构

- 变量String为16个大小写混合的英文字母,请将其改写成大写字母

DATAS SEGMENT

String DB 'schoolofCoMPuter'

A_Str DB 16 DUP(?)

DATAS ENDS

CODES SEGMENT

ASSUME CS:CODES, DS:DATAS

BIG_CHAG PROC

AND AL, 3FH

RET

BIG_CHAR ENDP

START:

MOV AX, DATAS

MOV DS, AX

XOR AX, AX

MOV SI, OFFSET String

MOV DI, OFFSET A_Str

MOV CX, 16

AGAIN:

MOV AL, [SI]

CALL BIG_CHAR

MOV [DI], AL

INC SI

INC DI

LOOP AGAIN

CODES ENDS

END START

3.4.5 中断程序结构

DATAS SEGMENT

DATAS ENDS

STACKS SEGMENT

STACKS ENDS

ATTACTS SEGMENT

ATTACTS ENDS

CODES SEGMENT

ASSUME CS:CODES, DS:DATAS, SS:STACKS, ATTACKS:ES

Inter PROC ;中断服务子程序

Inter ENDP

START:

MOV AX, DATAS

MOV DS, AX

XOR AX, AX

MOV AX, offset Inter

MOV [INT_VER_IP], AX

MOV AX, seg Inter

MOV [INT_VER_CS], AX

CLI ;打开可屏蔽中断标志

CODES ENDS

END START

第四章 计算机中断技术

4.1 中断的基本概念

- 如果中断类型码为16进制数32H,那么CPU收到后,把32H乘以4得到0C8H。0C8H开始的4个连续单元就是中断向量的地址,假设(0C8H) = 18H,(0C9H) = 20H,(0CAH) = 10H,(0CBH) = 20H,那么,中断处理程序的入口地址为2010H:2018H,2010H为段地址,2018H为偏移地址,那么8086CPU在响应中断向量码32H的时候,就会转到物理地址为2010H < 4 + 2018H = 22118H处取指令执行。

4.2 Pentium微处理器的中断

- 可以分为外部IO引起的事件中断,异常中断(故障中断、陷阱中断、异常终止中断)

4.2.1 中断描述符表

- 分为了实地址模式下和保护模式下

4.2.2 中断类型码和中断程序间的关系

- 收到中断类型码后,把该码乘以8,找到IDT中对应的中断描述符,然后找到中断描述符中的基地址和偏移地址,得到实际的物理地址。

4.3 中断控制器 8259A 芯片简介

- 背景:由于8086CPU外部可屏蔽中断只有一个(还有一个不可屏蔽中断),一个INTR无法满足要求。

4.3.1 8259A 功能

- 可管理8个中断源

- 采用9块芯片最多可以管理64个中断源

- 可编程为高电平触发或者是脉冲边沿触发

- 8个中断输入的任何一个可以由软件屏蔽

- 只有IMR = 0,IRR的请求信号才可以引起中断

- 具有查询方式,由CPU定时发出查询命令,必须关闭CPU对外部中断的请求

4.3.2 8259A 中断优先级的设置

- 自动旋转方式

- 特殊旋转方式

4.3.3 8259A 优先级嵌套方式

- 全嵌套方式:上电复位后没有选择其他的优先级方式,自动进入全嵌套方式

- 特殊嵌套方式:多用于多片芯片连用

4.3.4 8259A 中断屏蔽方式

- 一般中断屏蔽:直接对OCW1编程

- 特殊中断屏蔽:可以由OCW3编程

4.3.5 8259A 中断结束方式

-

自动中断结束方式

-

非自动中断结束方式

4.3.6 8259A 编程

- 例:如图所示,设8259A芯片的端口地址为20H和22H,试编程:是开关K每按一次,8086CPU中的寄存器CL内容便加1

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Mu89MhDc-1662779227770)(F:\\计算机4级\\picture\\IMG_20220903_220047_edit_113348610291036.jpg)]

CODES SEGMENT

ASSUME CS:CODES

START:

CLI

MOV ES, AX ;ES清0

MOV BL, 30H ;任意给定一个数,作为ICW2的高5位

MOV AL, BL ;

ADD Al, 3 ;IR3

MUL AL, 4 ;计算中断向量表地址

MOV DI, AX

MOV AX, OFFSET INTV;获取中断处理程序偏移地址

MOV ES:[DI], AX ;

第五章 计算机和外设的数据交换技术

5.1 概述

5.2 CPU和外设之间的数据传送方式

5.2.1 程序传送方式

5.2.1.1 无条件传送方式

- 定义:不需要校验传输信息的正确性

5.2.1.2 条件传送方式

- 定义:会校验传输信息的正确性

5.2.2 中断传送方式

- 相比于查询方式,提高了CPU的使用效率

5.2.3 DMA传送方式

- 直接存储器访问

5.2.3.1 DMA控制器的工作方式

- 单字节传送

- 块传送

- 请求传送

5.3 串行通信

5.3.1 基本概念

5.3.1.1 串行通信模式

-

单工模式:一方固定发送,一方固定接收

-

半双工模式:数据允许在两个方向上传输,但是在某同一时刻,只能由一个方向进行传输

-

全双工模式

-

码元、比特率、波特率(码元传输速率):一个码元可以包含多个比特

5.3.1.2 串行通信原理

- 位同步与字符同步

5.3.1.3 串行通信传输方式

- 异步传输方式

- 同步传输方式

5.3.1.4 RS-232-C标准

- 25针连接器简化后改为9针连接器

- 采用负逻辑规定逻辑电平,提高抗干扰能力

5.3.2 可编程串行通信接口8251A

5.3.2.1 基本介绍

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BLc0o83s-1662779227771)(F:\\计算机4级\\picture\\IMG_20220904_113415_edit_133914683331648.jpg)]

- 数据总线缓冲器:三态双向缓冲器,用于同CPU交换数据

5.3.2.2 工作原理

- 发送方式工作原理

- 接收方式工作原理

5.3.3 8251A的编程

5.3.3.1 8251A的模式字

- 用于规定8251A的工作模式

5.3.3.2 8251A的控制字

- 用于控制8251A的基本功能,如 是否允许接收或发送

5.3.3.3 8251A的状态字

- 反映在传输过程中出现的各种状态

5.3.4 8251A应用举例

- P158

5.4 并行通信

5.4.1 可编程并行通信接口8255A

- 基本简介,类似于8251A

5.4.2 8255A的编程

5.4.2.1 8255A的方式选择控制字

5.4.2.2 8255A的置位复位控制字

- 只用于端口C的

5.4.2.3 8255A的工作方式

- 方式0(基本输入/输出)

- 方式1(具有握手信号的输入/输出)

5.4.2.4 8255A的应用实例

5.5 计数器/定时器接口电路8253(暂时没写,看考试题目)

第六章 DA和AD转换

6.1 基本概念

6.1.1 计算机的模拟接口

- 传感器–>放大–>低通滤波–>采样保持–>AD采样–>微型计算机–>DA输出

6.1.2 运算放大器的原理及应用

6.1.2.1 运算放大器的应用

-

比例电路

-

积分电路,电容在反馈支路

-

微分电路,电容在输入支路

-

模拟电压比较器

6.1.3 AD7501芯片简介

- 八进一出的模拟开关,可以利用软件控制开关选择8个输入中哪个与输出相连

6.2 DA转换器

6.2.1 基本工作原理

6.2.2 DA转换电路常用的参数和术语

-

绝对精度

-

分辨率

-

建立时间

-

线性度(非线性误差)

-

相对精度,绝对精度相对于满量程输出的百分比

6.2.3 DAC0832数模转换器

-

直通模式和缓冲模式,可以通过控制LE1和LE2来实现

-

还可以利用缓冲方式,将8位分辨率的芯片提高到16位的

6.3 AD转换器

6.3.1 基本工作原理

-

计数式AD转换器,转换速度慢

-

逐次逼近式AD转换器,从位数的最高位逐个往下进行逼近

-

积分式AD转换器,利用积分电路的充放电

6.3.2 AD转换电路常用的参数和术语

- 分辨率

- 转换时间

- 转换精度

- 量程

6.3.3 ADC0809芯片简介

- 逐次逼近式模数转换器

6.3.4 ADC0809案例

- 利用8255A和ADC0809,设8255的端口地址为80H、82H、84H、86H。采用查询的方式完成对ADC0809的8个模拟信道进行一次数据采样的程序

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-UA8Y1U3I-1662779227771)(F:\\计算机4级\\picture\\IMG_20220905_152451_edit_181267446244735.jpg)]

DATAS SEGMENT

BUFFER DB 20 DUP(?)

DATAS ENDS

CODES SEGMENT

ASSUME CS:CODES, DS:DATAS

START:

MOV AX, DATAS

MOV DS, AX

MOV AL, 88H

OUT 86H, AL

MOV CX, 8 ;8个通道

MOV BL, 0 ;指向信道地址

MOV DI OFFSET BUFFER

NXT:

MOV AL,BL

OUT 84H, AL ;发送ADD要转换的IN

MOV AL, 7

OUT 86H, AL ;发送ALE信号并启动AD转换

MOV AL, 6

OUT 86H, AL

NT:

IN AL, 6 ;

TEST AL, 80H ;

JNZ NT ;

IN AL, 80H ;

MOV [DI], AL ;

INC DI ;

INC BL ;

LOOP NXT

CODES ENDS

END START

第七章 人机接口

7.1 鼠标

7.2 键盘

7.2.1 矩阵键盘原理

- 可以利用R-S触发器硬件消抖

7.2.2 个人计算机键盘原理

- 重复不断的扫描查表

7.3 显示

7.3.1 发光二极管

7.3.2 七段数码显示器

7.3.2 液晶显示器

7.4 打印机

7.4.1 针式打印机

7.4.1 喷墨打印机

7.4.1 激光打印机

第八章 总线

8.1 概述

8.1.1 总线结构

8.1.1.1 单总线结构

- 在某一时刻,只允许有一个部件向总线发送信息

8.1.1.2 多总线结构

8.1.2 总线分类

8.1.2.1 片内总线

8.1.2.2 板级总线

8.1.2.3 系统总线

- 地址总线

- 数据总线

- 控制总线

以上是关于计算机四级嵌入式知识点——《计算机组成与接口》的主要内容,如果未能解决你的问题,请参考以下文章