标准单元库

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了标准单元库相关的知识,希望对你有一定的参考价值。

文章目录

本章介绍库(library)里单元描述中所提供的时序信息。单元可以是标准单元、IO缓冲器或者是如USB内核这样的复杂IP。

- 除时序信息外,库单元描述中还包含一些其它属性,例如单元面积和功能,这些属性与时序无关,但在RTL综合(synthesis)过程中会用到。在本章中,我们仅关注与时序和功耗计算有关的那些属性。

- 可以使用各种标准格式来描述库单元,各种格式的内容基本相似,本书中使用Liberty语法描述库单元。

- 本章前面部分介绍了线性和非线性时序模型,随后介绍了用于纳米技术的高级时序模型,这些将在3.7节中进行介绍。

3.1 引脚电容(pin capacitance)

单元的每个输入和输出都可以在引脚(pin)上指定电容。在大多数情况下,仅为单元输入引脚指定电容,而不为输出引脚指定电容,即大多数单元库中的输出引脚电容为0。

pin(INP1)

capacitance:0.5;

rise_capacitance:0.5;

rise_capacitance_range:(0.48, 0.52);

fall_capacitance:0.45;

fall_capacitance_range:(0.435, 0.46);

...

上面的示例展示了输入INP1引脚电容值的一般规格(specification)。在最基本的格式中,引脚电容被指定为单个值(在上面的示例中为0.5个单位)。电容单位通常为皮法拉(pF),一般在库文件的开头指定。单元描述中还可以为rise_capacitance(0.5个单位)和fall_capacitance(0.45个单位)分别指定值,这些值是指引脚INP1上发生电平上升和下降转换(transition)时的值。也可以将rise_capacitance和fall_capacitance的值指定为范围,并在描述中指定下限值和上限值。

3.2 时序模型(timing modeling)

逻辑单元的时序模型(timing model)旨在为设计中的各种单元实例(instance)提供准确的时序信息。通常会从单元的详细电路仿真中获得时序模型,用以对单元工作时的实际情况进行建模,且需要为逻辑单元的每个时序弧都建立一个时序模型。

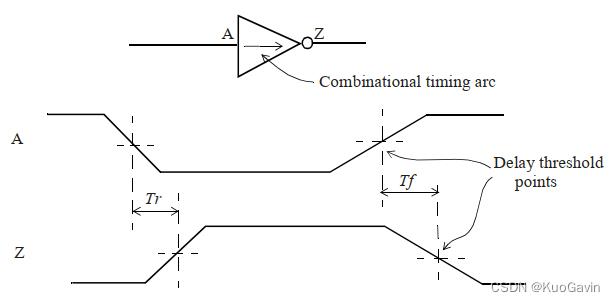

先来考虑简单逻辑单元反相器的时序弧,如下图,其中其输入引脚的上升(下降)沿造成输出针脚的下降(上升)沿。这两种时延分别对应于 T f T_f Tf(output fall delay)和 T r T_r Tr(output rise delay)。

注意,延迟是根据单元库中定义的阈值(threshold)点测量的,通常为50% V d d V_dd Vdd。 因此,延迟值指从输入经过其阈值点到输出经过其阈值点的延迟。

通过反相器的时序弧的延迟取决于两个因素:

- 输出负载,即反向器输出针脚上的电容负载;

- 输入信号的过渡时间(transition time);

延迟值与负载电容有单调关系:负载电容 ↑ \\uparrow ↑,延迟值 ↑ \\uparrow ↑;

延迟值与过渡时间的关系不定:多数情况下,过渡时间 ↑ \\uparrow ↑,延迟值 ↑ \\uparrow ↑;某些情况下,输入信号阈值点(用于测量延迟)与单元的内部开关点(switching point)明显不同,此时通过单元的延迟可能相对于输入信号过渡时间表现出非单调行为:过渡时间 ↑ \\uparrow ↑,延迟值 ↓ \\downarrow ↓,尤其负载电容值较小的情况下。

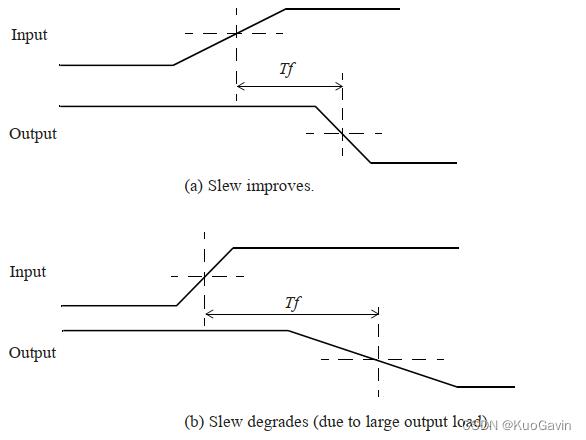

逻辑单元输出引脚的压摆(slew)主要取决于输出引脚的输出电容:输出信号过渡时间会随着输出负载的增加而增加。因此,在输入端压摆时间(压摆是模电中概念,过渡时间是数电中概念)较大(过渡时间较长,理解即可不必纠结)情况下,选择合适的单元类型及输出负载,可以改善输出端的压摆。如下图所示,(b)由于更大的负载,所以压摆就很大。

以上是关于标准单元库的主要内容,如果未能解决你的问题,请参考以下文章