关于建立时间与保持时间

Posted 秦枫-_-

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了关于建立时间与保持时间相关的知识,希望对你有一定的参考价值。

建立时间与保持时间的概念?

建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。

建立时间裕量与保持时间裕量

建立时间裕量:如果数据信号在时钟边沿触发之前的持续时间要大于建立时间Tsu,那么超出的部分时间即为建立时间裕量。

保持时间裕量:如果数据信号在时钟边沿触发之后的保持时间要大于保持时间Thd,那么超出的部分时间即为保持时间裕量。

为什么触发器要满足建立时间和保持时间?

因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后

触发器的输出将不稳定,在 0 和 1 之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是

你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能

不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

(比较容易理解的方式)换个方式理解:需要建立时间是因为触发器的 D 端像一个锁存器在接受数据,为了稳定的设

置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来锁存状态,从后级门

传到前级门需要时间。

设计建立时间与保持时间的本质:

数据不能传输太快也不能传输太慢

数据不能传输太快?

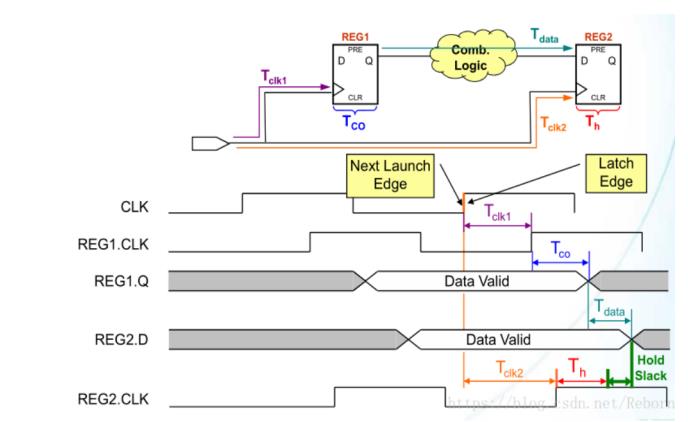

如下图:数据在一个时钟周期内就从第一级触发器到达了第二级触发器

·

其中 Tco 是触发器输入数据到触发器输出数据的延迟时间(Tco = Tsetup+Thold),Tdata 是组合逻辑延迟(路径延

迟),两寄存器之间时钟偏移 Tth= clk2-clk1,如图所示,要满足数据在 hold 中保持不变,就必须满足

Tclk1+Tco+Tdata>=Tclk2+Thold,即 Thold<=Tco+Tdata-Tth。

数据不能传输太慢?

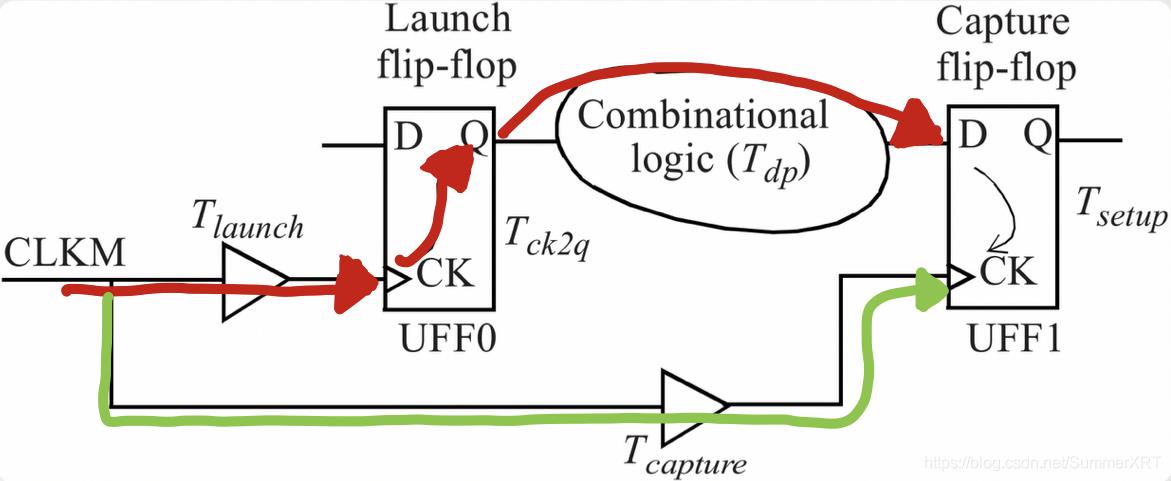

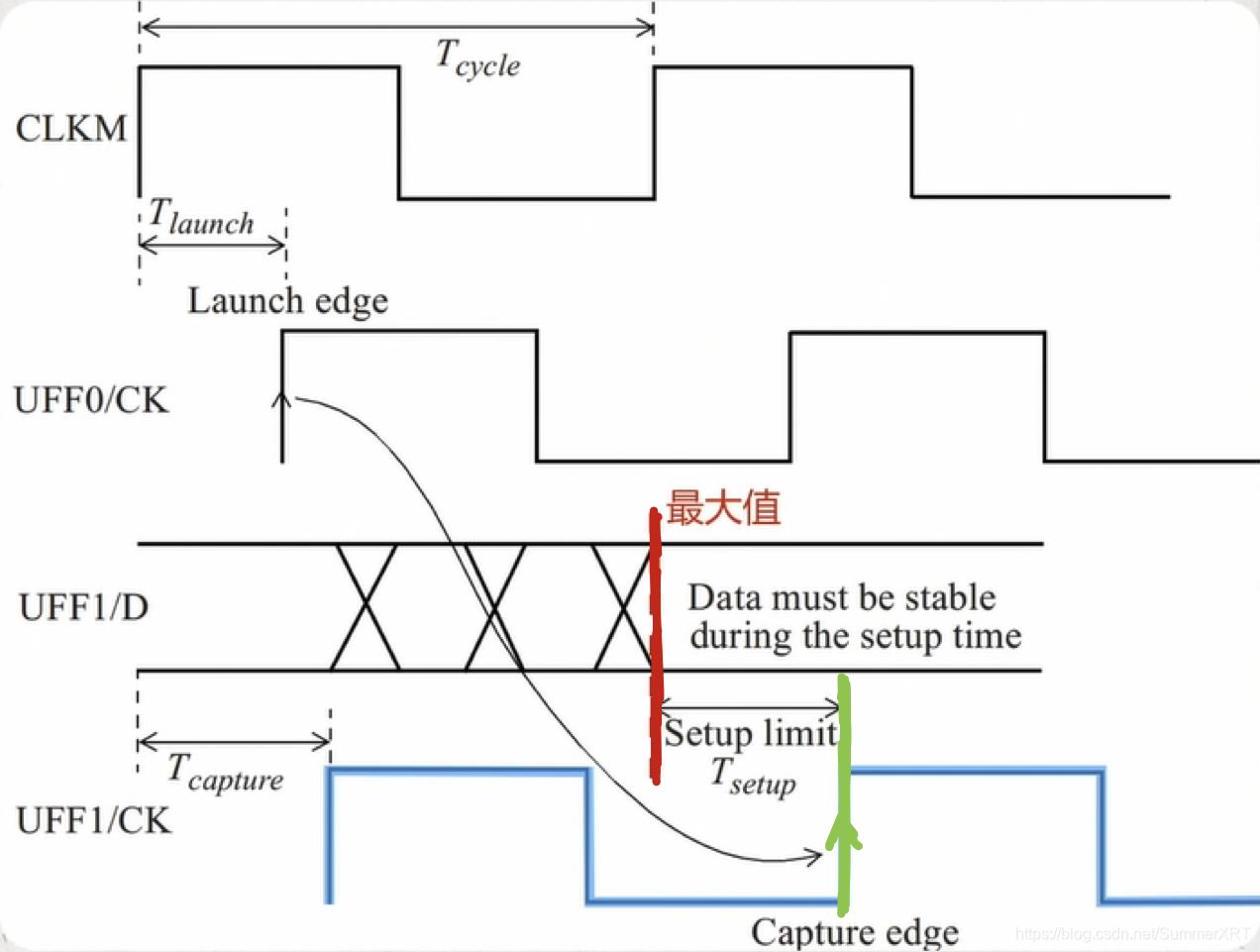

数据在第二个始终周期到达了二级寄存器:

图中Tck2q=Tco

Tlaunch=Tclk1

Tcapture=Tclk2

Tdp=Tdata

解释上图,第二个触发器要想满足setup time,就必须要满足:

上图中绿色竖线为时钟源点经过延迟,到第二个触发器的时间(对应绿色路径)

对应红色的路径部分,经过组合逻辑,到达第二触发器的Q端,最晚只能到达上图的红色竖线部分,否则就没办法,满足建立时间。

由此,我们可以推迟公式:

Tclk1 + Tco + Tdata ≤ Tclk2 + Tcycle - Tsetup

可以计算出想要满足第二个寄存器的建立时间,就必须要时钟周期 T>=Tco+Tdata+Tsetup-Tth。因此看出来当 Tth 为

正时钟偏斜时,可以改善时序,有利于满足建立时间。

解决建立时间和保持时间不满足的情况

由上面推导的不等式,我们可以得出结论:

1.建立时间不满足

当建立时间不满足时,即Tsetup值要大于实际的T +Tskew - Tdata - Tco,为了满足建立时间:

可以通过改进工艺,采取具有更小的Tsetup值的芯片;

采用延迟更低的触发器,降低Tck2q;

增大时钟周期Tcycle和时钟偏斜Tskew,但这会降低电路的性能;

尽量减小两个触发器之间的组合逻辑电路的使用,从而降低Tck2q。

2.保持时间不满足

当保持时间不满足时,也就是Thold要小于Tdp + Tck2q,可以通过:

理论上,可以增加Tdp和Tck2q来解决,也就是增加触发器的D端到Q端的延时,以及两级触发器之间的组合逻辑电路部

分。

目前大部分芯片的Thold时间都可以做到0ns。所以当保持时间不满足时,通常采用的做法是在传输路径上插入buffer,

在不影响逻辑功能前提下,只具有增加延迟的作用。

以上是关于关于建立时间与保持时间的主要内容,如果未能解决你的问题,请参考以下文章