9.2-控制单元CU的功能(学习笔记)

Posted PacosonSWJTU

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了9.2-控制单元CU的功能(学习笔记)相关的知识,希望对你有一定的参考价值。

【README】

本文总结自bilibili《计算机组成原理(哈工大刘宏伟)》的视频讲解,非常棒,墙裂推荐;

【1】CU功能(CPU内部不采用总线方式)

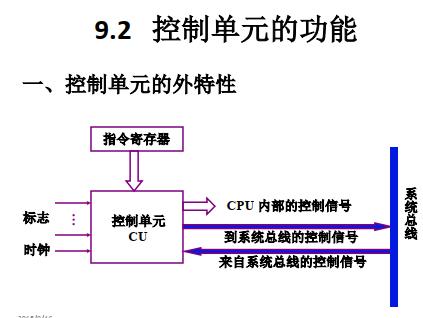

控制单元的功能: CU发出各种控制命令或微指令,控制整个计算机系统,包括cpu内部的各个部件,能够协调、稳定、正确、连续的运行;

【1.1】CU输入与输出信号

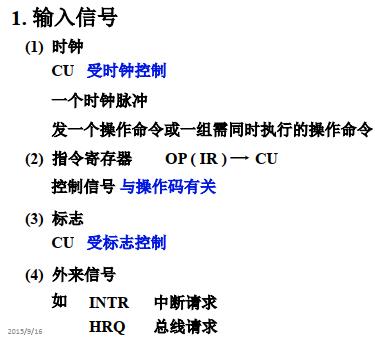

1)控制单元CU的输入信号

- 指令寄存器IR的操作码部分,送入CU,以便译码;

- 时钟信号:CU微操作命令在时钟信号的控制下,在指定的时间点被发出;

一个时钟脉冲,发一个操作命令或一组需要同时执行的操作命令; - 各种标志;如上一条指令运行结果的标志,就是本条指令是否发生跳转的依据;

- 来自系统总线的控制信号:CPu外部的控制信号可以进入控制单元;

2)控制单元CU的输出信号

2.1 )CPU内部的控制信号

- 如 寄存器间进行数据传输;

- 如 下一条指令地址进行修改; pc+1 –> pc ;

- 如 运算器的算术运算和逻辑运算,相应的控制信号也是由 cu发出的;

2.2)送到控制总线的信号

- 如存储器读写命令 ;

【1.2】控制信号举例

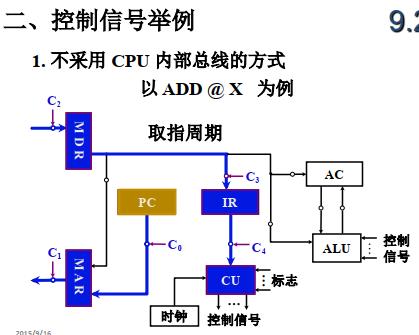

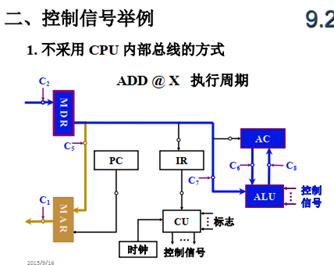

在不采用cpu内部总线的方式下的执行过程,其中各寄存器含义:

- PC,存储下一条指令的地址;

- IR,根据pc的地址,从存储器取出指令放入IR指令寄存器;

- CU,把IR中的指令送入CU进行译码;

- 时钟:时钟信号作为输入,以控制CU控制器发送各种控制信号;控制信号还会控制ALU进行算术或逻辑运算;

- AC:即ACC寄存器的简写,ACC是累加器;

- ALU:运算器;

- MAR:主存地址寄存器;

- MDR:主存数据寄存器;

【写在前面】ADD @X 指令介绍

这条指令完成的是一个加法操作;

这个加法是把内存单元X中的数据和AC寄存器中的数据在控制信号的作用下做加法操作,加法操作由ALU来完成,并且加法结果保存到AC寄存器(ACC寄存器或累加器)中;

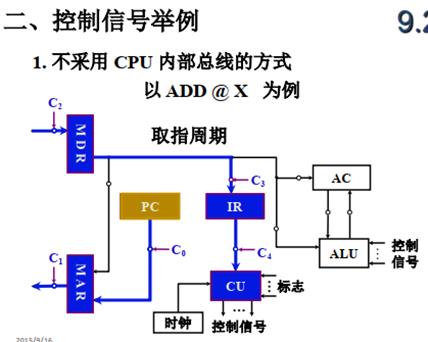

1)以 ADD @X 命令的取指周期(注意是取指周期)为例:操作发起从pc发起;

- 步骤1:控制电路C0 把pc的内容送入MAR;

- 步骤2:MAR 经过控制电路C1把地址送入主存;通知CU向主存发送读控制命令;

- 步骤3:从主存读取的命令通过控制电路C2送入MDR;

- 步骤4: 再由MDR经过控制电路c3送入IR寄存器;至此取指操作结束;

- 步骤5:IR指令的操作码部分通过c4控制电路送入CU进行译码,;

- 步骤6:PC加1,以便于下一次执行指令;

小结:以上5个控制信号c0~c5都是CU产生的;

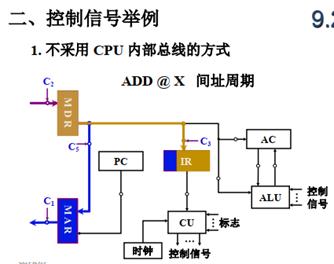

2)下面看下间址周期,执行周期中的控制信号

指令执行周期的控制信号的控制过程:

起始状态:操作数的地址在MDR;

- 步骤1:把MDR(操作数地址)通过C5控制信号送入到MAR;

- 步骤2:MAR中的地址通过c1控制信号(控制门)送入到地址线,地址线送入存储器;

- 步骤3:CU发出读操作命令;

- 步骤4:从主存读入的数据,通过C2控制门送入MDR;至此,两个操作数都在cpu的寄存器中了;被加数保存在AC,加数在MDR中;

- 步骤5:C6和C7两个控制门打开,把操作数送入ALU;

- 步骤6:CU发出加法控制信号;并把运算结果通过C8控制门送入到AC寄存器;至此,执行过程就结束了;

注意: 以上方式,是cpu内部不采用内部总线的方式;

【2】控制单元的功能(CPU内部采用总线的方式)

注意:cpu内部总线不同于系统总线;

- cpu内部总线是CPU(包括ALU,CU)连接内部组件(如寄存器)用的;

- 而系统总线包括 地址总线,数据总线,控制总线,是cpu连接cpu外部设备用的,如主存,磁盘等;

(为了对比,上图是不采用CPU内部总线方式)

(上图是采用CPU内部总线方式)

【背景介绍】

Cpu中,由 PC,MAR,IR,进行取指令操作,并放入MDR中;

在控制单元的作用下,我们可以进行操作;

时钟信号作为控制单元CU的输入,经过控制单元CU译码后,产生各种类型的控制信号,来控制cpu内部与外部的操作;

AC寄存器(ACC寄存器);

ALU运算器:运算器要有多种类型的控制信号;控制它做相应的算术运算或逻辑运算;

ALU:是一个组合电路,为了能够保存两个操作数和计算结果,在alu的两个输入端需要加上寄存器,在输出端也要加上寄存器;输入时,ac可以作为其中一个寄存器,另一个输入寄存器是Y;在控制信号的作用下,把ac和y寄存器的操作数送入ALU进行相加,并把结果送入Z寄存器;

以上部件,都是离散的部件;在刚刚cpu内部不采用总线的结构下,分别有线路进行连接;

0)引入CPU内部总线目的:为了简化cpu结构,简化设计,假设cpu内部采用总线方式,这些离散部件是连接到CPU内部总线上的;

1)下面在cpu内部采用总线结构下,间址加法指令(ADD @X)的取指步骤:

- 步骤1:pc寄存器的值被送入cpu内部总线;

- 步骤2:通过mar输入控制信号把pc的值送给mar;这时mar保存的就是下一条要执行指令的地址(即加法指令的地址);

- 步骤3:MAR把指令地址送入地址线;

- 步骤4:CU发出读命令到控制总线,控制总线送给存储器;

- 步骤5:从主存读出来的指令被送入到数据线,进而送入到MDR寄存器中;(这时,MDR存储了间接寻址的加法指令)

- 步骤6:MDR存储的加法指令,通过控制信号送入cpu内部总线,接着送入到IR寄存器;(这时,IR指令寄存器就保存了要执行的加法指令)

- 步骤7:IR中的操作码部分送入CU进行译码;

- 步骤8:PC加1(以指出下一条要执行指令的地址);

以上控制信号(IRi,PCo, MARi, MDRo, PCo),都是由CU在时钟信号的控制下产生的控制信号(i输入,o输出); 这些控制信号间,是有先后关系的;

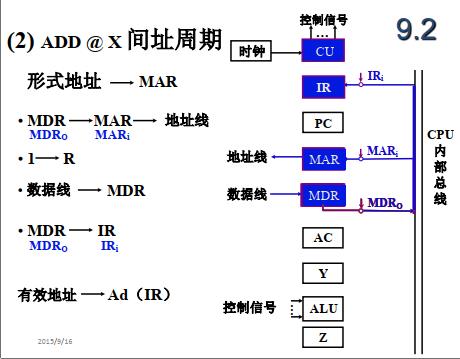

2)ADD @X 间址周期:

指令中的操作数形式地址,送入MAR;从内存中读出该形式地址内存单元对应的操作数有效地址,并送入IR寄存器的操作数地址部分(真实地址);

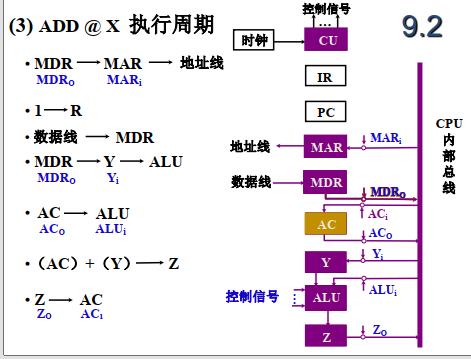

3)CPU采用内部总线方式下的ADD @X 执行周期步骤:

- 步骤1:MDR把操作数有效地址(真实地址)送入cpu内部总线;进而送入到MAR;

- 步骤2:MAR把操作数地址送入地址线;

- 步骤3:CU发出读信号到控制线,进而送入存储器;

- 步骤4:读出来的操作数通过数据总线送入MDR;(参加加法运算的另一个操作数保存在MDR中)

- 步骤5: MDR通过MDRo输出控制信号,把操作数送入cpu内部总线;CPU内部总线通过寄存器Y的输入信号,把操作数送入到Y寄存器;

- 步骤6:寄存器Y的数据送入ALU;

- 步骤7:寄存器AC通过ACo输出控制信号,把另一个操作数送入CPU内部总线,进而送入到ALU中;

- 步骤8:在各种控制信号下,ALU做加法操作;(AC)+(Y)的结果存入Z寄存器中;

- 步骤9:AC控制器在ACo控制信号下,把结果送入cpu内部总线,进而通过ACi控制信号送入AC寄存器:(至此,加法操作完成)

小结:以上蓝色部分都是控制信号,这些控制信号都是由CU发出的,控制信号间是有顺序的;

【3】多级时序系统

为了解释指令的执行,它的解释所花的时间,我们叫做指令周期;

指令周期分为: 取指周期,间址周期,执行周期,中断周期;

【3.1】机器周期

1)定义:完成一个基本操作所需要的时间,如取指令,存储器读,存储器写;通常以访存时间为基准;因为指令最耗时的操作就是访存操作;

2)取指周期的过程(微操作)包括:

| 1,Pc值送入MAR; 2,MAR送入主存; 3,CU发出读控制信号给主存; 4,从主存读取指令到MDR,进而送入IR; 5,IR送入到CU进行译码; 6,PC加1; 以上操作都是有先后顺序的;以上这些操作都是微操作,有先后顺序的; |

在机器周期内部,也需要有多个时钟周期,由时钟来控制微操作的先后顺序;

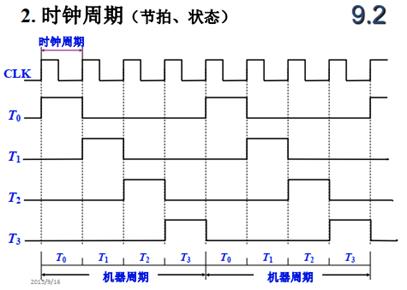

【3.2】时钟周期(节拍,状态)

1)定义:控制计算机操作的最小单位时间(注意是控制);1个时钟周期,可以做1个或若干个微操作(若微操作可以并行执行);

2)机器周期和时钟周期关系:

把一个机器周期分为若干个时间相等的时间段(时钟周期,或节拍,或状态);

由这些时钟周期控制在一个机器周期内部的这些微操作,它们在时间上的先后顺序;

3)小结:

- 机器周期指的是:完成一个基本操作的所需要时间;如取指令;

- 时钟周期指的是:控制计算机操作的最小单位时间(1个时钟周期可以做1个或多个微操作);

- 两者关系:1个机器周期划分为多个时钟周期;或多个时钟周期组成1个机器周期;

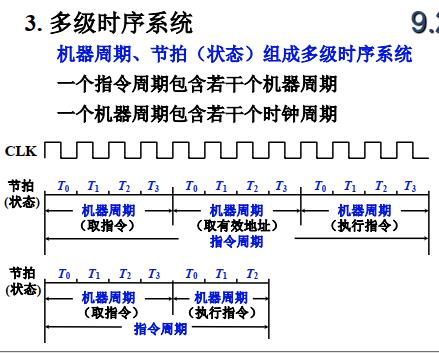

【3.3】多级时序系统

多级时序系统:包括了指令周期,机器周期、节拍(时钟周期)3个部分;

一个指令周期包含若干个机器周期;

一个机器周期包含若干个时钟周期;

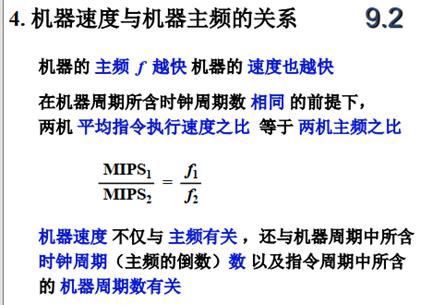

【3.4】机器速度与主频间的关系

补充:

在不采用指令流水线技术前提下,且一个指令周期包含多个机器周期且一个机器周期包含多个时钟周期,则机器速度和主频成正比关系;

在采用流水线技术前提下,即便上述条件相等,但速度就不一定了

【4】控制方式

控制方式定义:产生不同微操作命令序列所用的时序控制方式;

【4.1】同步控制方式

1)同步控制方式:每一个微操作都是在定宽,定距(统一基准时标)的时钟信号的控制之下;

- 采用定长的机器周期:每个机器周期含有相同的节拍数;(如取指令需要4个时钟周期,而执行指令需要1个时钟周期,但被划分了4个时钟周期,这就造成了浪费)

- 不定长的机器周期:机器周期内部的节拍数(时钟周期)可以不等;

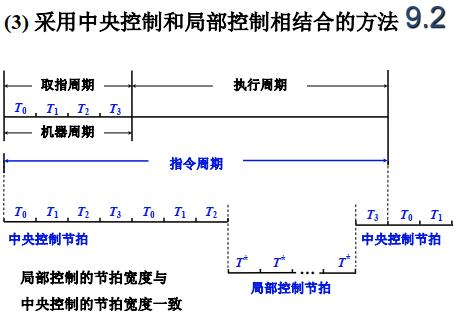

- 中央控制和局部控制相结合的方法:一部分由中央控制节拍控制,而另一部分由局部控制方式来控制;

【4.2】 异步控制方式(没有定宽定距的基准时钟)

以上是关于9.2-控制单元CU的功能(学习笔记)的主要内容,如果未能解决你的问题,请参考以下文章