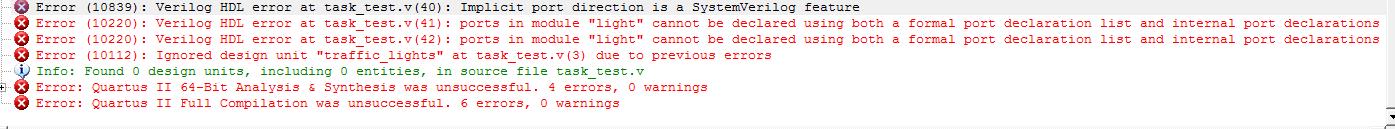

Verilog 写task函数时候出现下面的报错

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog 写task函数时候出现下面的报错相关的知识,希望对你有一定的参考价值。

//`timescale 1 ps/ 1 ps

module traffic_lights(

clk,

red,

amber,

green

);

input clk;

output red;

output amber;

output green;

reg red;

reg amber;

reg green;

////dedine the parameter

parameter on=1,

off=0,

red_tics=350,

amber_tics=30,

green_tics=200;

//initial

initial red=off;

initial arber=off;

initial green=off;

///the main progress

always begin

red=on; //打开

light(red,red_tics); //等待

green=on;

light(green,green_tics);

amber=on;

light(amber,amber_tics);

end //类似C语言的函数调用

////define task

task light(color,tics); //定义交通灯的开启时间task

output color; //输出 控制信号

input [31:0] tics; //输入 延时时钟

begin

repeat (tics) @(posedge clock);

color=off;

end

endtask

//// produce the clock

// always @ (posedge clk)

// begin

endmodule

正确如下:

task light;

output color;

input [31:0] tics;

begin

repeat (tics) @(posedge clock);

end

endtask 参考技术B task 应该不能被综合的吧,只能仿真用的吧本回答被提问者采纳

怎么用verilog编写PWM,形成下面的波形,实际上就是三角波....

参考技术A 用一个计数器,一个控制按键,在原理上就是按钮按一次,计数器的计数范围变化。module PWM (

button,

pwm,

clk );

input button ;

output reg pwm ;

input clk ;

reg button_r ;

reg [7:0]delay;//按键消除抖动用延时

reg [7:0]count; //计数器

reg [7:0]temp; //脉宽设置

always@(posedge clk )

if(!button )

button_r<=1'b0;

else

if(delay==8'h00)

button_r<=1'b1;

else

delay<=delay+1'b1;

always@(posedge clk,negedge button_r)

if(!button_r)

temp<=temp+8'h10;

else

if(count==temp)

begin

count<=8'h0;

pwm<=~pwm;

end

else

count<=count+1'b1;

endmodule

差不多就这样,原理不变本回答被提问者采纳 参考技术B 用计数器计数,控制波形输出。电平越长,计数值越大,电平越短,计数值越小。

以上是关于Verilog 写task函数时候出现下面的报错的主要内容,如果未能解决你的问题,请参考以下文章