altium designer (Protel DXP)中,位于不同高度的元器件重叠放置出现空间干涉,如何解决?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了altium designer (Protel DXP)中,位于不同高度的元器件重叠放置出现空间干涉,如何解决?相关的知识,希望对你有一定的参考价值。

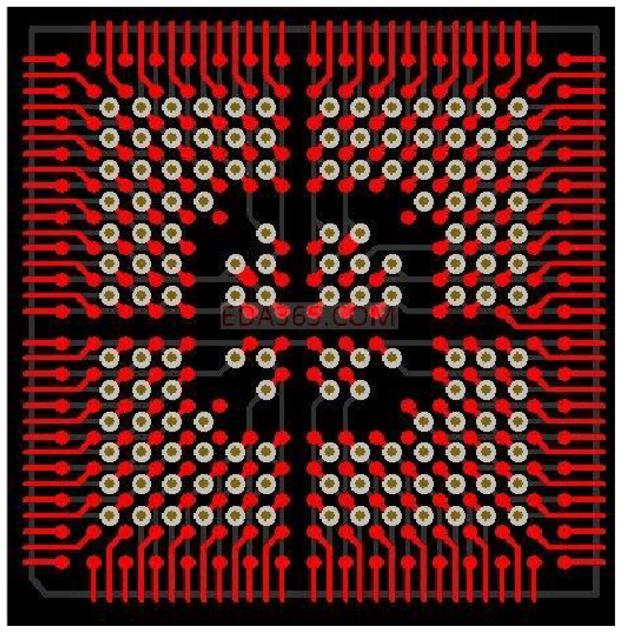

我的板子上需要在顶层重叠放置两层元件,一个是由主板上的排针和铜柱连接固定、位于主板上方一定高度的小电路板,其他的贴片元件位于这块悬浮的电路板下方的主板上。画PCB的时候,自然就报出这些元件空间上相互干涉了。我想知道应该怎样解决这个问题,在制作封装的时候只找到了关于元器件总体高度的设置,没有看到关于器件悬浮高度的设置。希望有高手能帮我解决这个问题。

类似于“在规则设置里面把ComponentClearance忽略掉”这样的建议就不要提了,我还是希望在其他地方出错的时候得到警告的。因为在这条规则中看到有“最小垂直间隙”这一项,所以我认为软件应该支持悬浮的器件。

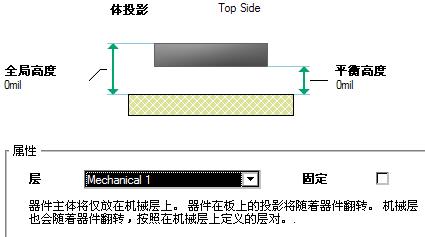

刚发现在优先选项-PCB Editor-Default-Component Body中有一个“平衡高度”的设置。可能跟我遇到的问题有关。不知道能不能对单个元件设置这一参数,使得下方的空间可以放置其他元件。

你这不是元件重叠问题,而是两块PCB,能叠在一起画吗?

既然是两块板,分开画就是了,做拼板在一起也行追问

没错,是两块PCB,但我只画下面那块,上面那块是一个现成嵌入式的模块,通过排针插在下面那块板上,同时四个角还需要螺钉固定。所以我给嵌入式模块制作的封装就有整个模块那么大,这就使得原来下面那块板上的元件和嵌入式模块的封装干涉了。所以我想知道怎么解决这个干涉的问题。如果不理会确实也可以,只是检查错误时会出现很多没用的警告。

追答将这个嵌入式模块的封装定好位后打散Tools_Convert_Explode component to Free ...,焊盘及丝印都存在(如果需要画完板再放回一个在原处就可以)

追问嗯,你这个方式确实是目前我找到的最好的方法了。刚刚补充了一下问题,如果还没人能给出合适的答案的话,分就给你啦。谢谢。

本回答被提问者采纳Altium Designer (AD) 中规则的部分讲解

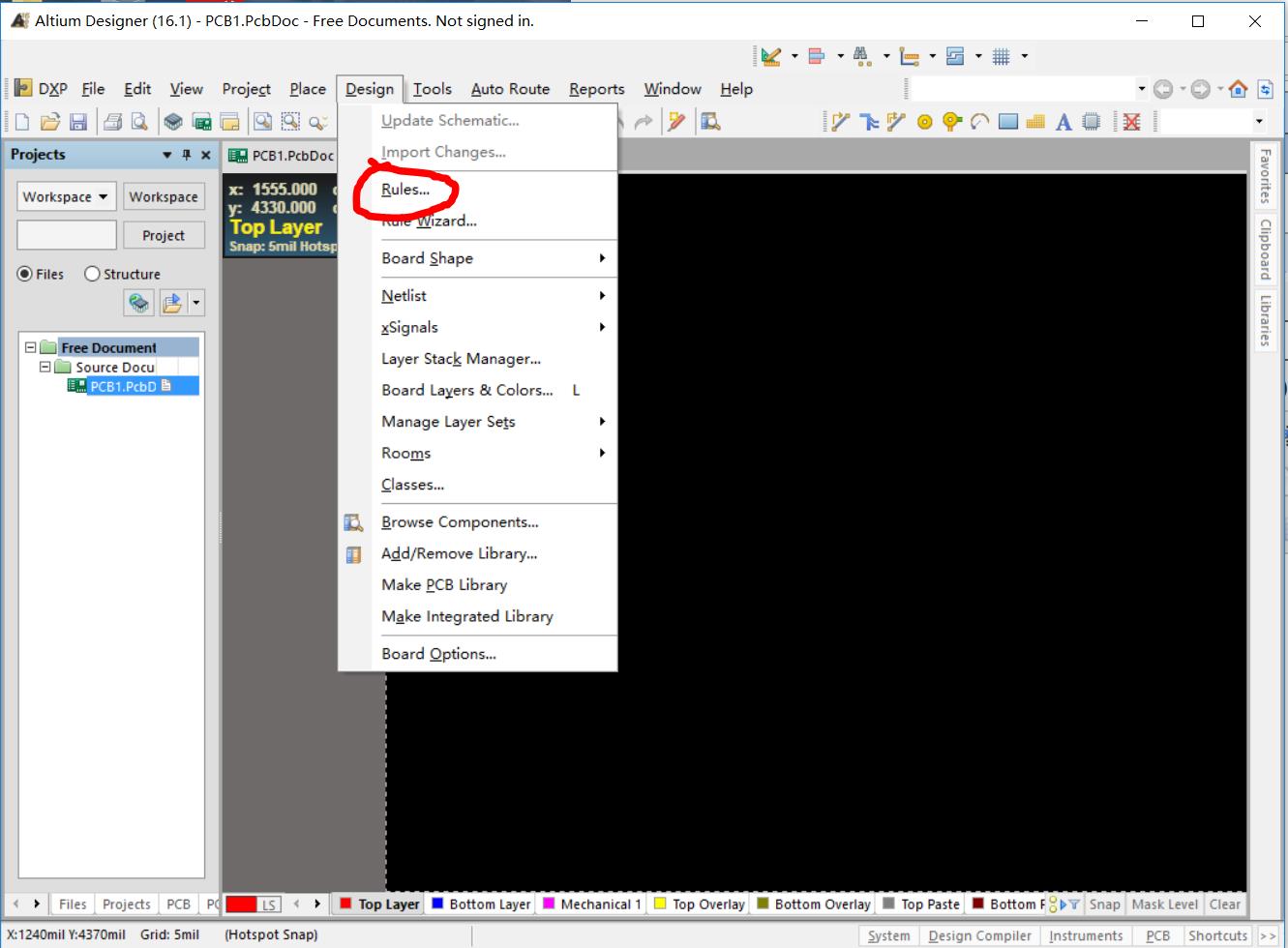

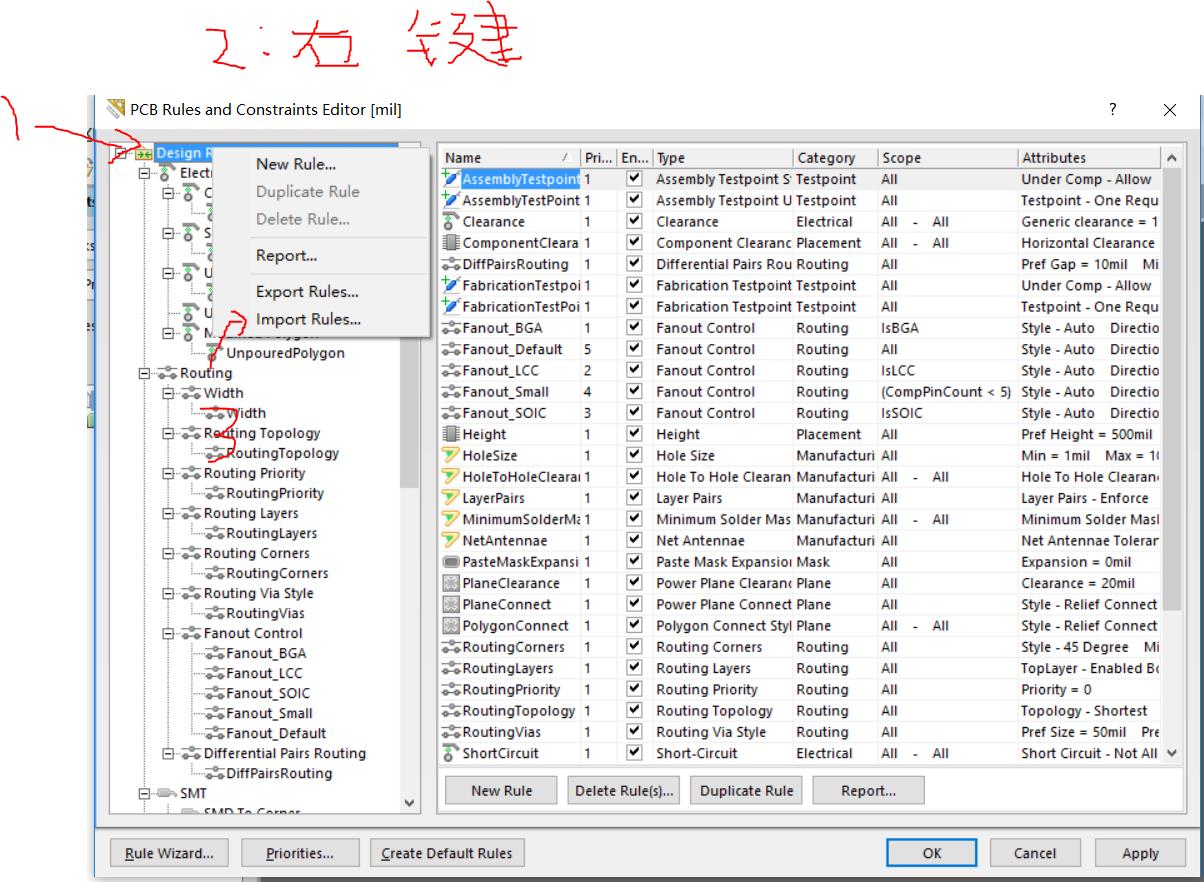

当创建好PCB时,选择 Design - Rules 即可进行规则的设置,也可以直接利用快捷键D-R(多利用快捷键,可以有效的提高设计效率,)

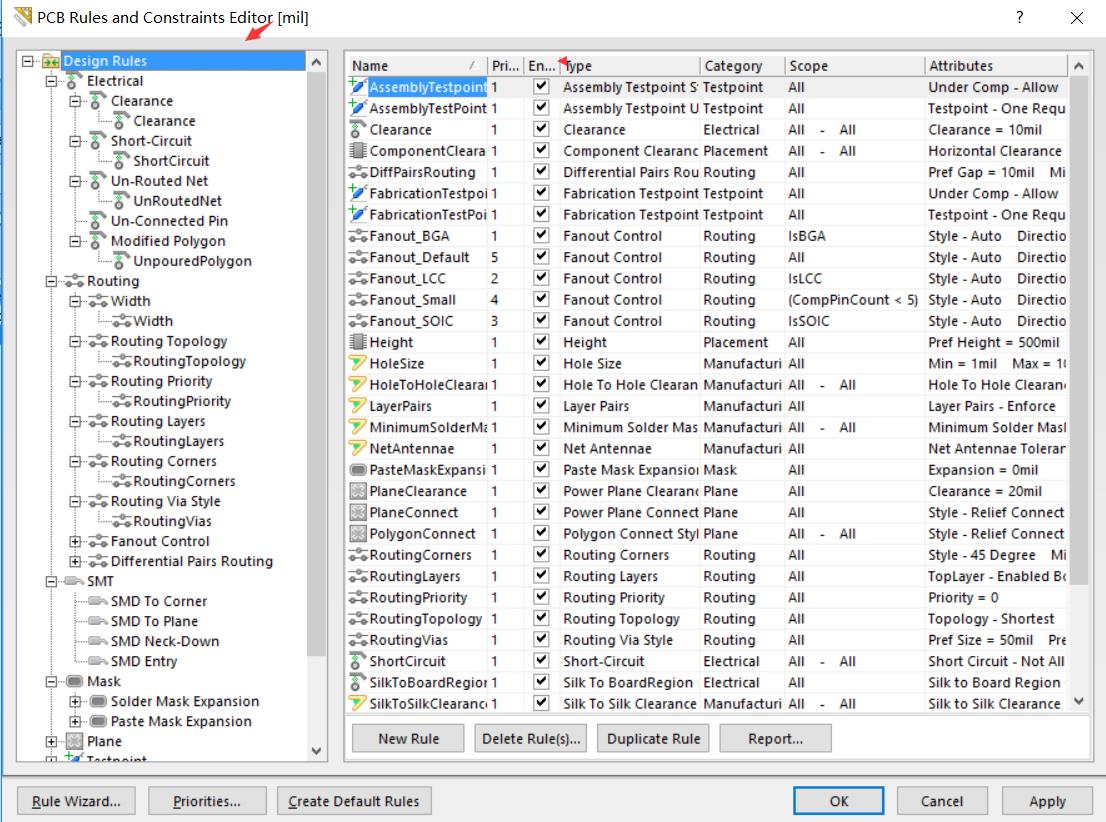

这个是规则的总界面,熟练以后可以直接从这里进行修改,很便捷

1 先从Electrical(电气方面)开始讲起

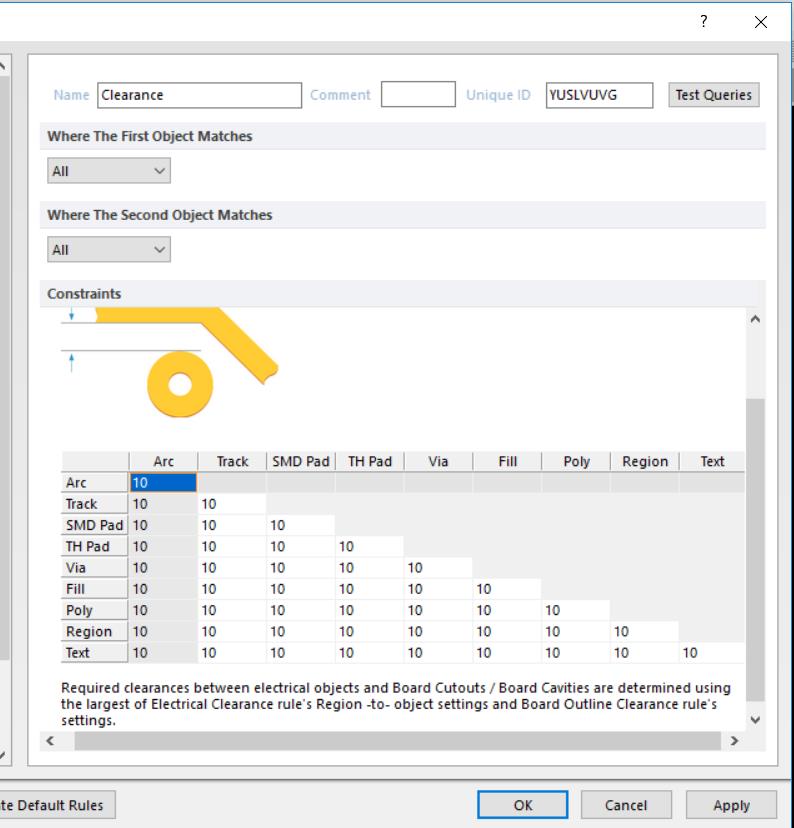

Clearance(间隙)

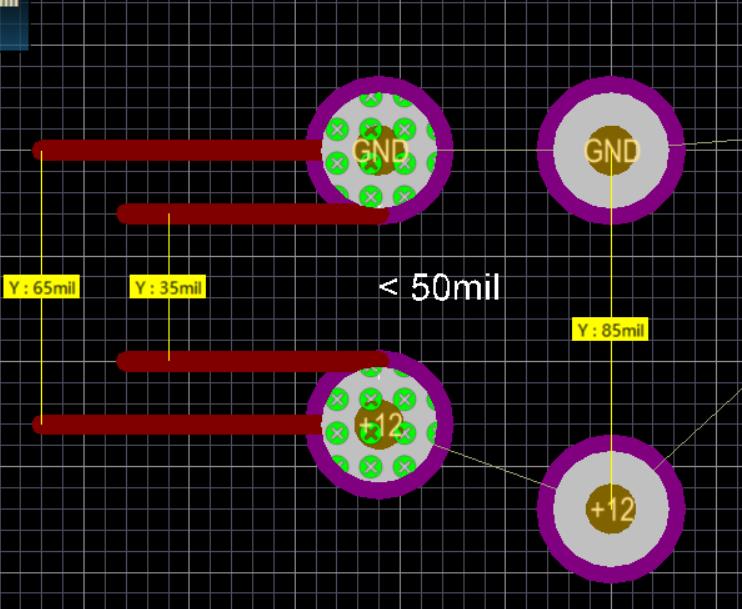

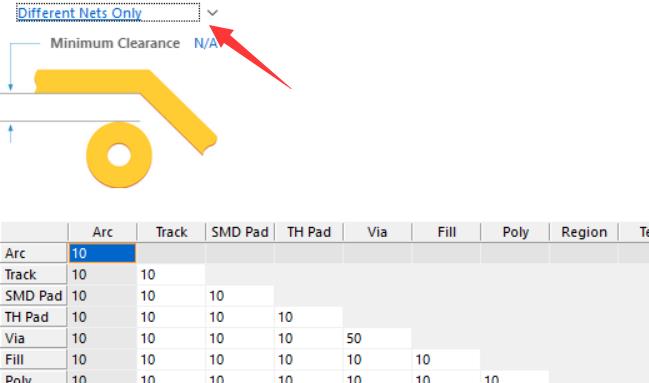

这个表格我们以下面的设置为例,参考它的设置,将Via-Via之间的间距设置为50mil

在PCB中

注,同网络之间不报错是因为我在设置时选择了只应用不同的网络

在图中,当边缘间距小于50mil,即是图中35mil<小于50mil便出现了错误提示。

Arc

Track(导线)

SMD Pad (贴片式焊盘) ,右图是顶层的一个焊盘

TH Pad(通孔焊盘)

3D图中是有穿透的孔

Via(过孔)

Fill(填充)

![]()

Poly(覆铜)

![]()

Region(区域)

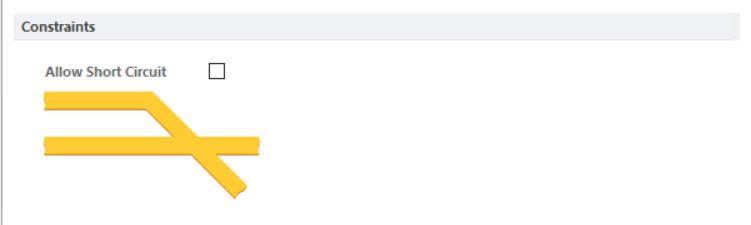

ShortCircuit(短路)----勾上图中选择则允许这种情况出现,一般都不勾选

Un-Routed Net(未连接的网络)--默认就可以了,

Un-poured Polygon(未覆铜区域)--默认就好

Routing(布线规则设置)

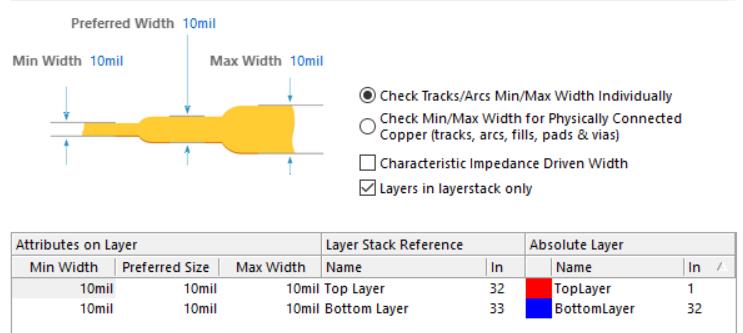

width(线的宽度)

Min width (最小线宽) Preferred Width(首选线宽) Max Width(最大线宽)主要就这三个,其他的选项一般不用改

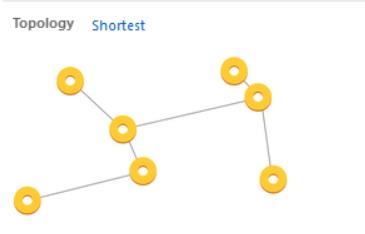

Routing Topology(布线拓扑规则) ----即系统的连线方式,shortest是最短连接方式,默认为此就好

Routing Priority(布线优先级)--主要用于设置自动布线的时候,不过一般都是采用手动布线,一般用不到

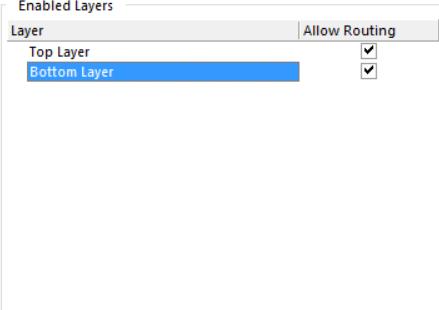

Routing Layers(布线图规则)--设置哪些层可以布线

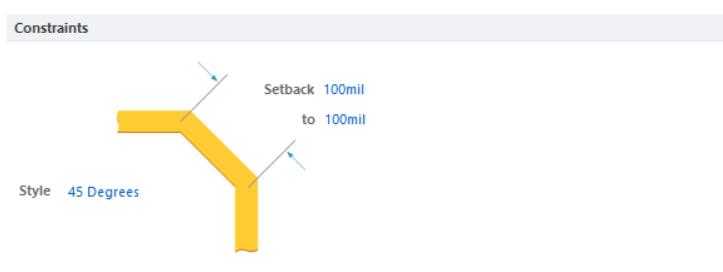

Routing Corners(拐角)--设置拐角的大小,因为一般都不会走直角,所以最好设置一定的角度

Routing Via Style(设置过孔大小)---也分为最大最小和首选

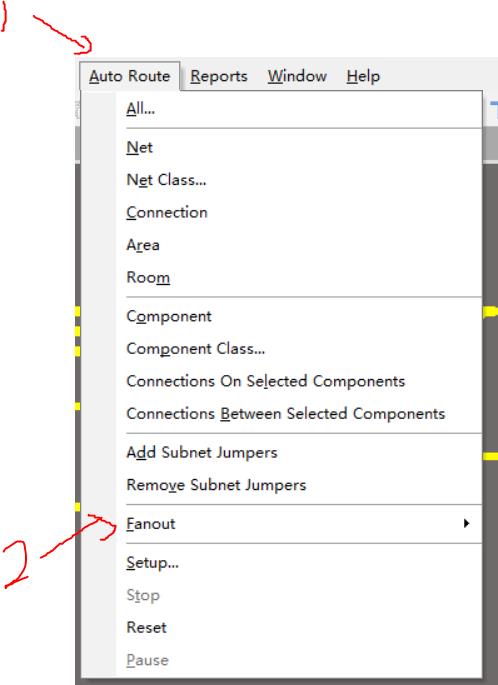

Fatout Contrl(扇出布线) 我还没试过,不过据说是很好用的,它可以将底下有的几种封装类型将网络引出方便连接,例如

位置在

Differential Pairs Routing(利用差分对布线) ---高频信号中需要利用等长线来避免造成重大错误

SMT(表贴焊盘规则)

SMD To Corner:SMD焊盘与导线拐角处最小间距规则

SMD To Plane:SMD焊盘与电源层过孔最小间距规则

SMD Neck Down:SMD焊盘颈缩率规则

Mask(阻焊层规则)我还没用过,暂时不懂

Solder Mask Expansion:阻焊层收缩量规则

Paste Mask Expansion:助焊层收缩量规则

Plane(电源层规则)

PlaneConnect 电源层连接类型规则

PlaneClearance 电源层安全间距规则

PolygonConnect 焊盘与覆铜连接类型规则

之后的几个我没接触过,接触了解以后会补充

这个是我之前从网上找到的一个规则模板,可能有些地方不符现在的制作水平,但很多都可以参考

https://pan.baidu.com/s/16WA-eXXwm9AnHzPSbIe52w

导入规则的方法

以上是关于altium designer (Protel DXP)中,位于不同高度的元器件重叠放置出现空间干涉,如何解决?的主要内容,如果未能解决你的问题,请参考以下文章

Altium Designer 中怎么不直接用线相连,将两个引脚连在一起?

Altium Designer PCB多个封装LIB文件合并成一个 求具体操作我有点笨

Altium Designer许可告急,这样的许可优化方案才是最优选择!!!