跨时钟域CDC电路设计

Posted Per_HR7

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了跨时钟域CDC电路设计相关的知识,希望对你有一定的参考价值。

跨时钟域CDC电路设计

同步时钟和异步时钟的定义

- 同步时钟—能够明确定义多个时钟间如下关系的时钟源—站在EDA工具的角度

- 时钟频率

- 时钟高电平/低电平的持续时间

- 各个时钟的相位(第一个上升沿的方向和时间)

- 时钟的输入latency

- 异步时钟

- 不能明确定义多个时钟间以上关系的时钟源

亚稳态(metastable)产生与问题

-

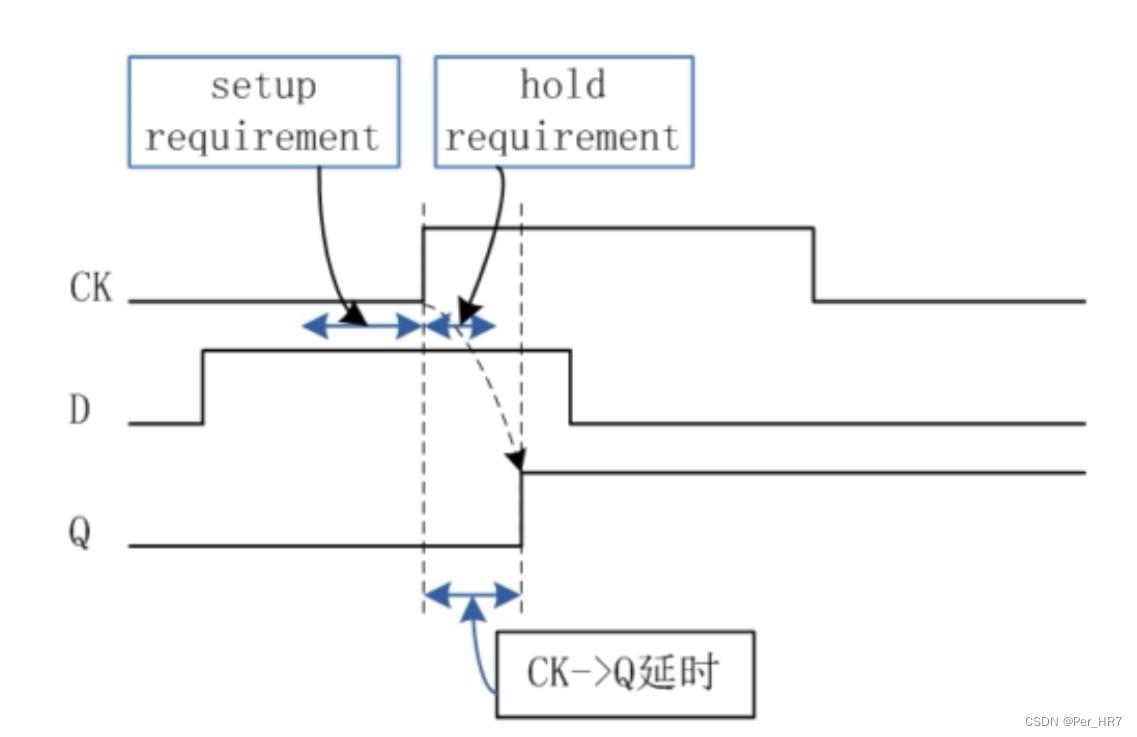

DFF的setup/hold需要满足特定要求

-

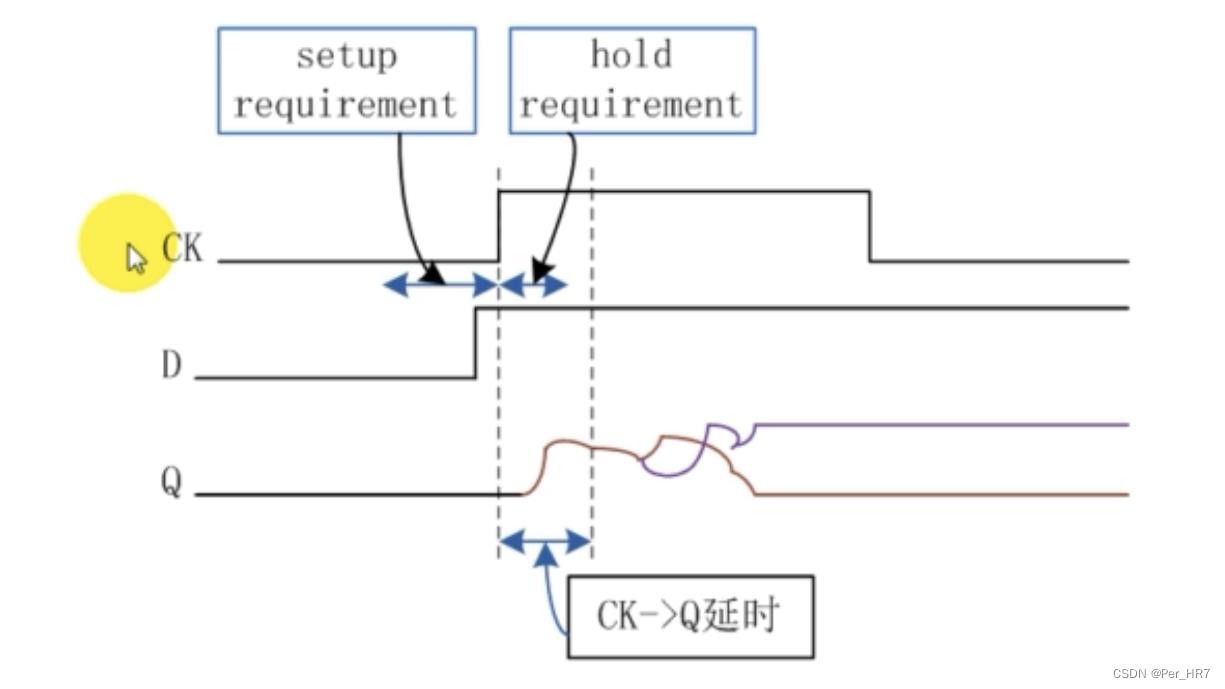

DFF的setup/hold不满足特定需求—存在Q端输出不确定的情况且ck->Q更长

-

metastable导致的问题

- DFF的输出端不稳定,可能是1/0

- 比cell-library里面定义的更长的ck->Q延时

-

靠跨时钟域同步电路处理亚稳态问题

-

跨时钟处理目标—百分百确保数据(事件)在跨时钟域时的数据完整性

- 数据的值不能错

- 数据的顺序不能错

- 数据的个数不能错

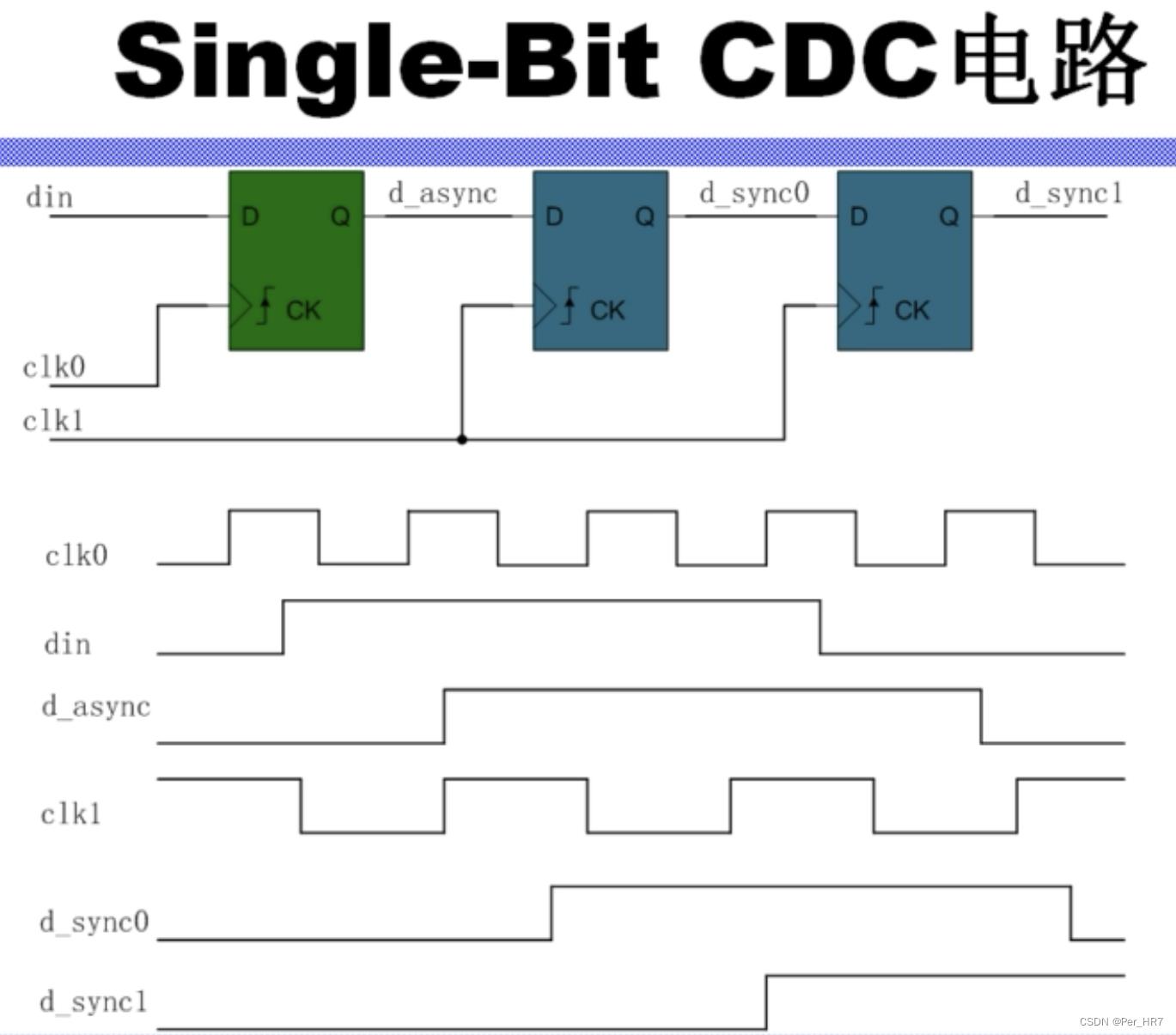

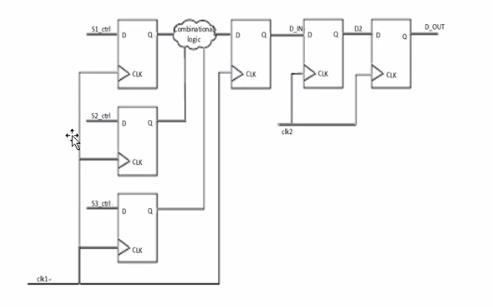

Single-bit信号跨时钟域电路结构

-

这是一个经典的跨时钟域的设计,采用的方式是打两拍

-

解决问题的思路

- 由于亚稳态造成的这种存在Q端输出不确定的情况且ck->Q更长的现象,我们不妨可以让输入持续时间更长来保证拥有足够的setup/hold时间,同时再加上ck->Q的最长时间,这两部分之和的时间作为我们跨时钟域的后级时钟clk1,这样就可以保证两拍正确解决该问题

- 这样可以百分百保证解决相关问题

-

保证百分百解决亚稳态的最核心的关注问题

- din足够长,保证被第二个D触发器抓住

- 第二个D触发器的ck->Q的最长时长要小于clk1,这样就可以理解为让亚稳态恢复正常的时间是小于时钟周期的,这样就可以实现跨时钟域的正确性

-

缺点—不可预期什么时候才能同步

-

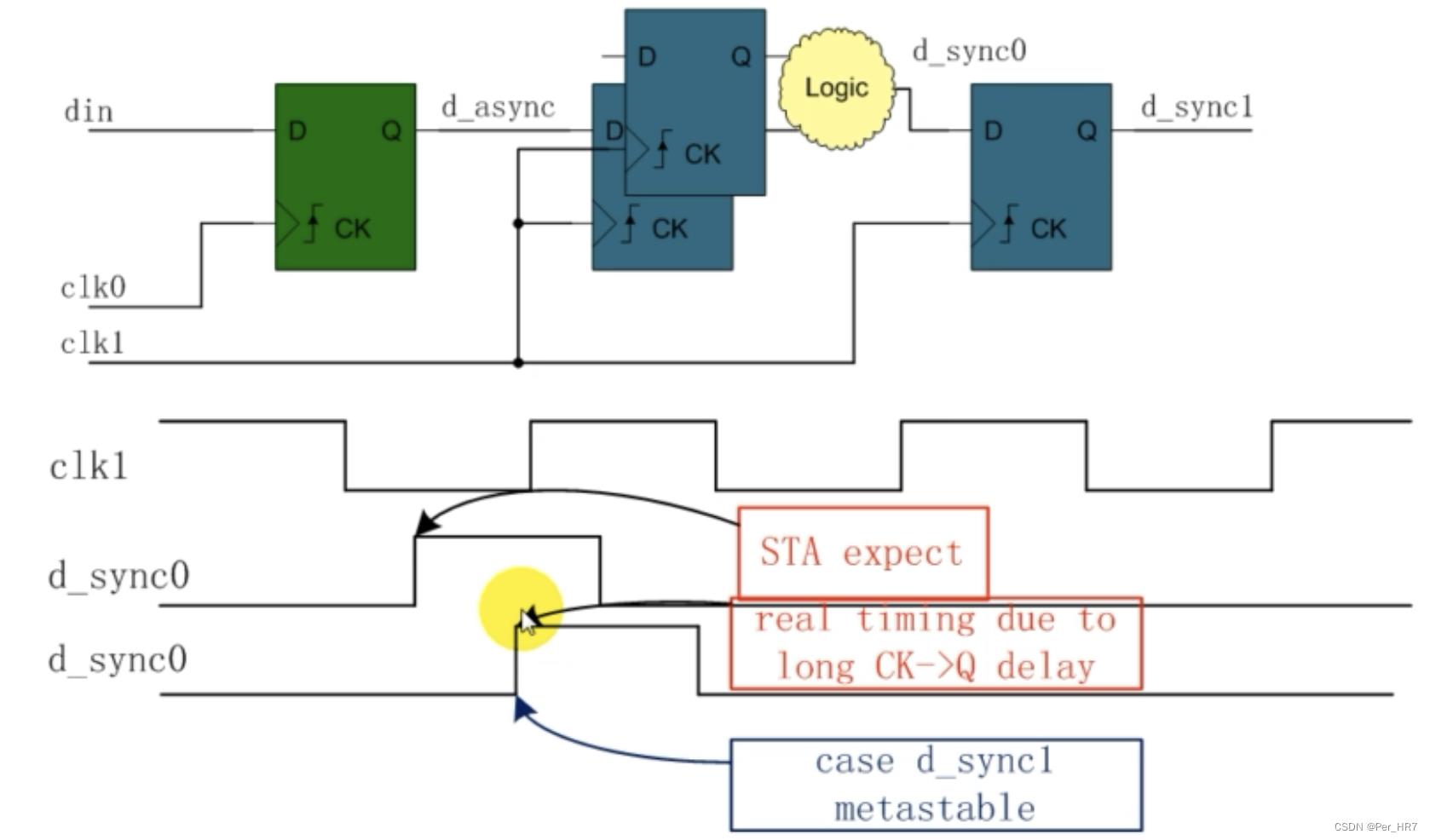

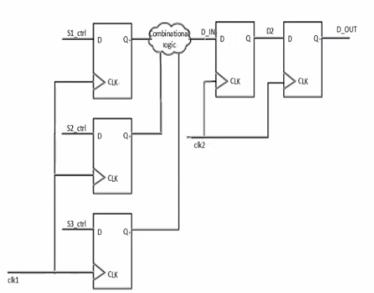

分析下图中产生错误的原因

-

组合逻辑电路中会由于布线延迟问题产生一定的延迟差异,会在逻辑建立过程中出现错误脉冲输出(竞争现象),虽然这样也不影响最后建立的结果,但如果直接接入跨时钟处理寄存器,则在如图的波形时刻刚好将错误信息读入,导致其同步错误信息。

-

解决方案

- 可以在组合逻辑后再次添加一个寄存器,保证信号是稳定采入的,而不是抖动产生的

-

分析下图错误的原因

-

在EDA软件分析过程中,并不会考虑亚稳态电路所造成的STA影响,而实际在第二级D触发器中,由于亚稳态问题,必然导致数据输出滞后性更强,因此,存在不满足最后一拍寄存器setup时间需求,导致第二拍的输出错误

-

可以加入时序约束来确定组合逻辑延时带来的影响

-

分析下图是否错误

-

该图是正确的

-

输入和第一级中不能加入组合逻辑

Multi-bit信号跨时钟域电路结构

-

存在亚稳态而后导致出现新的数据

-

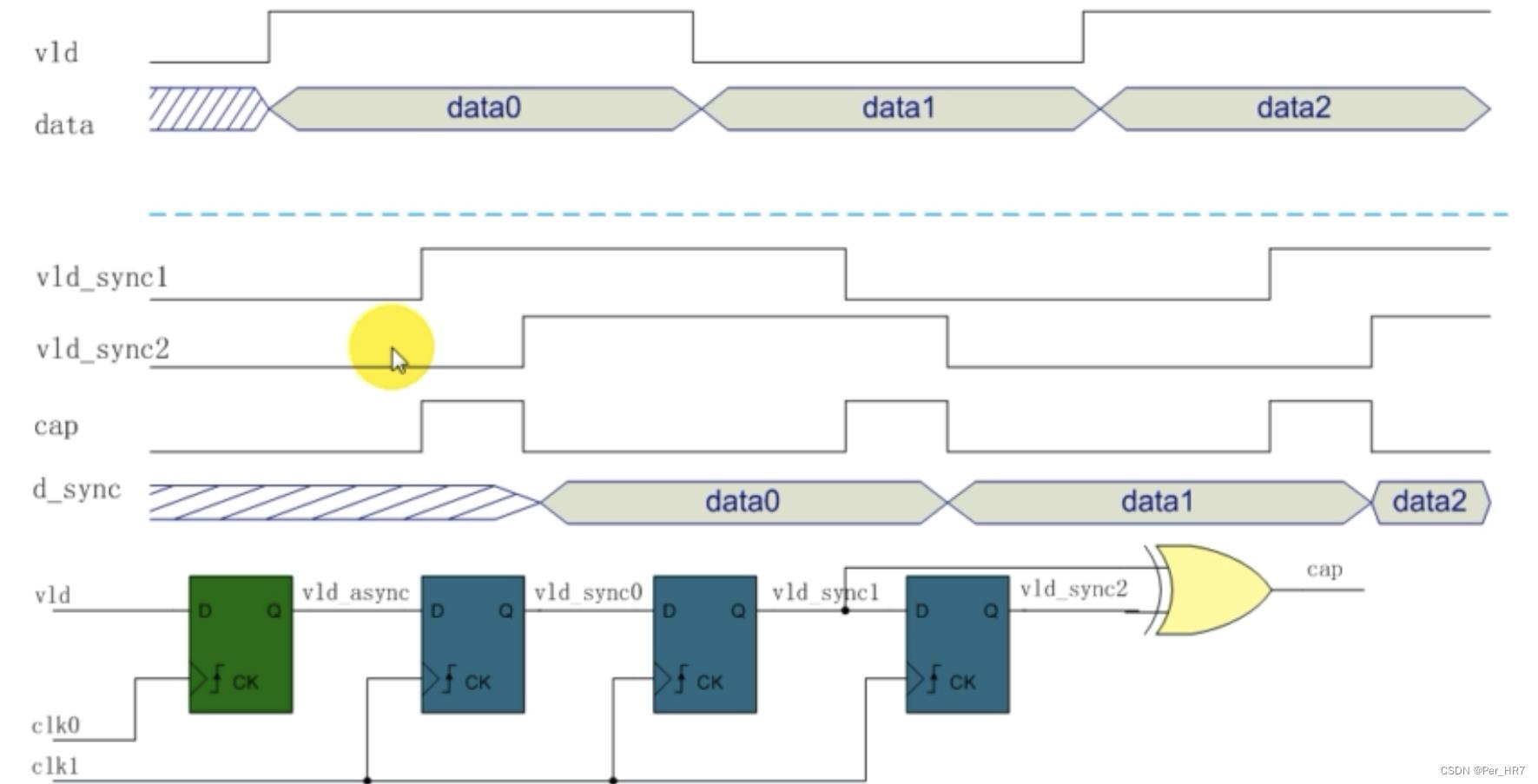

解决方案—加入guard信号

-

通过建立guard之间的高低电平的联系,进行握手保证数据进行合理的同步时间,共4次才能同步一次数据

-

缺点—同步一次需要的时间太久

-

同过对guard信号进行1bit同步后的异或输出决定是否需要同步数据

-

异或门的优势—可以检测上升沿或者下降沿

-

注意—这里的同步是对guard信号,而非data,只有guard信号同步成功后,data直接被抓获

-

这种结构是否能更快呢—采用异步FIFO结构

跨时钟域电路验证

- 通过RTL仿真不能验证CDC电路的正确性

- 因为不存在hold/setup过程

- 通过delay的gate level后仿验证CDC电路的正确性

- 信号的反转率不够

- 仿真时间不够长,无法把clk间的关系全部覆盖

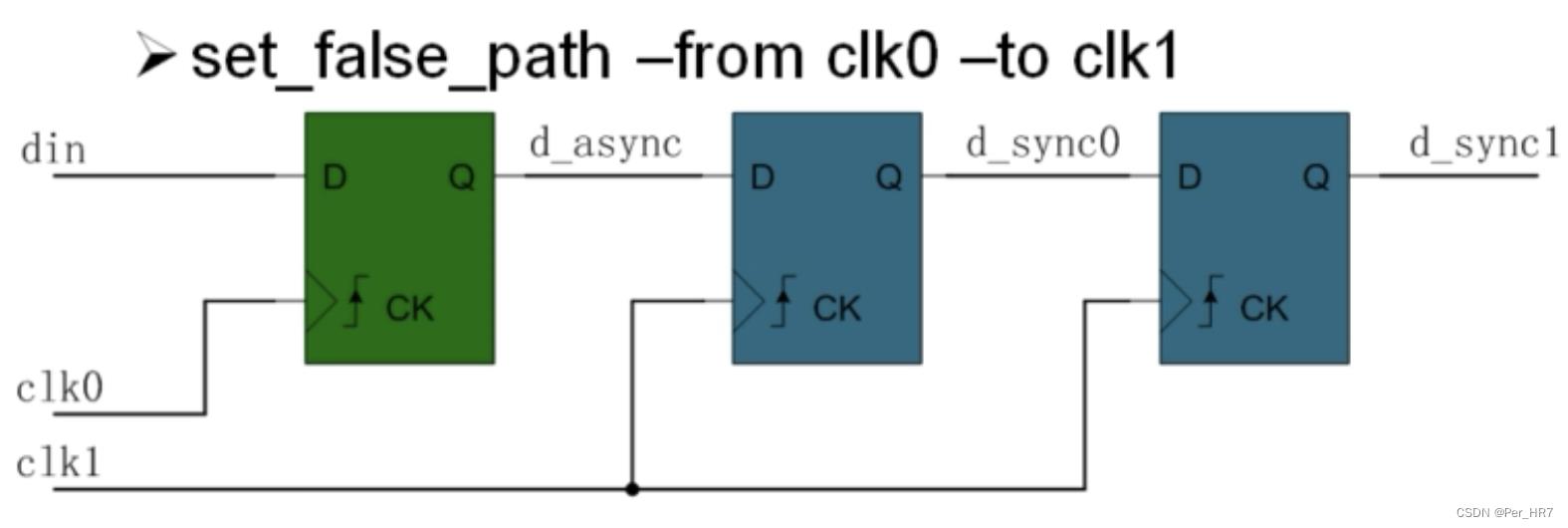

跨时钟域电路的时序约束

-

对于跨时钟域高速设计我们需要进行其他的约束设计

- 要考虑set_maximal_delay from d_sync0 to d_sync1

- 要考虑set_maximal_delay from d_sync0 to d_sync1

-

单bit高速约束

-

多bit高速约束

数字IC设计——跨时钟域篇3(单比特处理)

数字IC设计——跨时钟域篇3(单比特处理)

下面介绍常见的单比特跨时钟域的处理方法

一、慢时钟域信号同步到快时钟域的处理方法:

-

两级寄存器同步

慢时钟信号进入到更快的时钟域时(频率相差2倍以上),此时不用考虑快时钟域信号采样丢失问题,可以考虑使用两级触发器进行同步处理。 -

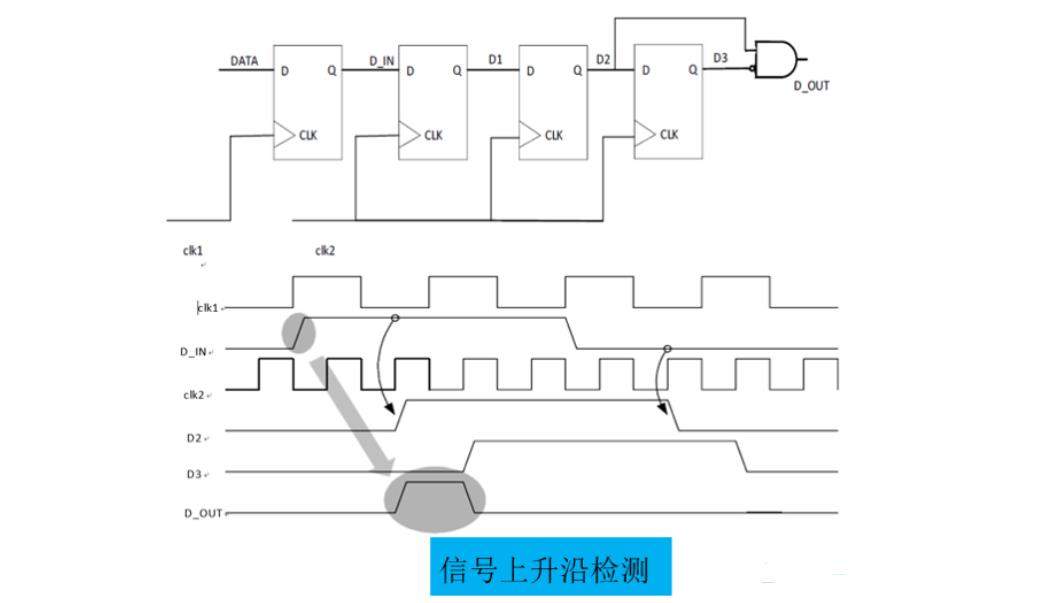

边沿检测同步器

慢时钟信号进入到更快的时钟域时(频率相差2倍以上),为了避免快时钟域多次采样到有效信号,快时钟需要对信号进行边沿检测。需要使用边沿检测同步器 -

握手处理(单比特比较少用)

当一个慢时钟域的单比特信号进入到更快的时钟域,但是两个时钟频率相差不大(频率相差2倍以下),为了避免快时钟采样丢失,需要进行握手的同步处理

二、边沿检测

之前说了如果慢时钟信号进入快时钟域信号,并且频率相差较大,那么快时钟域可以一直采样到慢时钟域信号,为了只在上升沿和下降沿或者双边沿采样到值,因此需要使用到边沿检测同步器。

之前写过一篇博客,可以参考:

FPGA基础入门篇(四) 边沿检测电路

数字IC设计verilog编写——3边沿检测

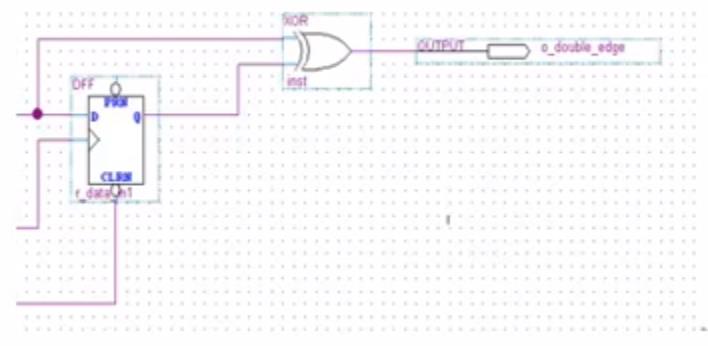

-

上升沿检测

快时钟先将输入信号进行两级同步处理,再进行一个时钟的延迟,延迟后的信号取反与同步信号做与逻辑,得到信号的上升沿。

-

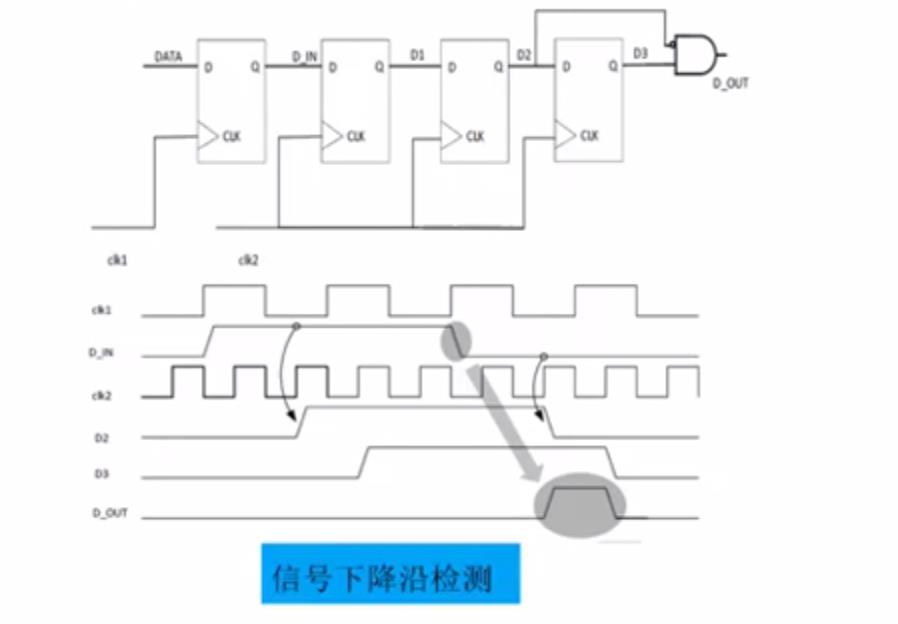

下降沿检测

快时钟先将输入信号进行两级同步处理,再进行一个时钟的延迟,延迟后的信号与取反后同步信号做与逻辑,得到脉冲信号的下降沿。

-

双沿检测

快时钟先将输入信号进行两级同步处理,再进行一个时钟的延迟,延迟后的信号与同步信号做异或逻辑,就可得到信号的双沿脉冲。

-

边沿检测的verilog RTL代码:

module edge_detect(

clk,

rstn,

signal_a,

pos_edge_flag,

neg_edge_flag,

double_edge_flag

);

input clk,rst;

input signal_a;

output pos_edge_flag, neg_edge_flag,double_edge_flag;

reg signal_reg_1,signal_reg_2,signal_reg_3;

//sync

always @(posedge clk or negedge rstn) begin

if (!rstn)

{signal_reg_3,signal_reg_2,signal_reg_1} <= 3'b000;

else

{signal_reg_3,signal_reg_2,signal_reg_1} <= {signal_reg_2,signal_reg_1,signal_a};

end

//pos_edge falg pull up

assign pos_edge_flag = signal_reg_2 & !signal_reg_3;

//neg_edge falg pull up

assign neg_edge_flag = !signal_reg_2 & signal_reg_3;

//double_edge flag

assign double_edge_flag = signal_reg_2 ^ signale_reg_3;

endmodule

说明:

在跨时钟域处理时,首先对单比特信号进行二级同步的处理得到稳定的信号,然后第三级在处理边沿检测。总共需要三拍的操作。

三、快时钟域到慢时钟域处理方法

快时钟域信号同步到慢时钟域的处理方法:

-

电平拓展

如果已知慢时钟域的时钟频率,可以考虑将快时钟域的信号进行电平扩展,使得足以被慢时钟域采样。 -

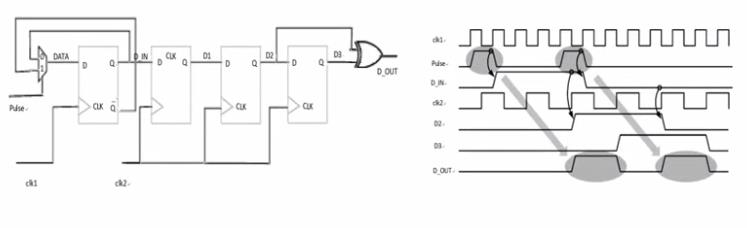

脉冲同步器

快时钟域中需要同步的信号是脉冲信号,它出发原时钟域的翻转电路,每当翻转电路时,电路被翻转一次,慢时钟域的同步器对翻转后的信号进行采样,和边沿检测,再重新在本时钟域恢复出脉冲信号。具体RTL设计可以参考之前写的一篇博客:

数字IC设计verilog编写——6脉冲同步器脉冲同步器的原理结构图:翻转电路 + 边沿检测电路

局限性:

1.脉冲需要是单脉冲信号

2.多个脉冲之间需要大于两个需要同步时钟域周期以上(边沿检测)。如果小于2个周期,可能最终的信号恢复出来的高电平脉冲连在一起或者重叠为一个周期。

3.不能用在快时钟域采样慢时钟域

-

握手处理(稳定可靠,不管是单比特还是多比特,均可采用)

当一个快时钟的单比特信号进入到慢时钟域,同样可以使用握手的方式进行同步处理。

四、典型电路

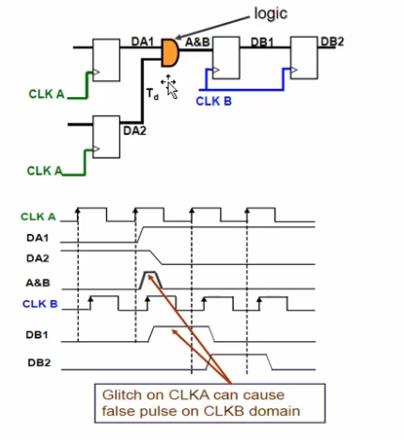

- 跨时钟域的多个相关连的单比特信号不可以通过打拍的方式同步到目的时钟域。

对跨时钟域的timing path如果不处理,容易导致亚稳态。

如果做了同步处理,但同步处理不当俨然会出现glitch,多路扇出问题,re-convergence,datahold等问题导致电路实际运行出现故障。

CLKA domain中,DA1和DA2分别为两个DFF的输出,理想状态下,DA1和DA2到达与门两个输入端的时间是一样的,这样设计就不会出现问题。

但是后端布局环境等因素,导致的传播延迟Td会使A&B存在一个glitch(信号到达与门的时间不一致)。而由于CLKB和CLKA为两个CLK Domain,之间不存在固定的相位关系,假设这个glitch恰好被CLKB锁存住,那么就会在DB2生成一个有效的高电平信号,这个高电平信号不是我们的设计所期望的,那就会导致后续的电路功能出现问题。

跨时钟域的多个相关联的单比特信号不可以通过打拍的方式同步到目的时钟域。

错误使用方法:(异步单bit控制信号组合逻辑输出的错误使用)

正确的解决方案(在原来时钟域先进行打拍处理):

以上是关于跨时钟域CDC电路设计的主要内容,如果未能解决你的问题,请参考以下文章