UVM学习——介绍

Posted 在路上-正出发

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了UVM学习——介绍相关的知识,希望对你有一定的参考价值。

引言

本专栏的博客均与 UVM 的学习相关,学习参考:

【1】UVM Tutorial

【2】张强著,UVM实战 (卷 Ⅰ)

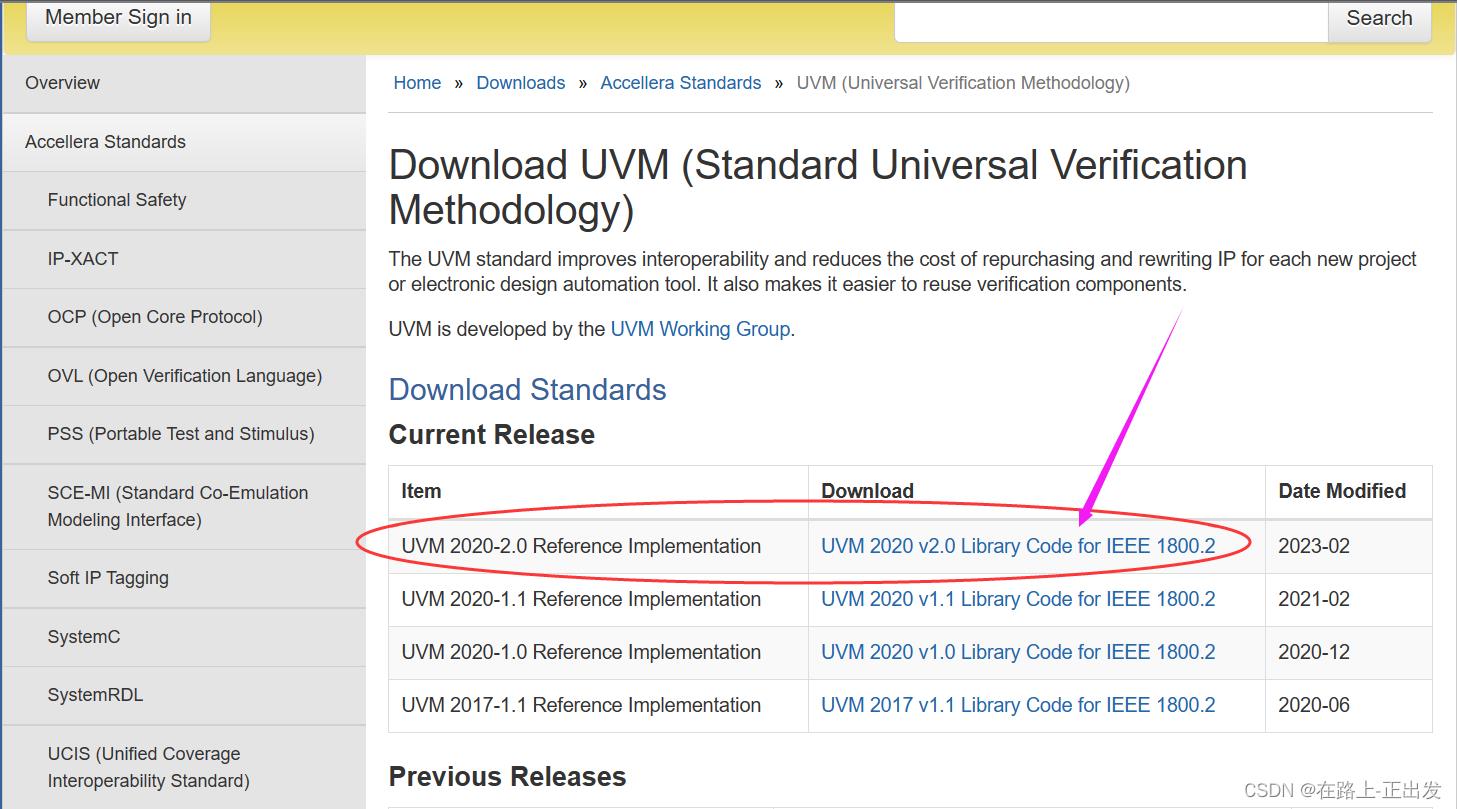

【3】Download UVM (Standard Universal Verification Methodology)

本文就先介绍 UVM 的基本内容。

UVM 概念

UVM(Universal Verification Methodology,通用验证方法) 是一个全产业的标准,它使能了更快速的开发,验证环境的重用以及IP验证。

它是使用SV的语法和语义定义的一组类库,SystemVerilog (IEEE 1800),现在是一个IEEE标准。

UVM背后的主要思想是通过提供可以部署在多个项目的API架构来帮助公司开发模块化、可重用和可扩展(推广)的 testbench 。

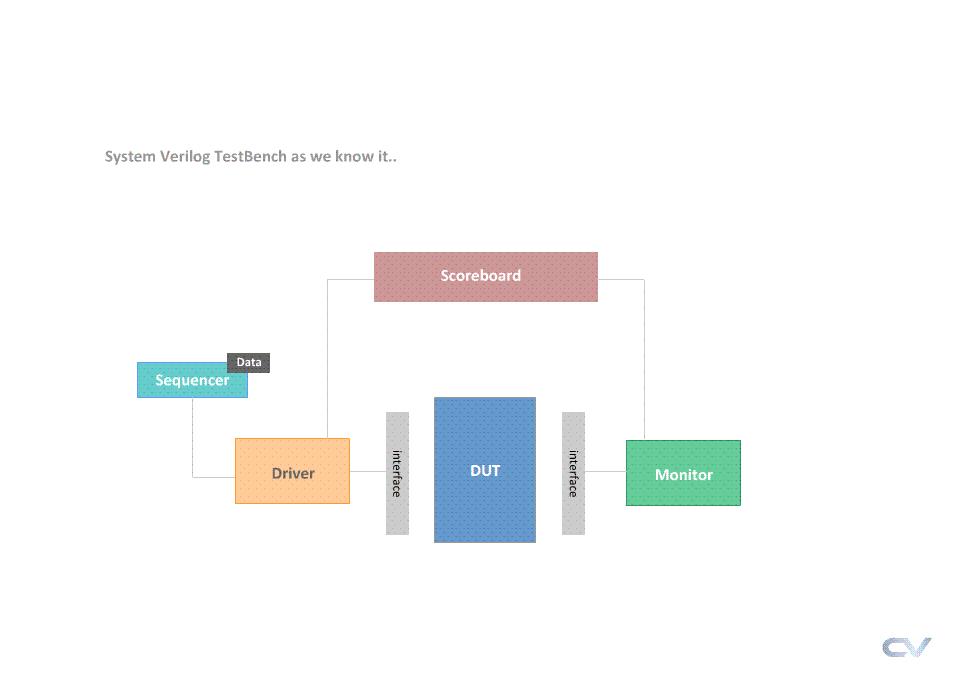

UVM主要来源于开放验证方法(OVM技术)和支持多个EDA供应商,像Synopsys,Cadence,Mentor and Aldec。UVM类库提供了通用的工具,比如配置数据库,TLM和组件层次结构除了数据自动化功能,如复制、打印和比较。它将在一个抽象层验证环境中的每个组件都有一个特定的角色。例如,驱动类的对象将只负责驱动设计中的信号,而监控只是监视的设计接口和不驱动接口信号。

下图显示了一个典型的验证环境是由扩展可用UVM类是用uvm_ *前缀。这些组件已经有必要的代码,让他们彼此之间的连接,处理数据包和与他人同步合作。

它还经历了许多修改,增加了新的功能,取消了一些旧的功能。UVM的参考手册可以在这里:Download UVM (Standard Universal Verification Methodology)获得,其中包含对类层次结构、函数和任务的描述。

这里对 UVM 资源的下载以及学习使用作如下说明:

1、点进去链接后,选择最新版本下载:

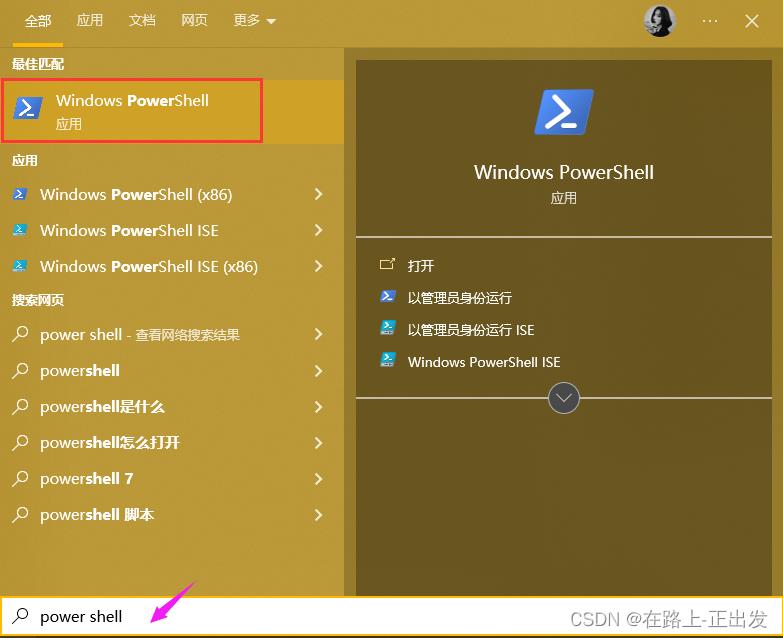

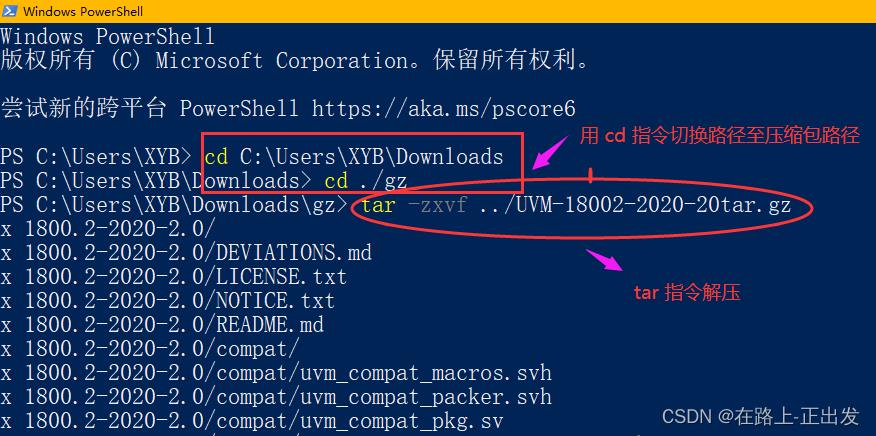

2、下载完成后,得到一个名为 UVM-18002-2020-20tar.gz 的压缩包。需要通过 power shell 完成解压。(Win 10)

搜索 power shell:

然后打开应用。

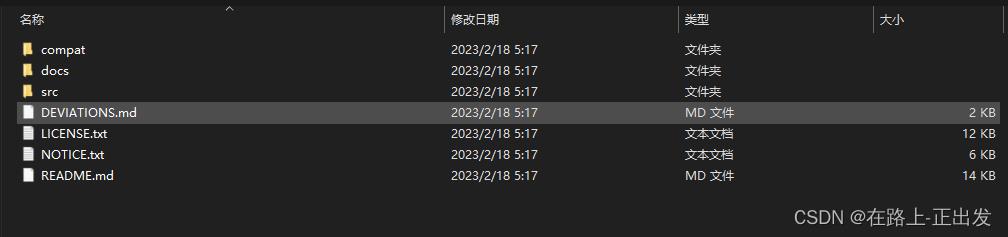

解压完成后,得到下面的文件:

当然,如果不想麻烦,直接进我的粉丝交流群(文末有链接),我已经上传到群文件:

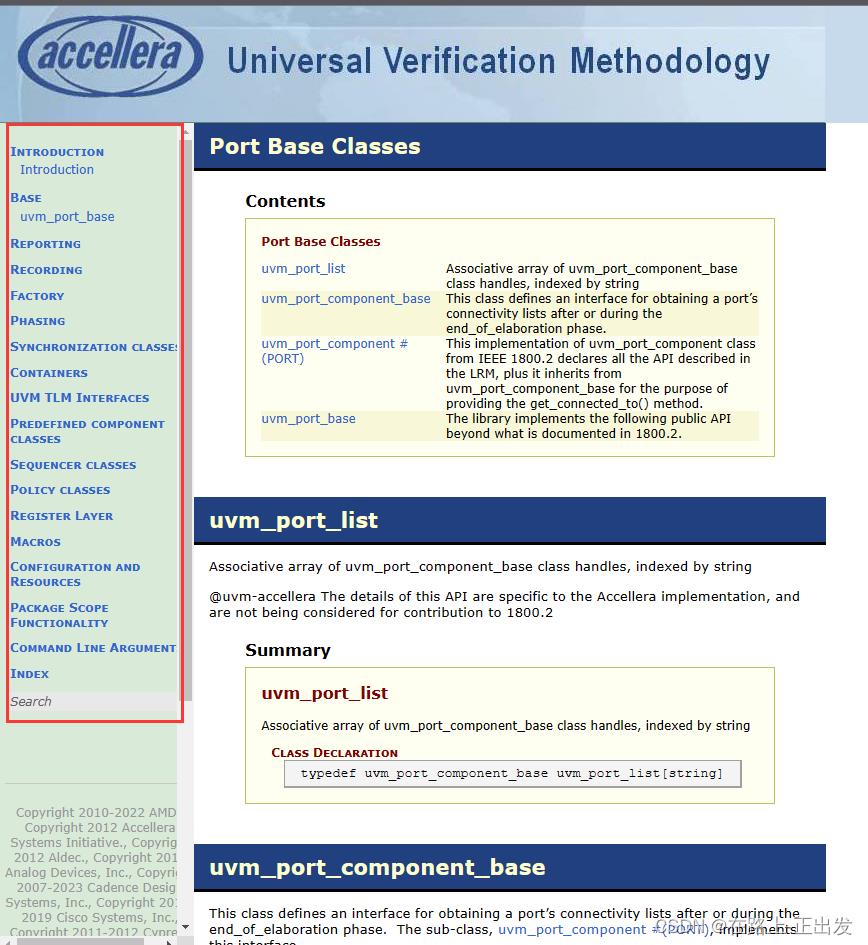

如果需要学习,建议直接打开下面所示的 网页文档:

可以按照右边的索引,系统学习:

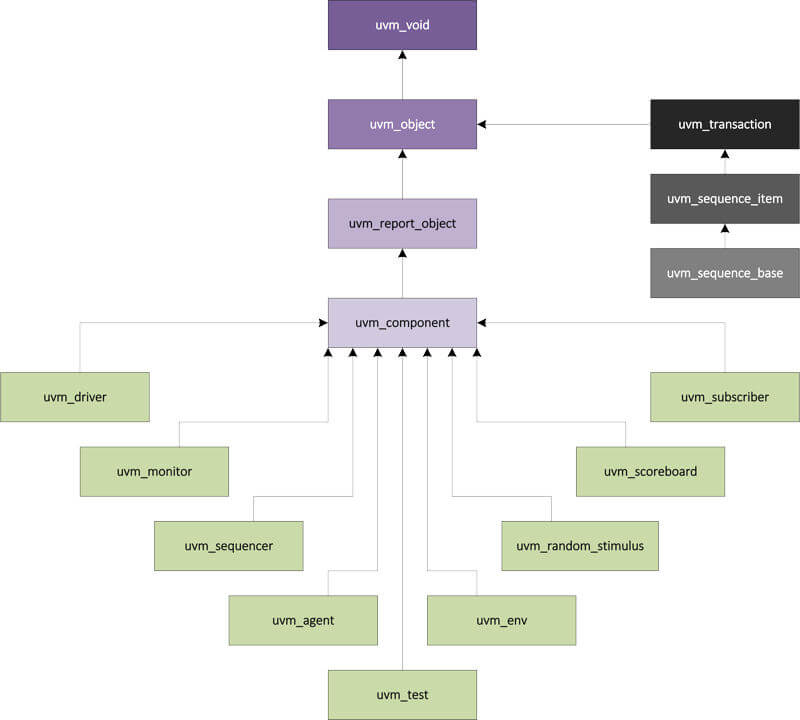

UVM 类的层级结构

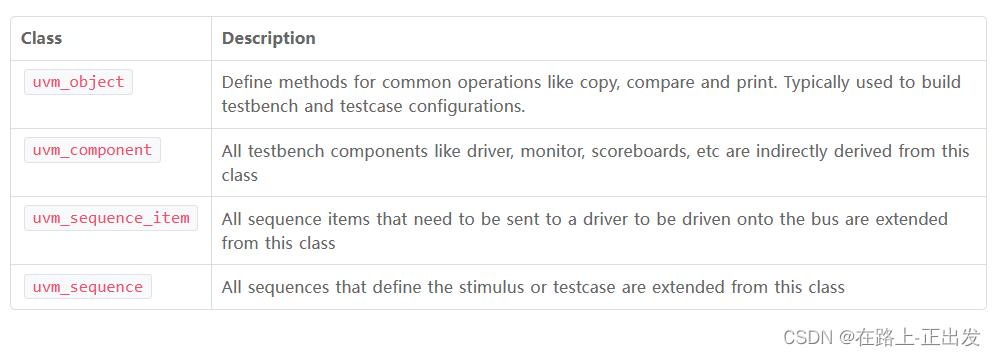

UVM提供了一组基类,从中可以通过继承来构建更复杂的类,并向其添加验证环境所需的某些函数。例如,可以通过从UVM基类uvm_driver扩展来构建Wishbone协议的新驱动程序类。该协议的激励可以通过从uvm_sequence_item中进行扩展来编写。如何构建这个序列并传递给驱动程序由UVM框架内部处理。

uvm_void是所有类的基础,但它是空类.uvm_object是主要类,其中定义了打印、复制和比较同一类的两个对象的公共函数。

该层次结构中有两个分支。第一个分支包含定义验证组件的类,如驱动程序、监视器,其余的在图中显示为UVM_REPORT_OBJECT下的所有内容。第二个分支定义由验证组件使用和操作的数据对象,这些数据对象在图中显示为UVM_TRANSACTION下的所有内容

UVM类的 主要类别

UVM对象(Objects)

UVM背后的想法是增强灵活性和重用代码,这样相同的测试台就可以以不同的方式配置来构建不同的组件,并提供不同的激励。建议从uvm_object中派生出这些新的用户定义的配置类。例如,可以构建一个配置类对象,使其具有定义必须如何构建测试台环境的某些设置。

UVM序列(Sequence)

UVM还引入了一个序列的概念,它只是一个实际激励设计的容器。如果你将不同的激励放到不同的序列中,它会增强重用和随机驱动这些序列的能力,以获得更多的覆盖率和验证结果。建议从uvm_sequence 继承所有新的用户定义的激励类。

每个序列都可以在其他序列中使用来创建不同的场景。例如,可以创建单独的序列,每个序列分别用于“读”和“写”事务。它们可以在其他序列中以随机模式用于执行R->W->R->W,或R->R->R->W,W->W->R->R和其他类似的模式。

UVM序列项(Sequence item)

必须驱动到DUT的数据对象通常被称为序列项,建议从 uvm_sequence_item 继承。例如,可以为APB事务定义一个序列项类,该事务定义了地址、写/读数据和访问类型,并将其发送到APB驱动程序,以将事务驱动到DUT。

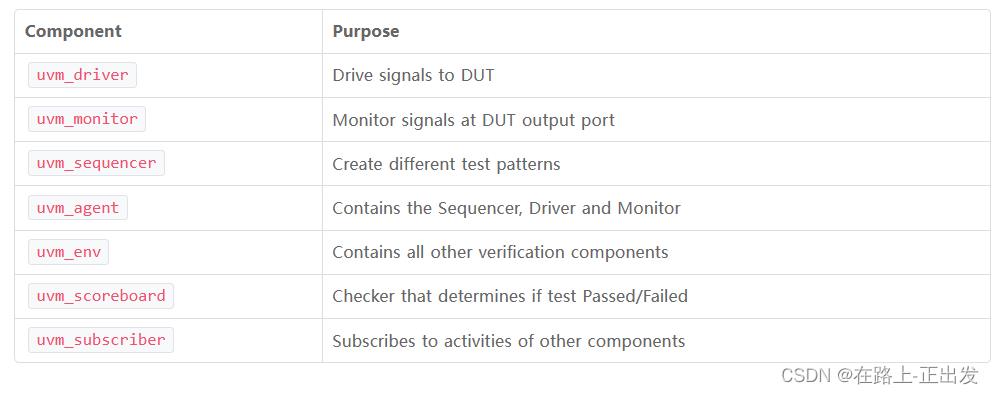

UVM组件

所有主要的测试台组件都来自于相应的基类。例如,建议从 uvm_driver 继承所有新的用户定义的驱动程序类,并从 uvm_monitor 继承监控器类,等等。下表中给出了对每个UVM组件所执行的操作的简要描述。

寄存器层

数字设计支持可以由软件配置的控制寄存器,这在系统虚拟日志测试台中是非常具有挑战性的,因为对于每个项目,您必须构建一组单独的类来存储和配置这些寄存器。UVM有一组广泛的类,使该任务相对简单,并且属于被称为寄存器模型的东西。这在验证可以在各种SoC设计中重用的ip时非常有用。

TLM连接

另一个真正聪明的特性是使用了来自System C的TLM。TLM帮助以事务和类对象的形式在组件之间发送数据。它还带来了一种向听众广播数据包的方法,而不必创建特定的频道并附加。

UVM阶段

验证组件从其父类 uvm_component 继承的另一个主要特性是阶段性的。这使得每个组件在继续下一阶段之前相互同步。下一章将介绍各个阶段。每个组件都经过实例化的构建阶段,在连接阶段相互连接,在运行阶段消耗模拟时间,并在最后阶段一起停止。

从零开始学习 UVM4.1UVM Phases —— UVM Phases 介绍

文章目录

UVM Phases是什么?

所有TestBench组件都是从uvm_component派生的,并且具有 Phase 概念。每个组件都经历一组预定义(pre-defined)的phases,直到所有组件在当前phase执行完毕后,它才能进入下一个phase。因此,UVM阶 phase在仿真生命周期中充当同步机制(synchronizing mechanism)。

由于各个Phase被定义为回调函数,所以从uvm_component派生的类可以在回调方法中执行有用的工作。不消耗仿真时间的方法是函数,而消耗仿真时间的方法则是任务。所有阶段可以分为三类:

-

- 构建时期(Build time phases)

以上是关于UVM学习——介绍的主要内容,如果未能解决你的问题,请参考以下文章

从零开始学习 UVM4.1UVM Phases —— UVM Phases 介绍

从零开始学习 UVM3.11UVM TestBench架构 —— UVM Virtual Sequencer

从零开始学习 UVM5.1UVM Factory —— UVM Factory Override(工厂覆盖)