计算机组成原理王道中央处理器学习笔记

Posted 买个等离子电视

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机组成原理王道中央处理器学习笔记相关的知识,希望对你有一定的参考价值。

声明:本文在经过 努力的clz同意的情况下进行了一定的借鉴。图片来源于王道,本文仅用于学习所用!

王道计算机组成原理课代表 - 考研计算机 第五章 中央处理器 究极精华总结笔记_努力的clz的博客-CSDN博客

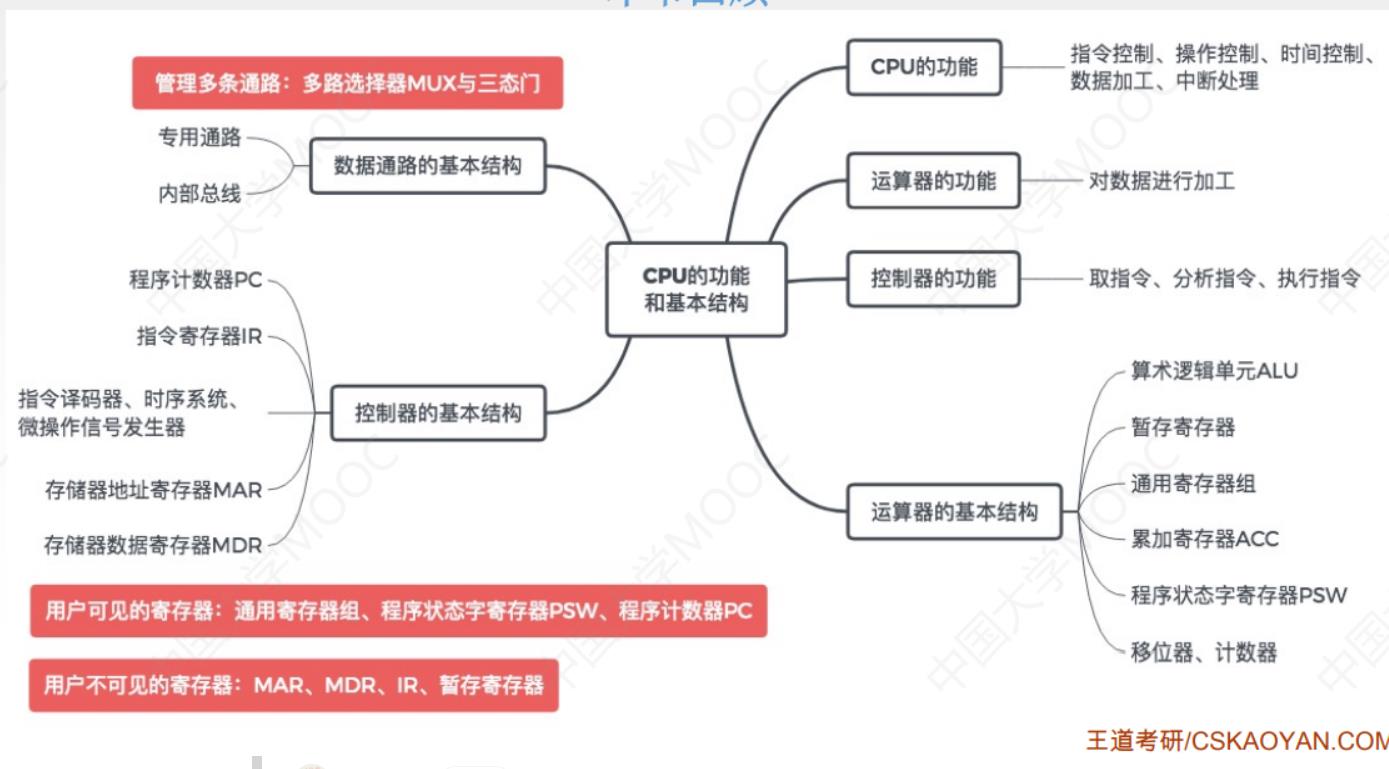

CPU的功能和基本结构

cpu的功能:

指令控制。完成取指令、分析指令和执行指令的操作,即程序的顺序控制。

操作控制。一条指令的功能往往是由若干操作信号的组合来实现的。CPU管

理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件,

从而控制这些部件按指令的要求进行动作。

时间控制。对各种操作加以时间上的控制。时间控制要为每条指令按时间

顺序提供应有的控制信号。

数据加工。对数据进行算术和逻辑运算。

中断处理。对计算机运行过程中出现的异常情况和特殊请求进行处理。

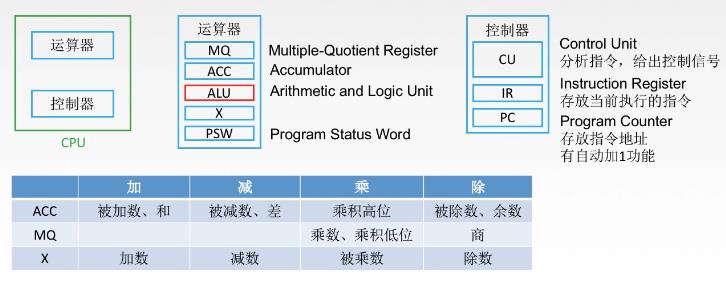

cpu中有运算器和控制器:

运算器:对数据进行加工

控制器:

协调并控制计算机各部件执行程序的指令序列,基本功能包括取指令、分析指令、执行指令

取指令:自动形成指令地址;自动发出取指令的命令。

分析指令:操作码译码(分析本条指令要完成什么操作);产生操作数的有效地址。

执行指令:根据分析指令得到的“操作命令”和“操作数地址”形成操作信号控制序列,控制运算器、存储器以及I/O设备完成相应的操作。

中断处理:管理总线及输入输出;处理异常情况(如掉电)和特殊请求(如打印机请求打印一行字符)。

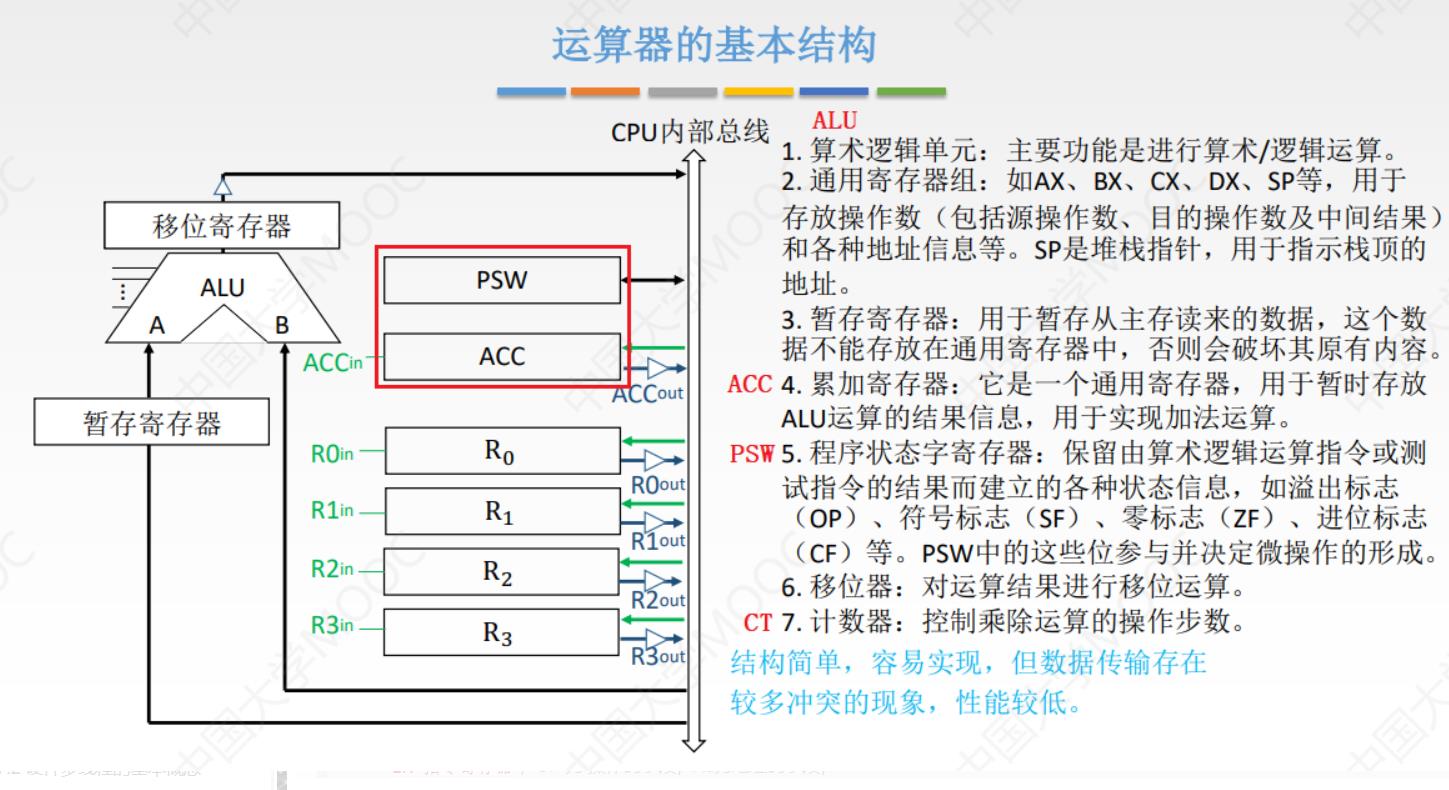

运算器的基本结构:

算数逻辑单元和通用寄存器

ALU是一个组合逻辑电路,可以实现算数运算和逻辑运算。图中A、B是指提供的两个操作数。很多情况下会把参与运算的一些数据提前存放在一些通用寄存器中。比如 。

。

右侧为x86架构对应的通用寄存器

在X86架构中,还会提供一些通用寄存器组AX,BX,CX,DX,SP等。如上图所示,其中AH指的是AX寄存器中的高位字节部分,AL指的则是AX寄存器中的低字节部分。其余部分的也类似。通用寄存器可以用来存放操作数(包括源操作数、目的操作数及中间结果和各种地址信息。SP是堆栈指针,用于指示堆栈的地址)

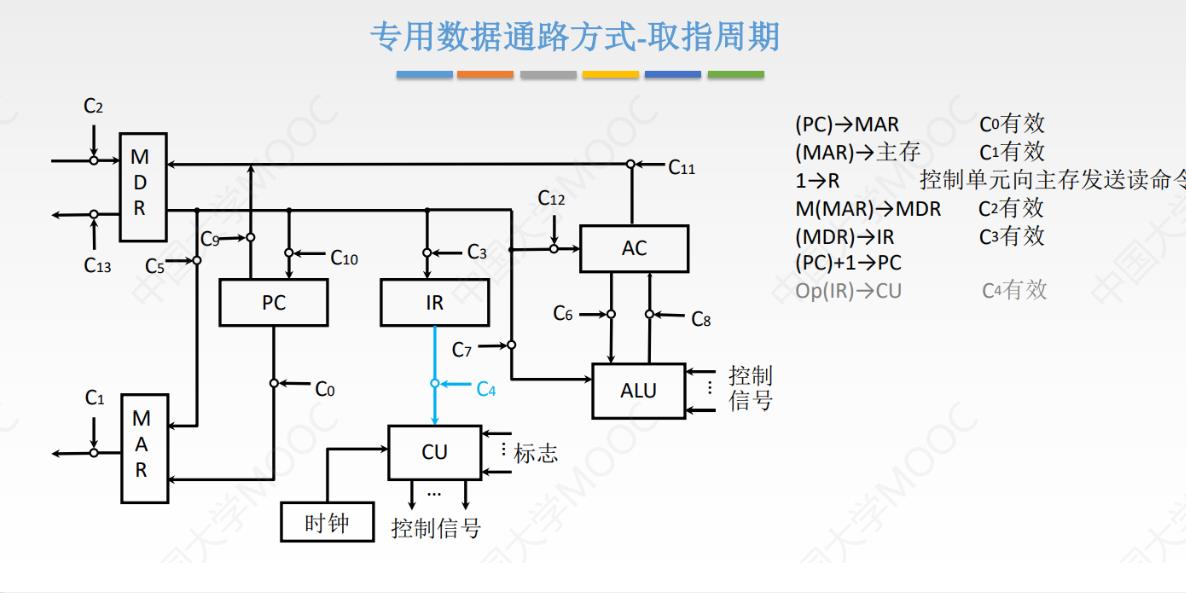

专用数据通路方式

数据通路设计方式

专用数据通路方式

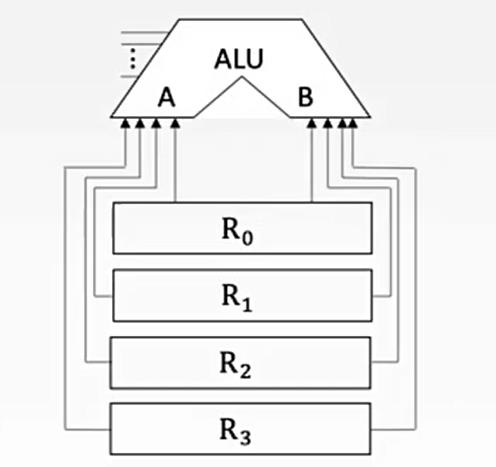

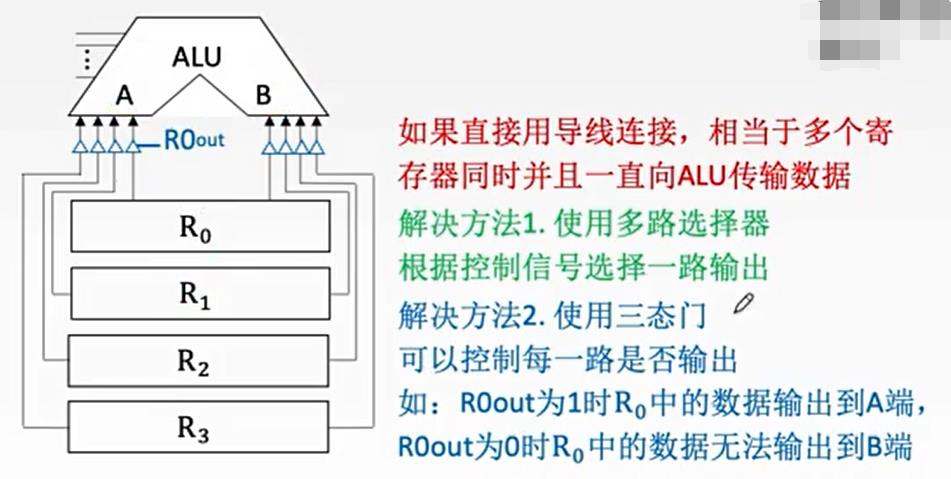

专用数据通路方式:根据指令执行过程中的数据和地址的流动方向安排连接线路。(如果直接用导线连接,相当于多个寄存器同时并且一直向ALU传输数据)

由于只能在专用寄存器中左边选择一个和右边选择一个进行输入,不能左边或者右边同时输入多个数据,因此有两种解决方案:

解决方法1:使用多路选择器根据控制信号选择一路输出

解决方法2.使用三态可以控制每一路是否输出

采用专用数据通路的方式,优点是性能较高,基本不存在数据冲突现状,缺点是结构复杂,硬件量大,不易实现。

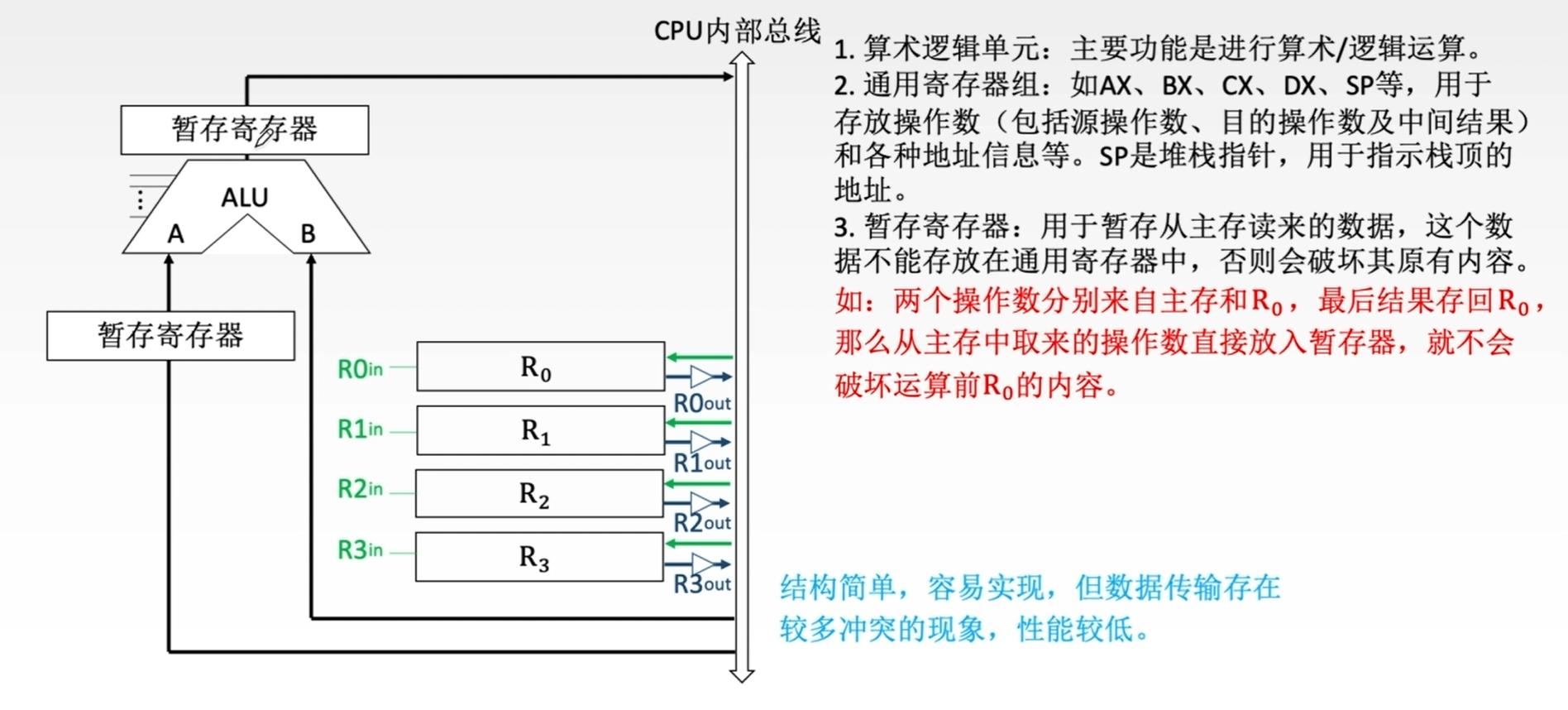

CPU内部单总线设计方式

CPU内部单总线设计方式:将所有寄存器的输入端和输出端都连接到一条公共的通路上。寄存器的输入端和输出端都连接到一条公共的通路上。

寄存器中的数据如何通过总线传入算数逻辑单元?首先将R0out打开(使三态门有效),这时候R0寄存器中的数据会通过总线先流入暂存寄存器中,之后需将R0out关闭(使三态门失效),将R1打开,这时候数据会通过另一个导线流入B(这里应该有一个控制的过程,目前还不理解这里为什么会指定流入A或B)。通过运算后,数据要保存在R0中。ALU的两个信号端A、B一定要等到两端电信号稳定后若在ALU之后不加暂存寄存器,那么输出结果会对B的信号造成影响。

A、B两处的操作数都需要从总线读数据,这步就发生冲突了,所以可以给其中一端添加 暂存寄存器 ,解决输入冲突问题; AUL的运算结果 和 B操作数输入端 都连接这总线,又发生了冲突,所以在ALU的输出端也添加了 暂存寄存器 ; 暂存寄存器 还可以添加一些功能,改造成 移位寄存器 或 累加寄存器 ;

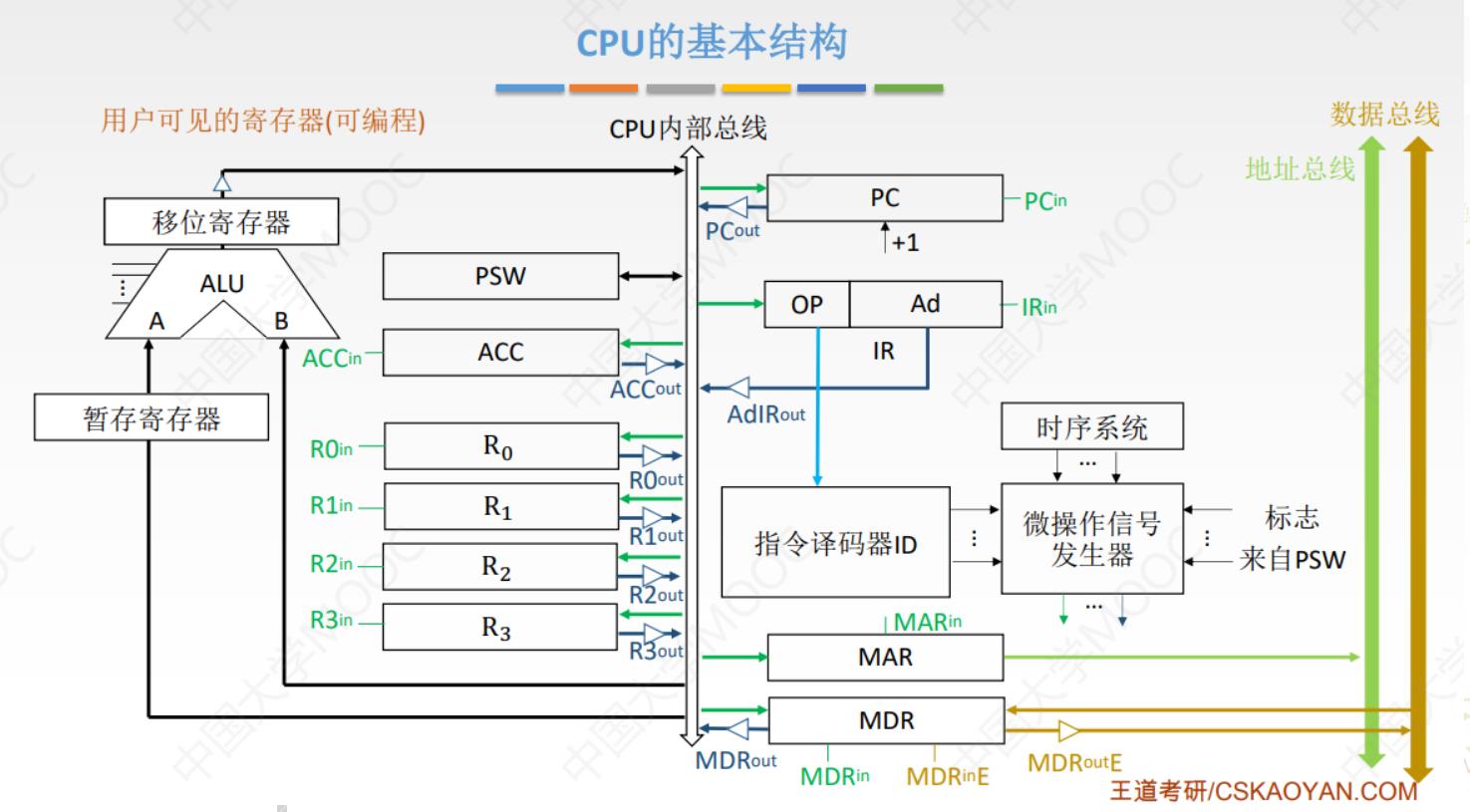

控制器的基本结构

2. 控制器的基本结构

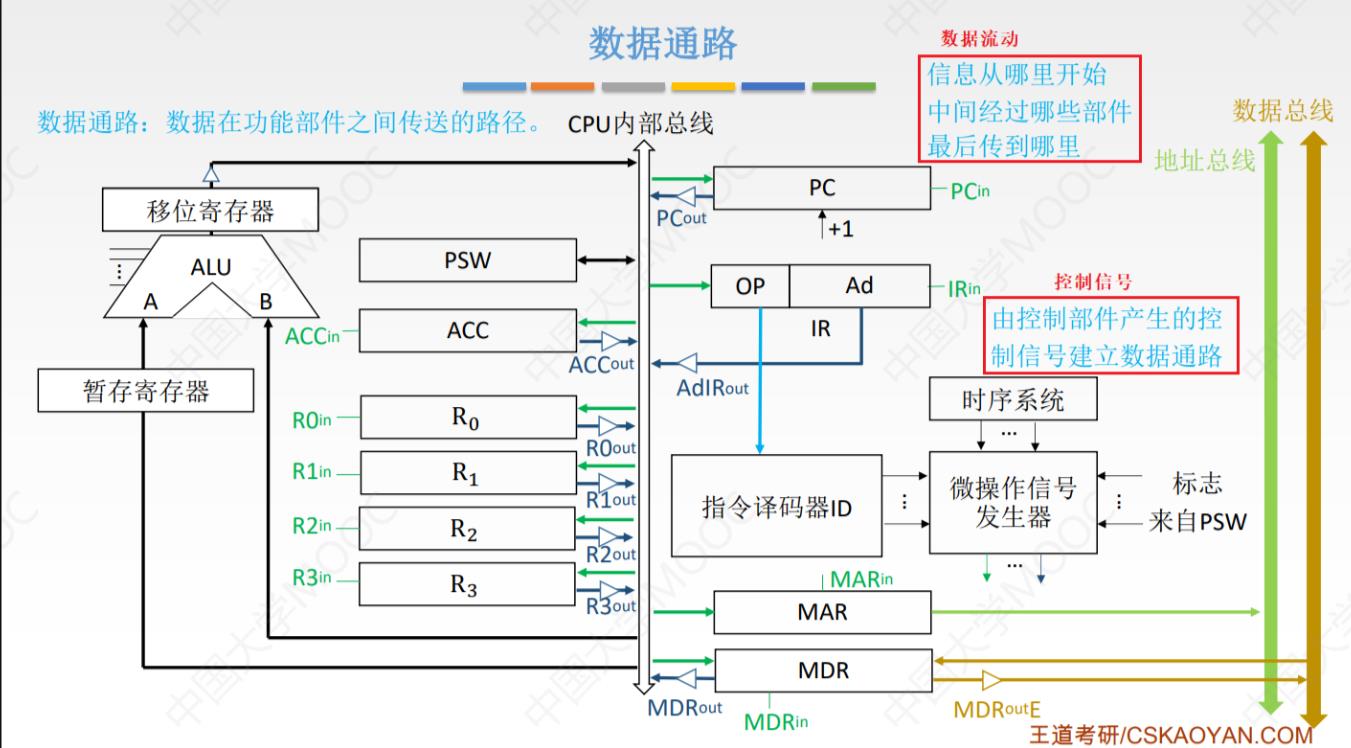

PC 程序计数器;

IR 指令寄存器,OP 为 操作码字段,Ad为地址码字段;

ID 指令译码器,OP 作为译码器的输入,该指令对应的输出端就会选通,就知道具体指令操作;

ID的输出信号 就是 微操作信号发生器 的输入信号,用来判断该指令对应的微操作序列;

说白了,译码器 会将 操作码字段 具体分为对应的 微操作 ;

MAR 地址寄存器;

MDR 数据寄存器,MDRin 是从CPU内部输入,MDRinE 是从外部输入;MDRout ,MDRoutE 同理;

时序系统,用于产生各种时序信号,它们都是由同一时刻分频得到的;

微操作信号发生器;

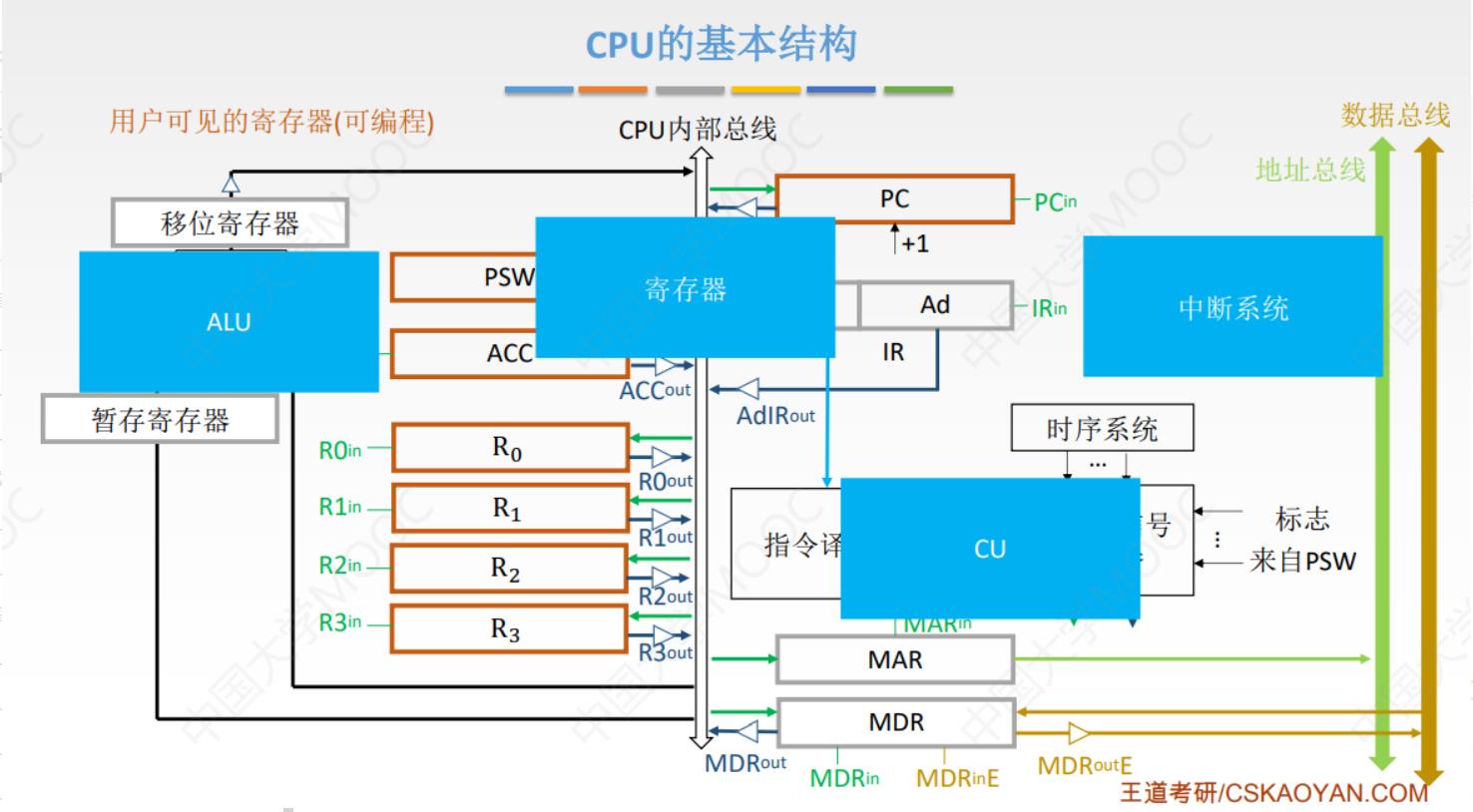

下图中橙色的寄存器为 用户可见的寄存器 ,灰色表示 用户不可见的寄存器 ;(选择题常考)

用户可见寄存器 (可对其编程): X 通用寄存器、PSW 程序状态字寄存器、累加器 ACC、程序计数器 PC;

用户不可见寄存器 (不可编程): MAR 存储器地址寄存器、MDR 存储器数据寄存器、IR 指令寄存器;

本章小结

指令的执行

指令周期

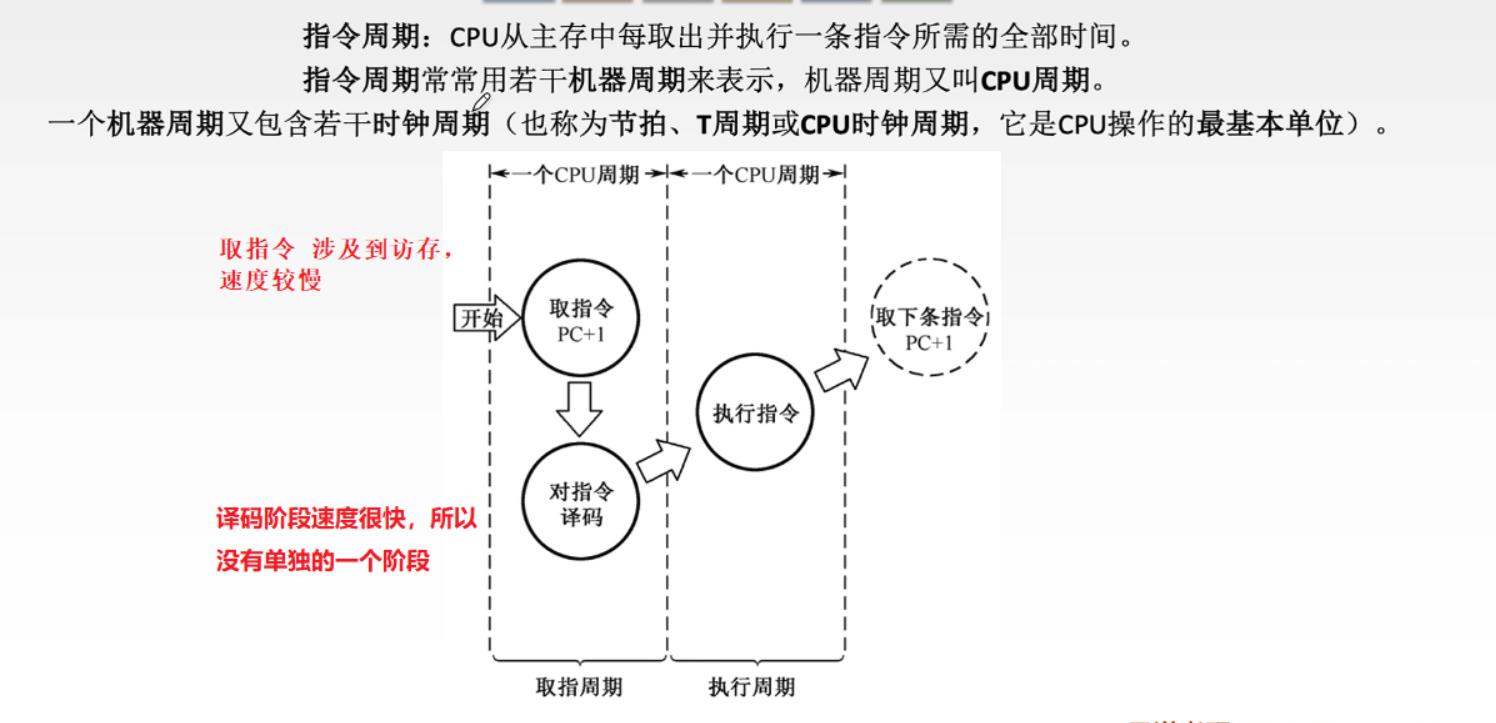

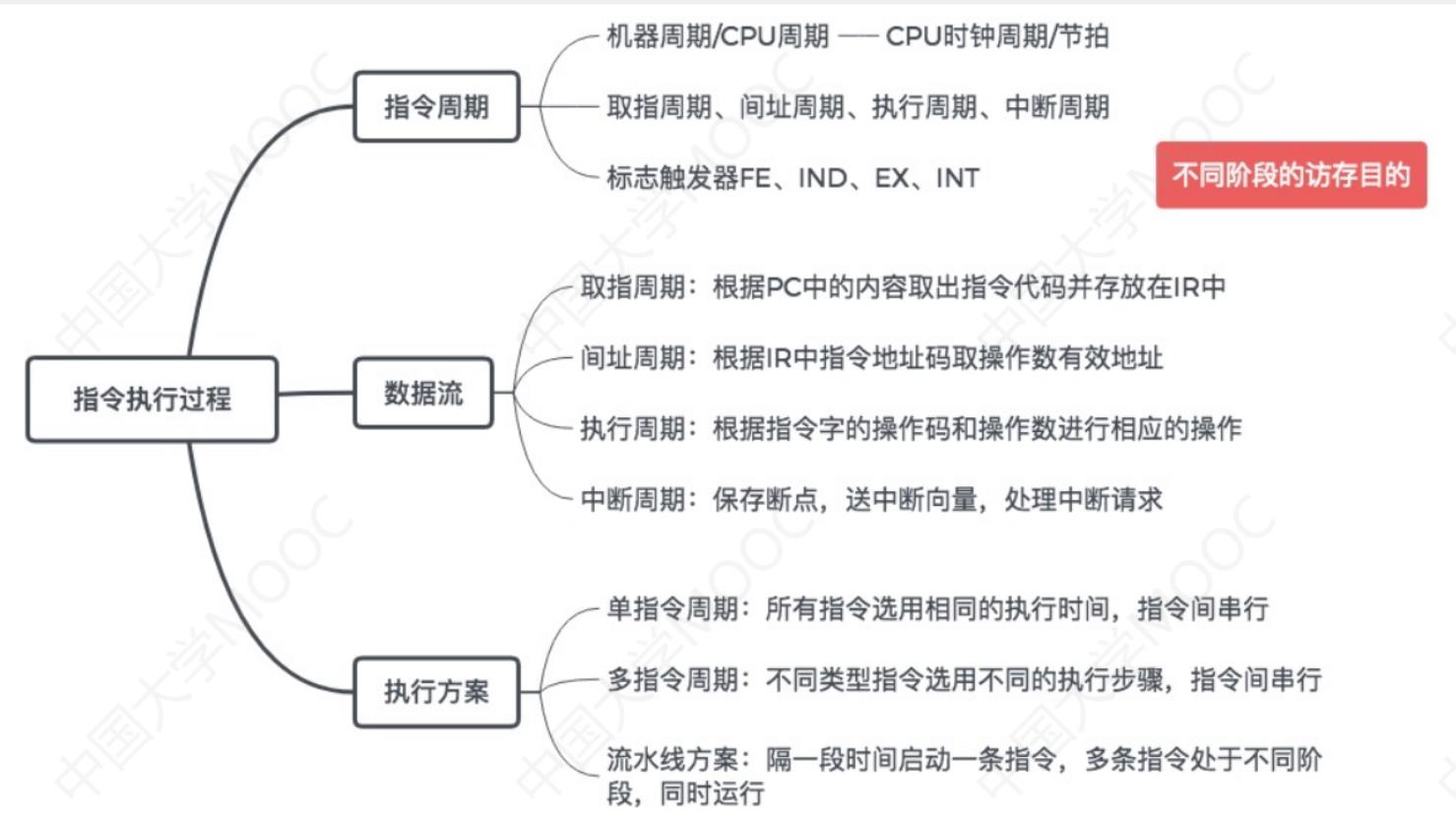

指令周期:cpu从主存中每取出并执行一条指令所需的全部时间。(每个指令的指令周期不一定相等)

一个 指令周期 划分为若干个 机器周期 (CPU周期) ;

一个 机器周期 划分为若干个 时钟周期(时钟周期 = 节拍 = T周期 = CPU时钟周期);

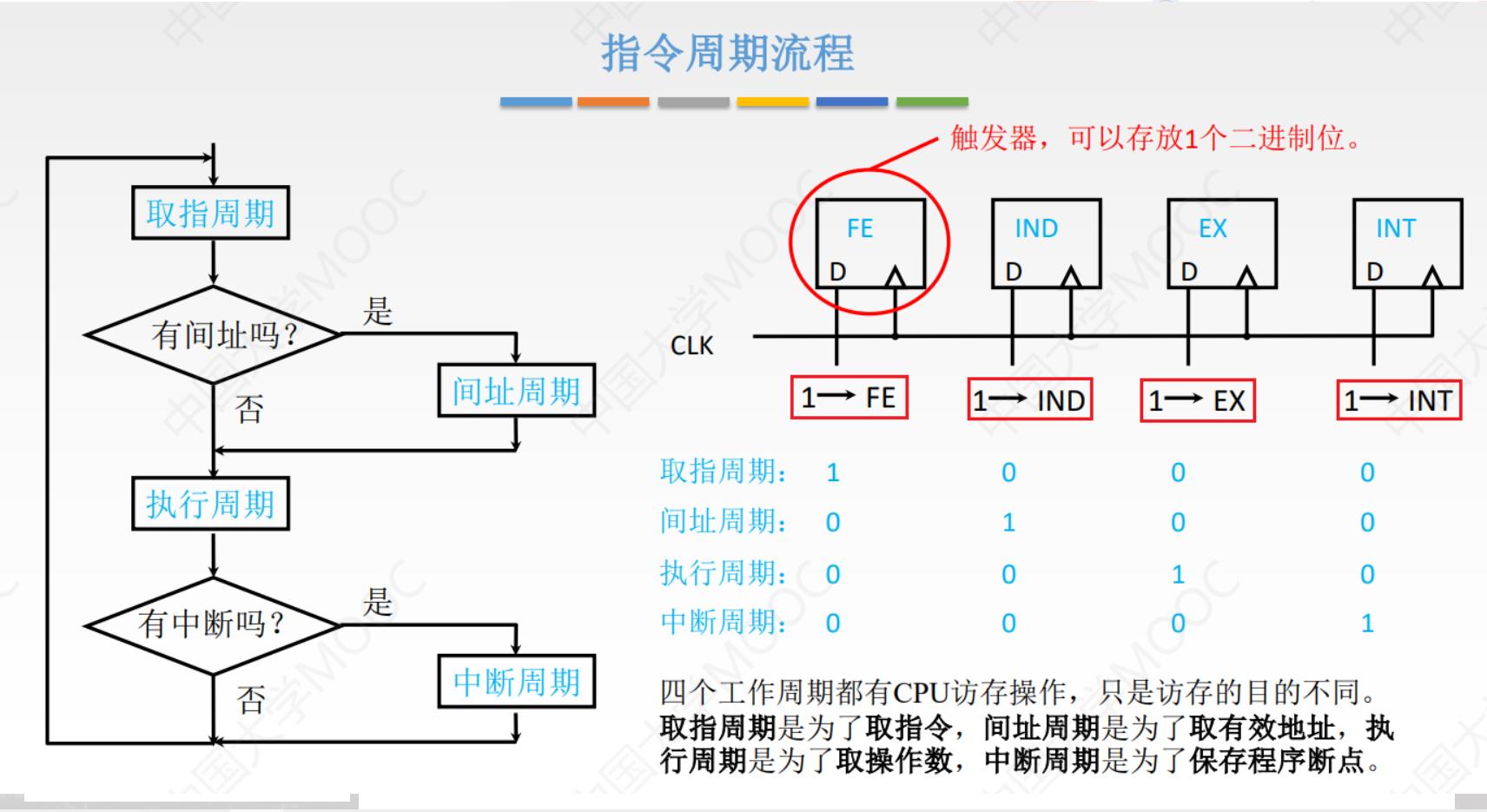

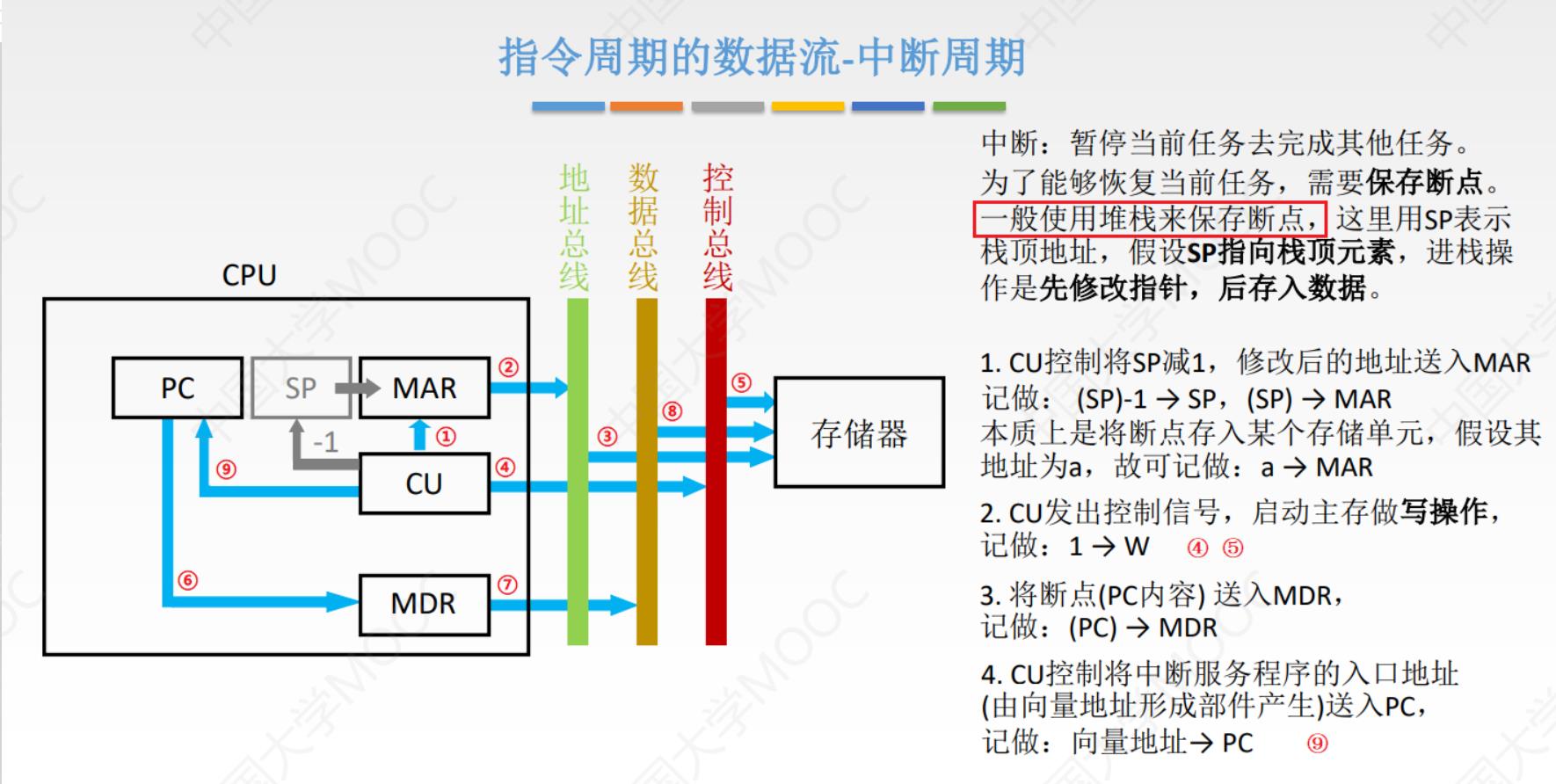

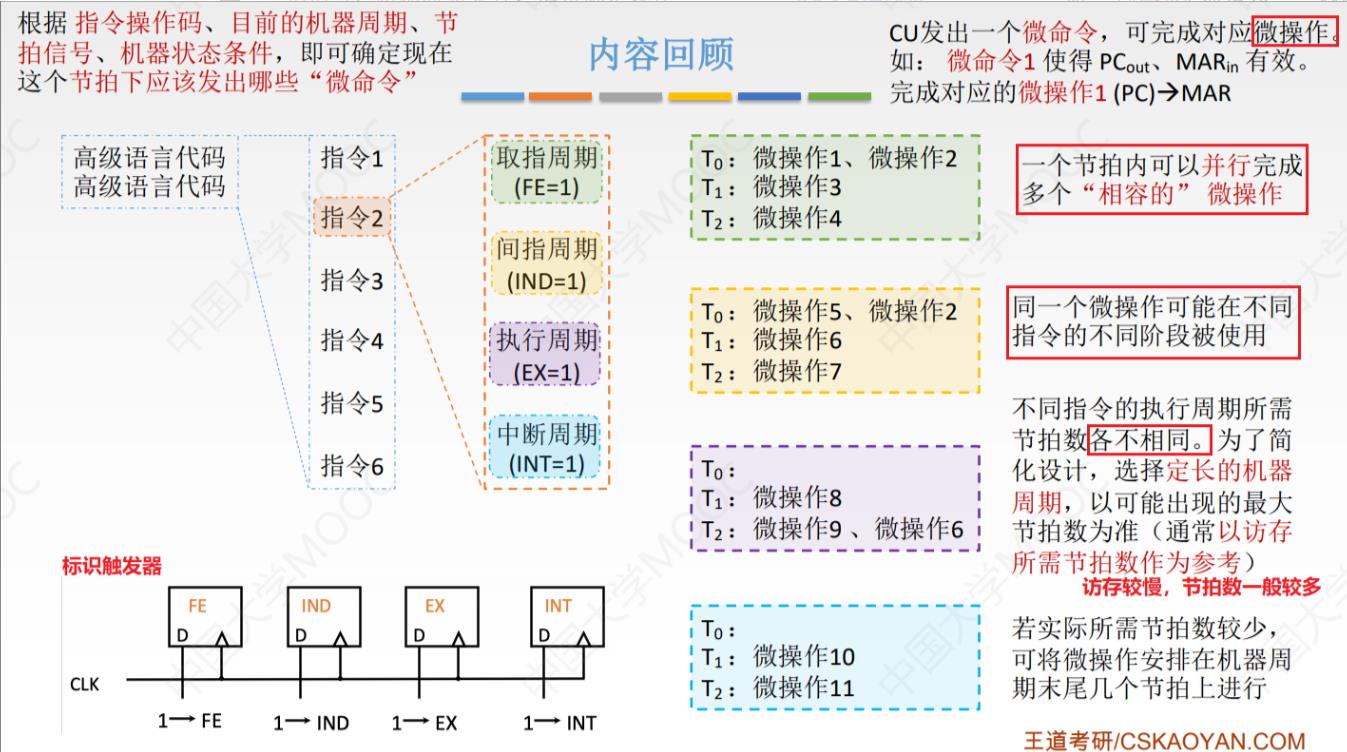

一条指令的执行分为不同的阶段:取指周期 - 间址周期 - 执行周期 - 中断周期;

当 CPU 采用中断方式实现主机和 I/O设备 的信息交换时,CPU在每条指令执行结束前,都要发中断查询信息。若有中断请求,

则CPU进入中断响应阶段(中断周期);

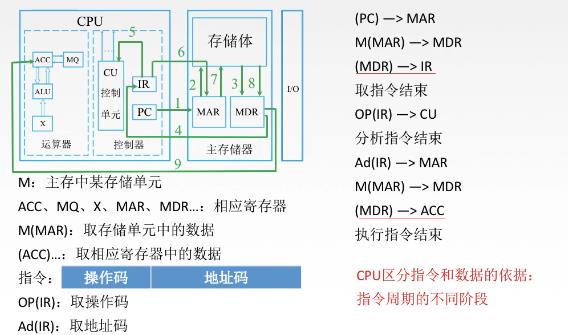

指令周期的数据流

为了标识当前处于哪个阶段,CPU内设置四个 标志触发器:FE、IND、EX、INT;

四个工作周期 都有CPU访存 操作,只是访存的 目的不同 :

取值周期 为了 取指令;

间址周期 为了 取有效地址;

执行周期 为了 取操作数;

中断周期 为了 保护程序断点;

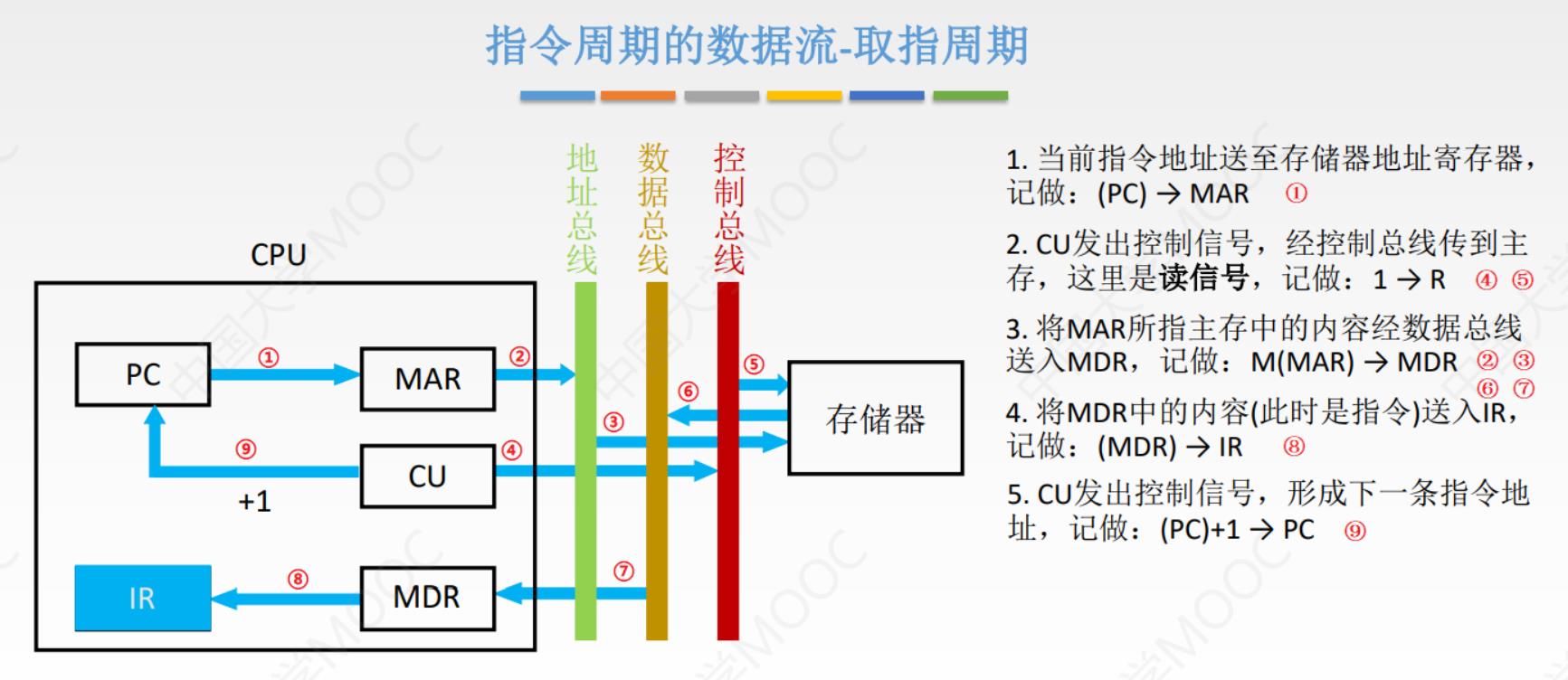

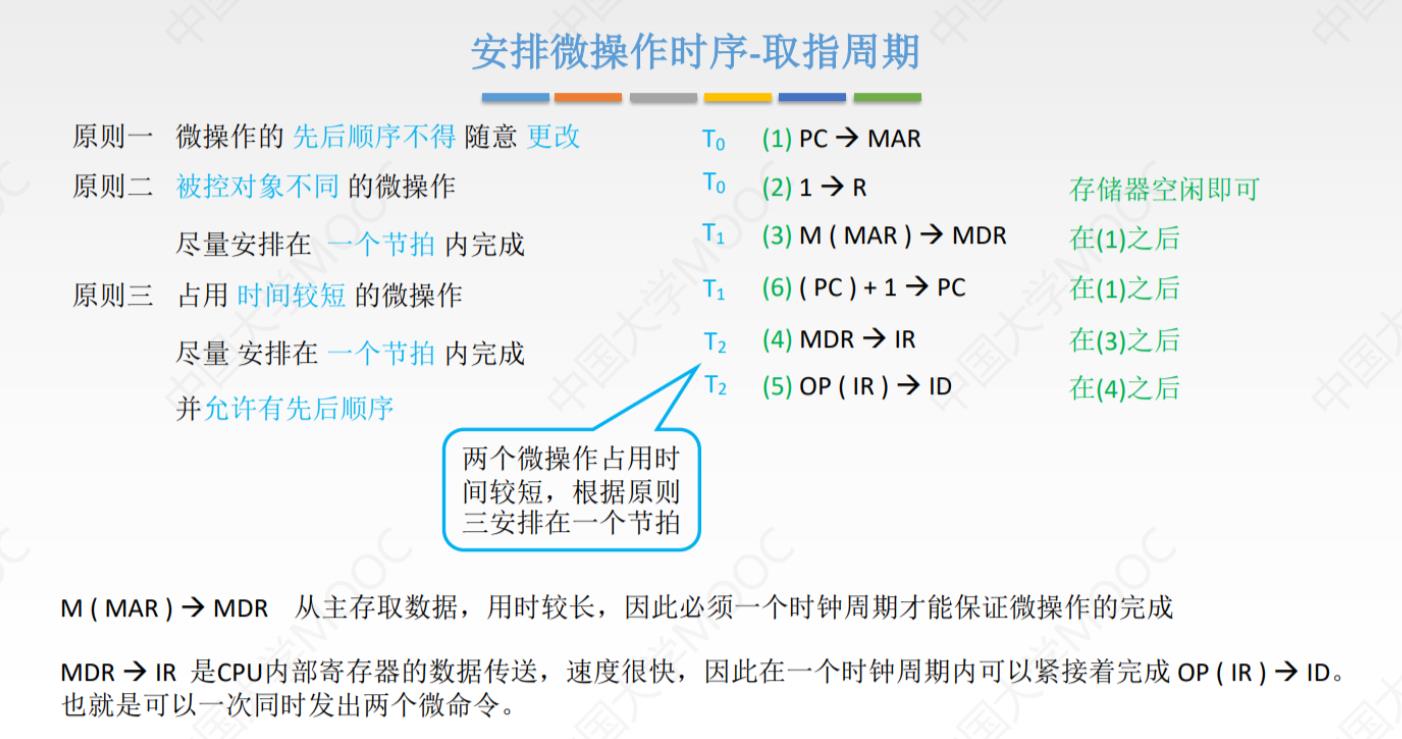

1. 取指周期

取指周期的任务是根据PC中的内容,从主存中 取出指令代码 并 存放在IR中 ;

2. 间址周期

间址周期的任务是取操作数有效地址;

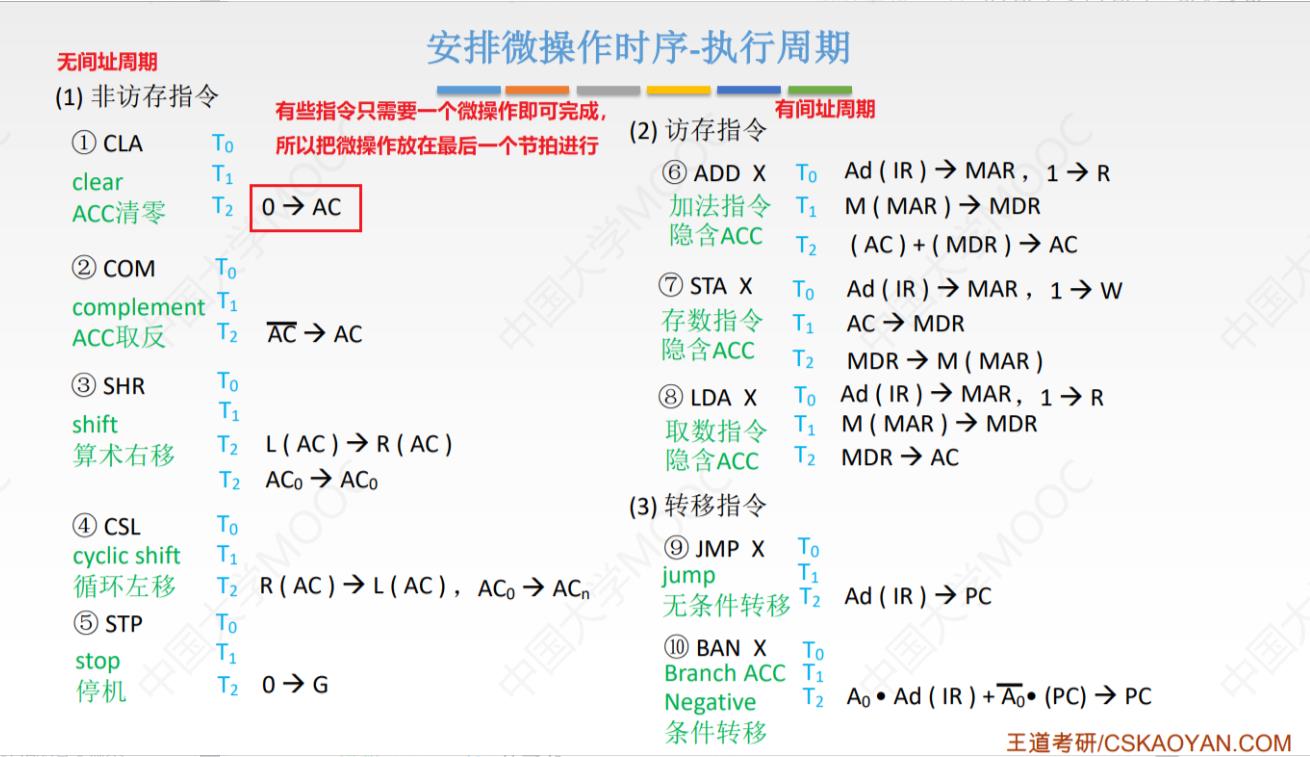

3. 执行周期

4.中段周期

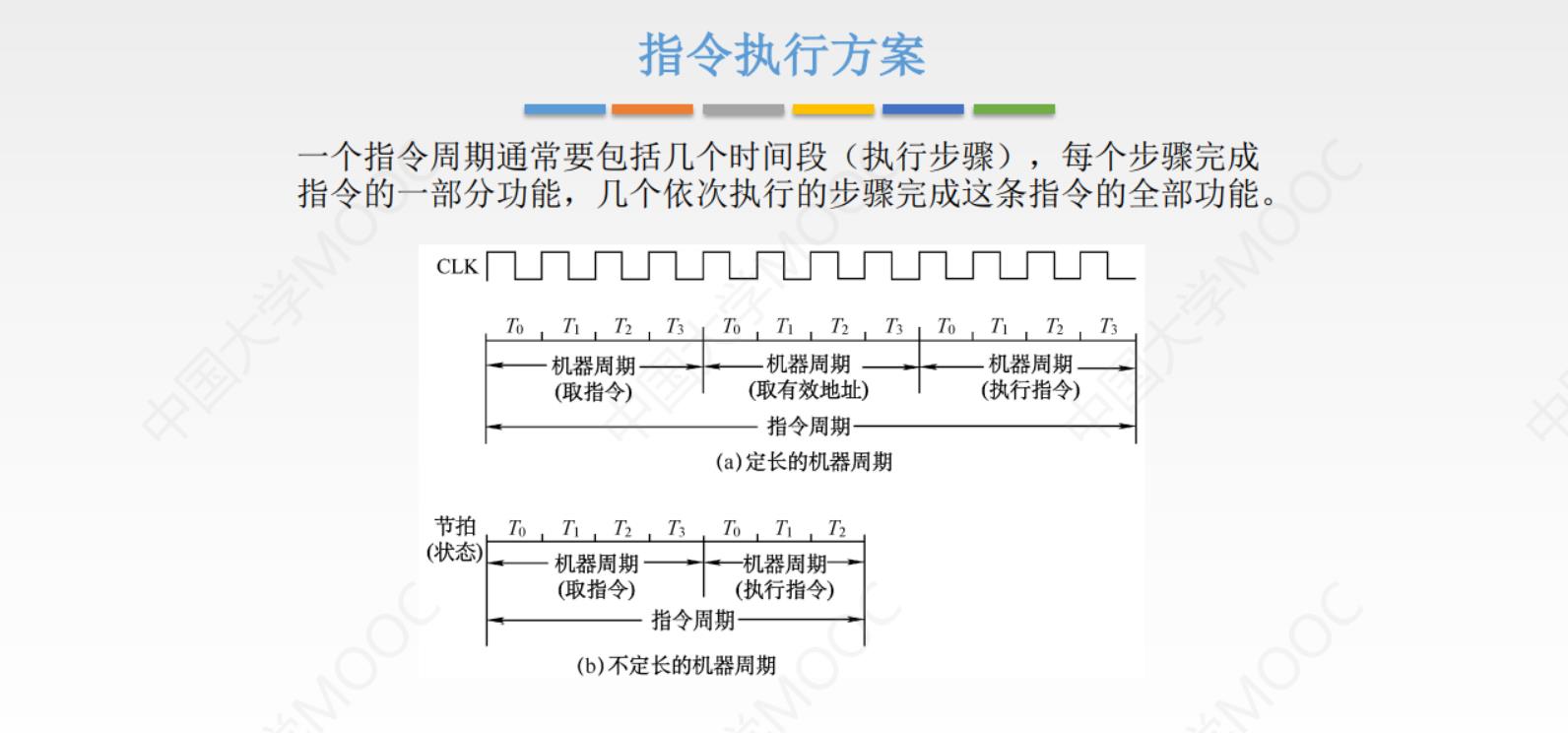

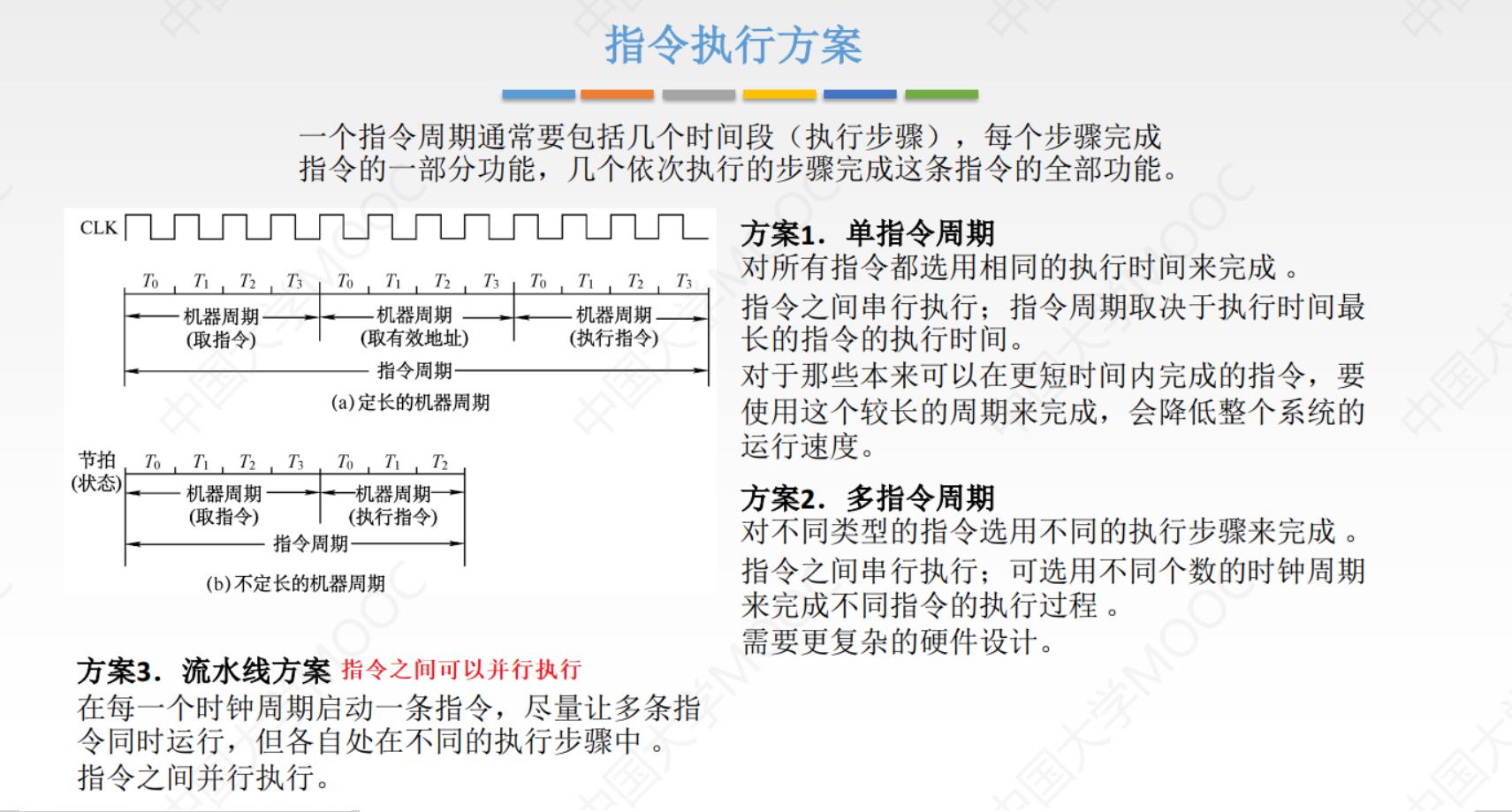

指令执行方案

指令执行方案

单指令周期:每条指令的 执行时间 规定相同;

多指令周期:每天指令的 执行时间 可以不同;

流水线方案:具体看 指令流水线 ;

章节小结

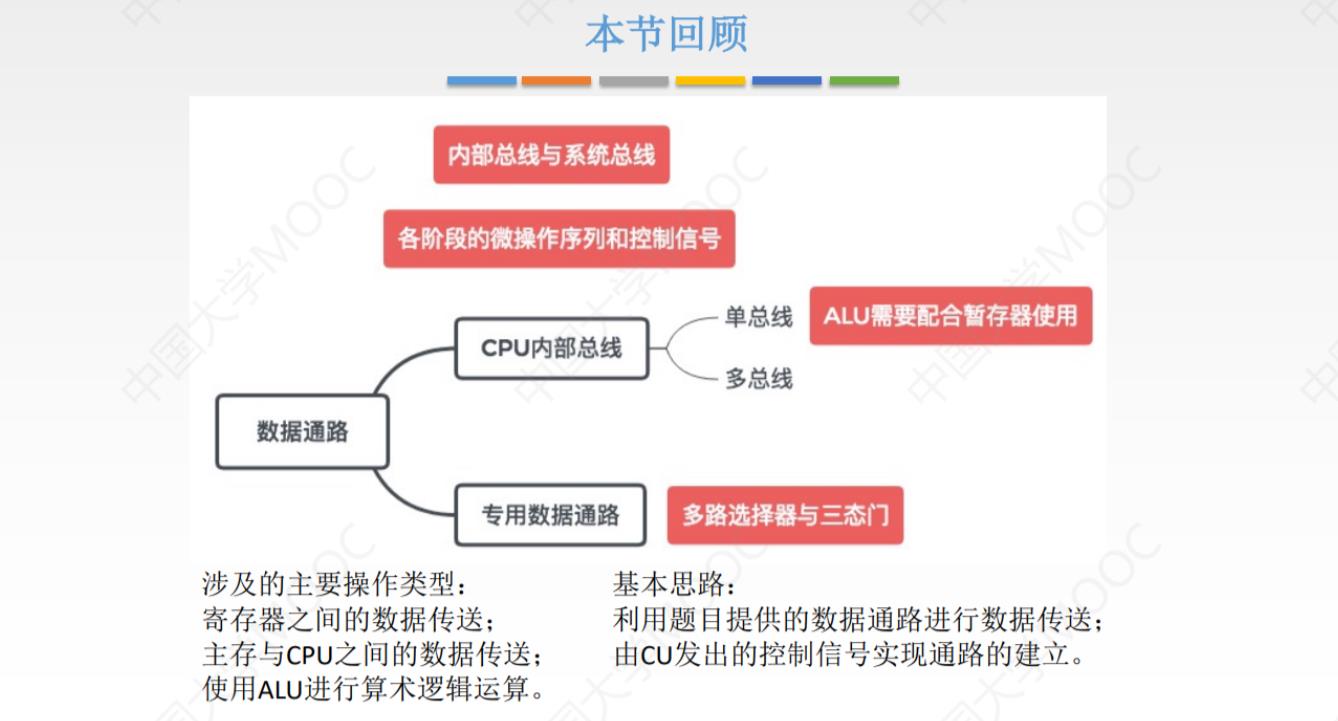

数据通路的功能和基本结构

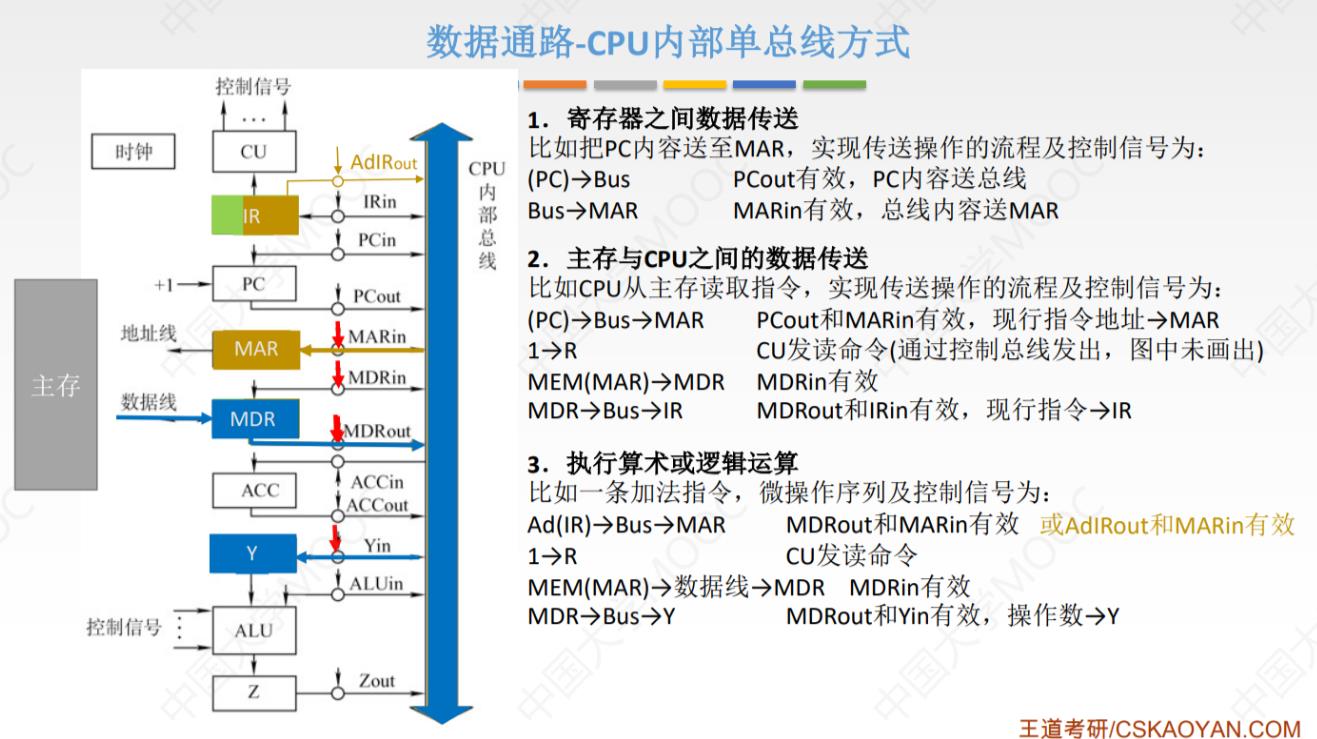

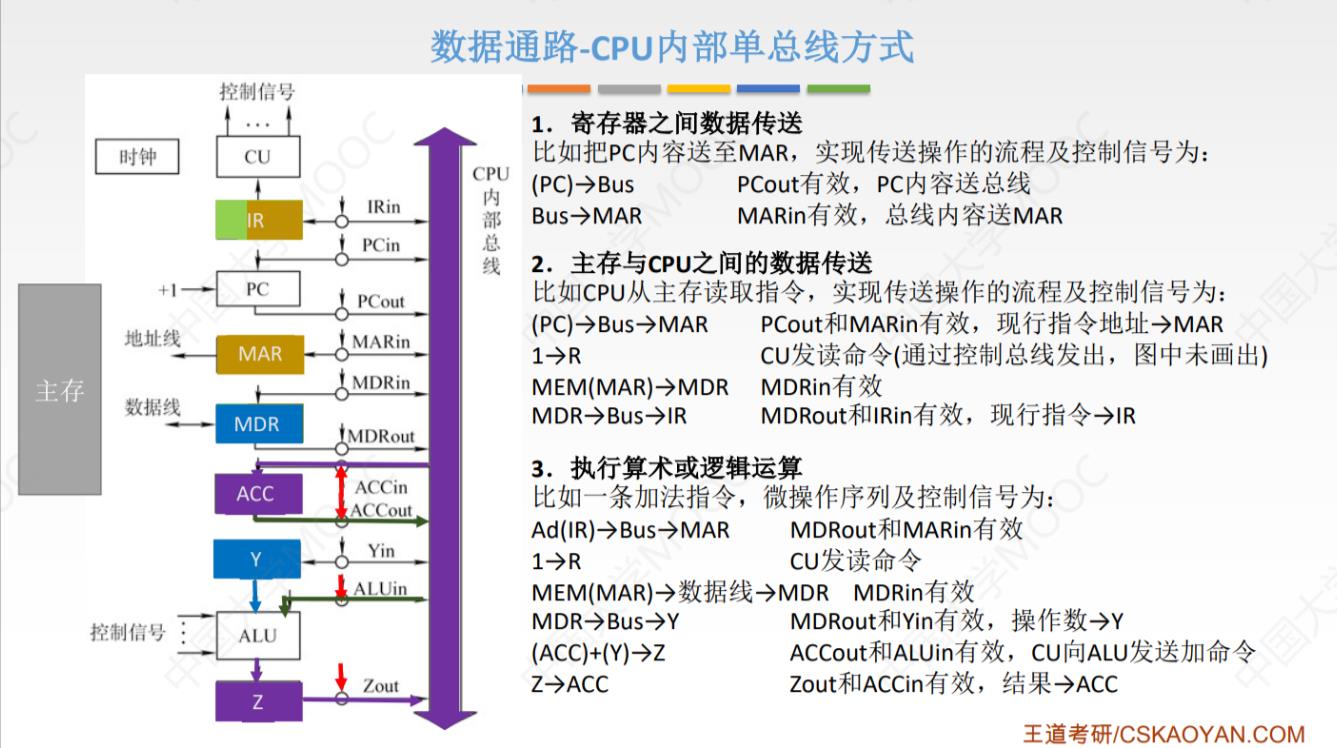

本节重点关注在指令执行中, 数据流动 情况和对应 控制信号;

数据通路的功能

数据通路:数据在功能部件之间传送的路径;

数据通路描述了信息从哪里开始、中间经过哪些部件、最终传送到哪个寄存器;

数据通路由 控制部件 控制,控制部件根据每条指令功能的不同生成对数据通路的控制信号;

数据通路的功能是 实现CPU内部的 运算器与寄存器 及 寄存器之间 及 寄存器与主存之间 的数据交换 ;

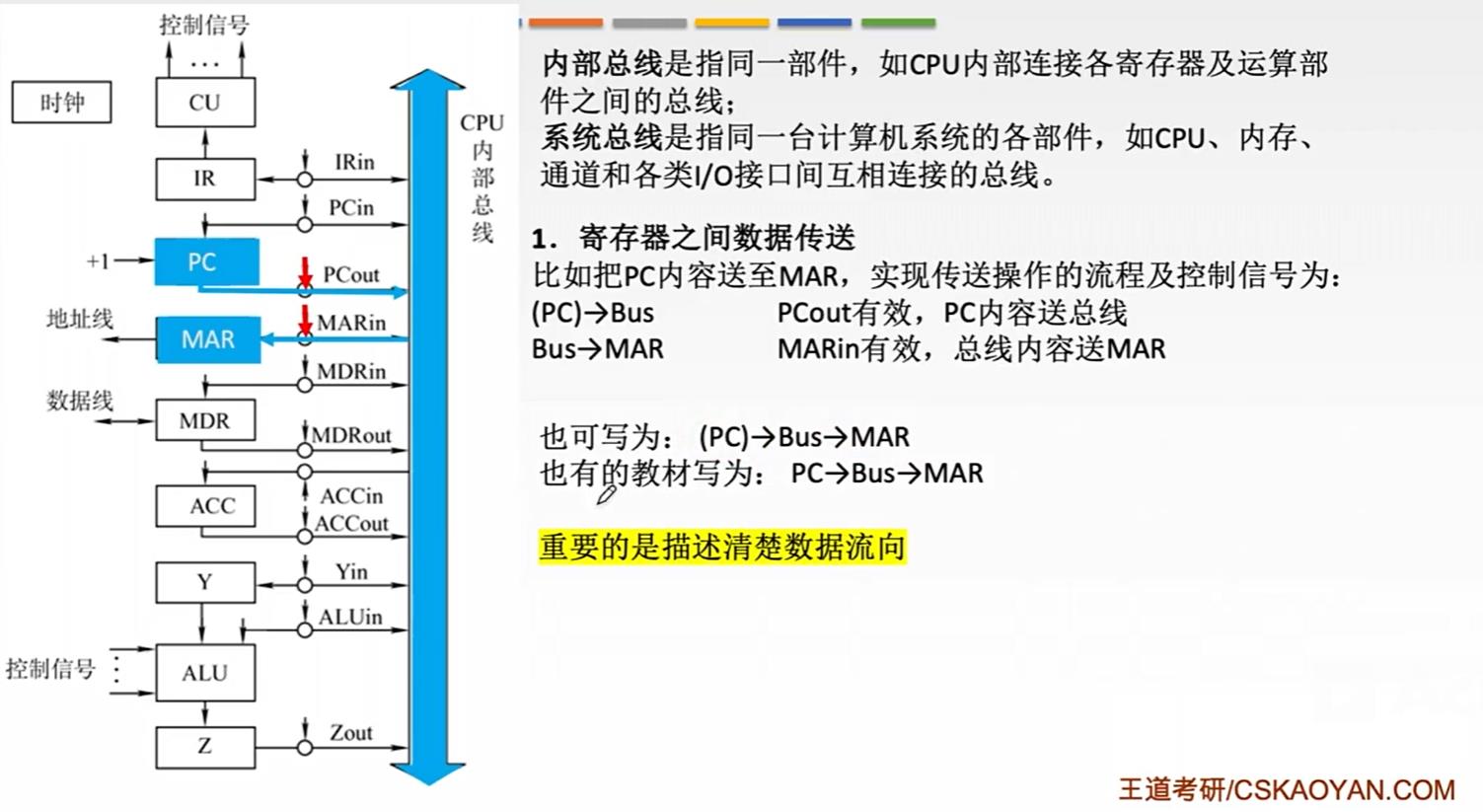

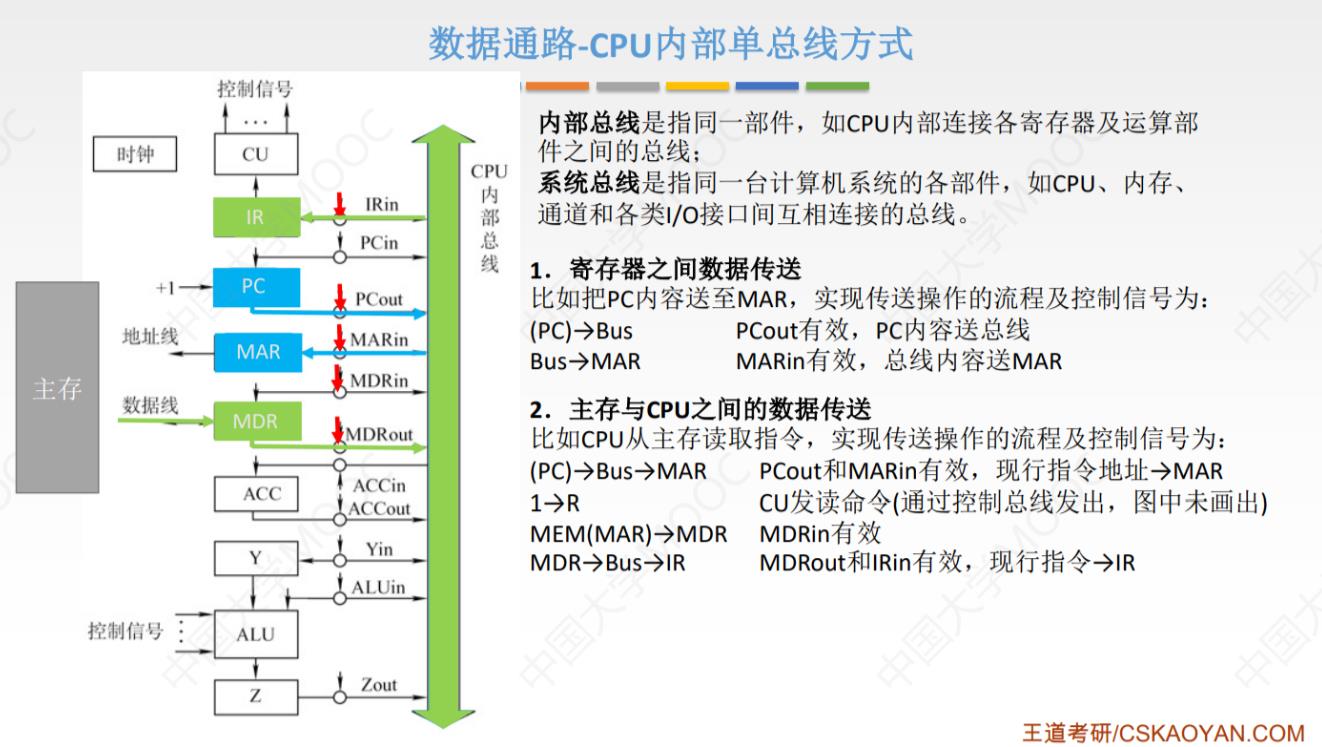

单总线结构

1. CPU内部单总线方式

数据流动的三个主要情况:寄存器与寄存器、寄存器与主存、寄存器与ALU,下面分别讨论三种情况;

复习:在CPU中至少要有六类寄存器:指令寄存器(IR)、程序计数器(PC)、地址寄存器(AR)、数据寄存器(DR)、累加寄存器(AC)、程序状态字寄存器(PSW)。

① 寄存器与寄存器之间的数据传送

内部总线:同一部件,如CPU内部连接各寄存器及运算部件之间的总线

系统总线:同一台计算机系统的各个部件,如CPU、内存、通道和各类I/O接口间互相连接的总线。

理解:上图所示是把PC(程序计数器)中的内容发送至MAR(地址寄存器)中。CU(控制信号)会有电路连接在XXin和XXout,进而对数据流进行控制。(Bus是总线的意思)

(PC)--->Bus-->MAR(一般要给PC加上括号,加上括号是不会有错的,不加会有一定的风险)。

② 主存与CPU之间的数据传送

主存与cpu之间数据传送

理解:需要CPU从主存中读取指令,实现传送操作的流程及控制信号:

首先程序计数器会指明我们的所需要读取的指令存放在主存中的地址,因此要完成将PC内容送至MAR中,也就是第①步(寄存器与寄存器之间的数据传送)。

得到地址信息后,会撤销PCout和MARin,紧接着CU会给主存发送(1->R)读的操作,这时候CU会通过控制总线将MARinE中的地址信息通过地址线发送给主存。

主存通过地址信息MEM(MAR)->MDR,通过CU控制总线的控制将MDRinE打开,将数据保存到MDR中。

所以主存与cpu之间数据传送这张图中的MDRin有效是有一些问题的,它的意思是MDRinE有效,及主存与MDR之间的数据传送线是有效的。

最后MDR->Bus->IR就不再说明了。

③ 执行算术或逻辑运算

专用通路结构

【讨论】专用数据通路方式在 取指周期 的步骤

章节回顾

硬布线控制器

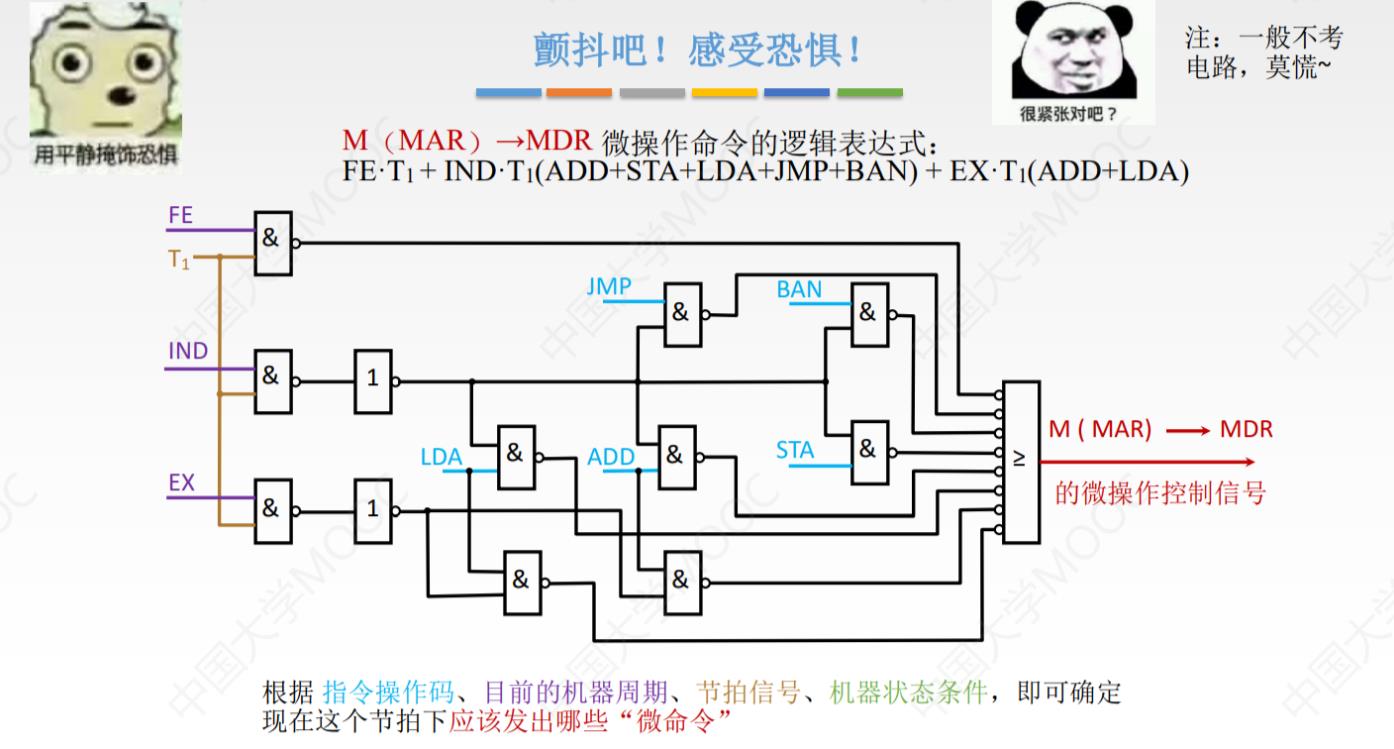

硬布线控制器,用 纯硬件 的方式实现控制器的功能;

微命令 是工作要求, 微操作 是具体工作;

一个节拍内可以 并行 完成 多个 相容的 微操作;

原理很像 逻辑公式表 ,例如: C 1 = FE · T 0 ;

当机器周期处于 FE取值周期,且在该周期的 T 0 节拍时,所对应的微操作就是 C 1 ;

下图就是本节的学习目标,不过考试不会考这么难;

紫色的线是 机器周期信号 ;

棕色的线是 节拍信号 ;

蓝色的线是 指令操作码信号 ;

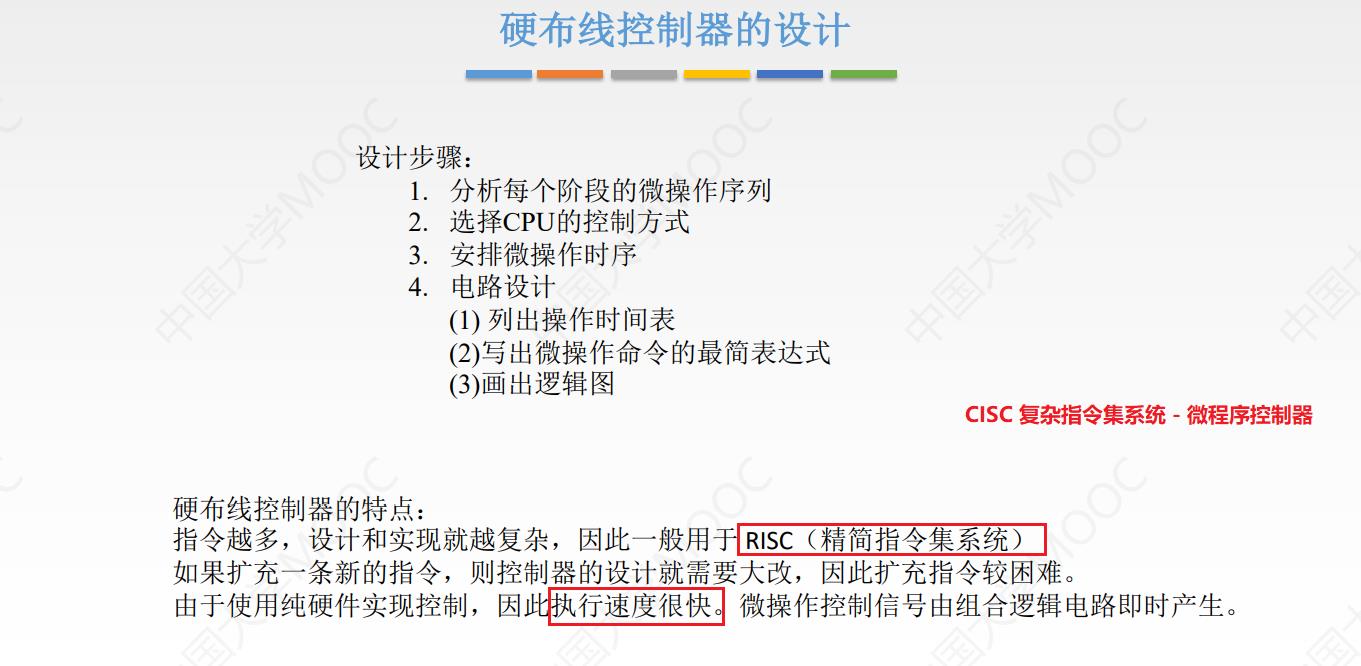

硬布线控制器的设计

本节的重点: 硬布线控制器的设计 ⭐

1. 分析每个阶段的微操作序列

2. 选择CPU的控制方式

产生不同微操作命令序列所用的时序控制方式;

(1) 同步控制方式

任意微操作均由同一基准时标的时标信号控制;(例如:15分钟后下课)

CPU把地址、数据和控制信号给内存后,会自动的隔一段时间区去取数据;

① 采用 定长 的机器周期

以 最长 的微操作序列 和 最繁琐 的微操作为标准机器周期;

优点:控制简单;

缺点:例如规定一个CPU周期4个节拍。有时执行完2个节拍就结束了,却还需要等待4个节拍结束;

② 采用 不定长 的机器周期

机器周期内节拍数不同,需要的多就延长,需要的少就减少;

③ 采用 中央控制 和 局部控制 相结合的方法

节拍数只延长,不减少;

(2) 异步控制方式

采用应答方式、无基准时标信号、无固定的周期节拍和严格的时钟固定;

(3) 联合控制方式

同步、异步相结合;

3. 安排微操作时序

① 取指周期

② 间址周期

③ 执行周期

④ 中断周期

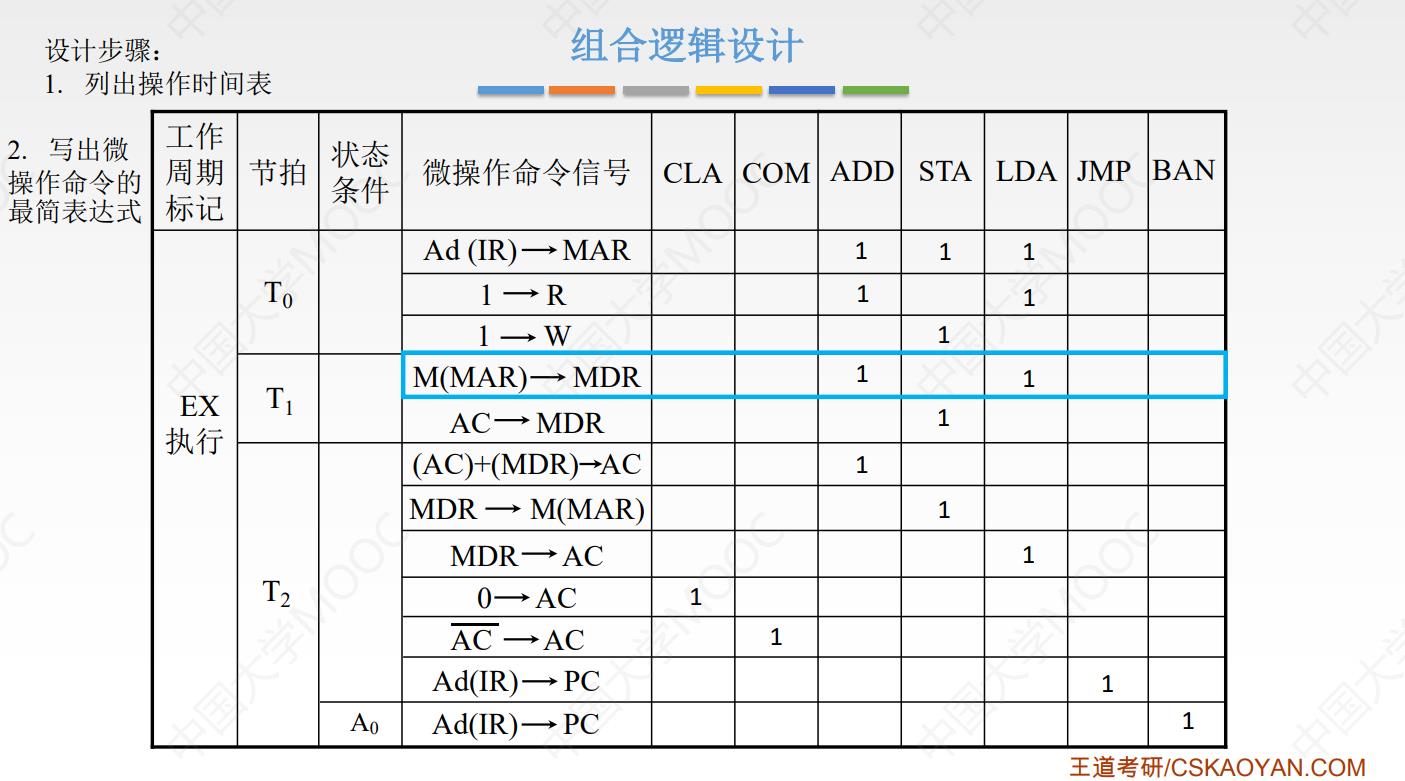

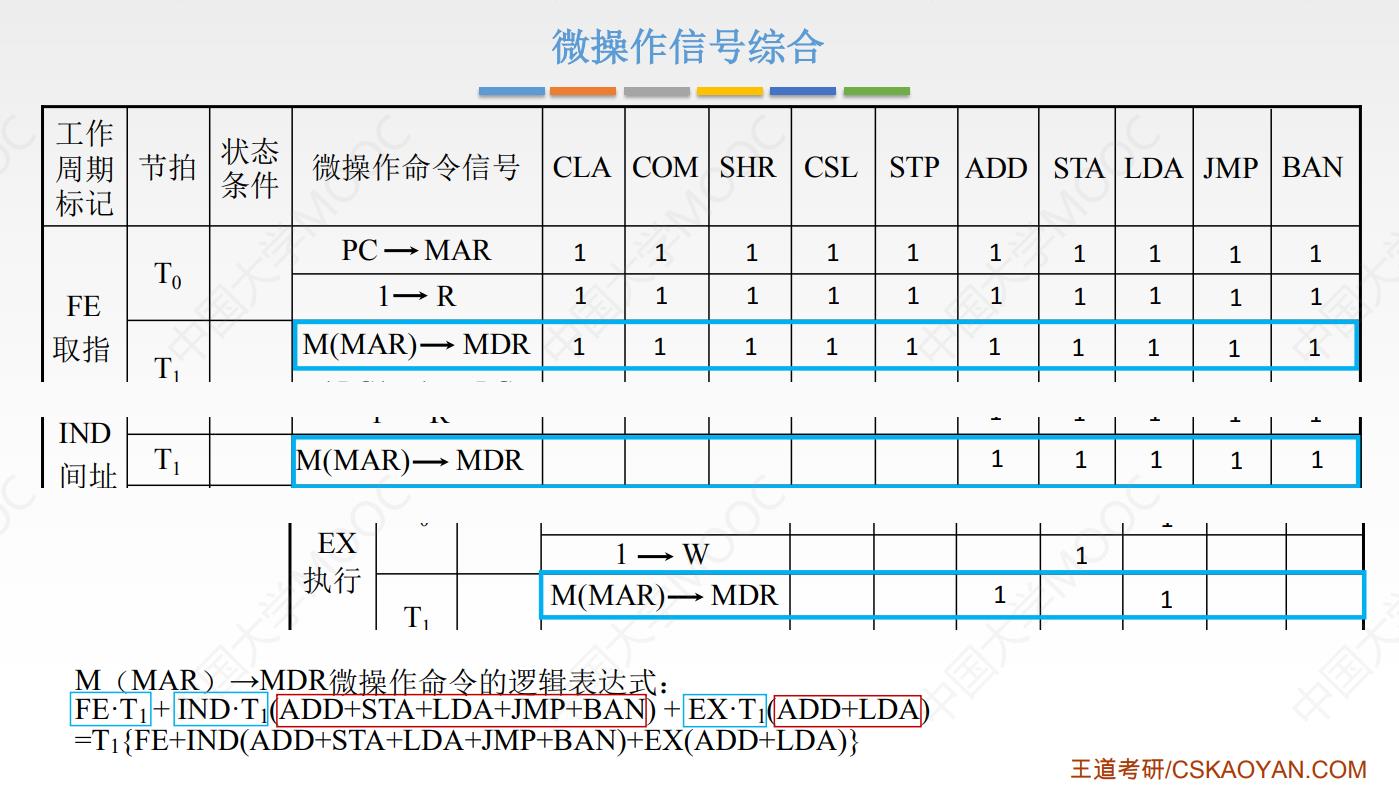

电路设计 - 组合逻辑设计

① 列出操作时间表

② 写出微操作命令的最简表达式

③ 画出逻辑图

小结

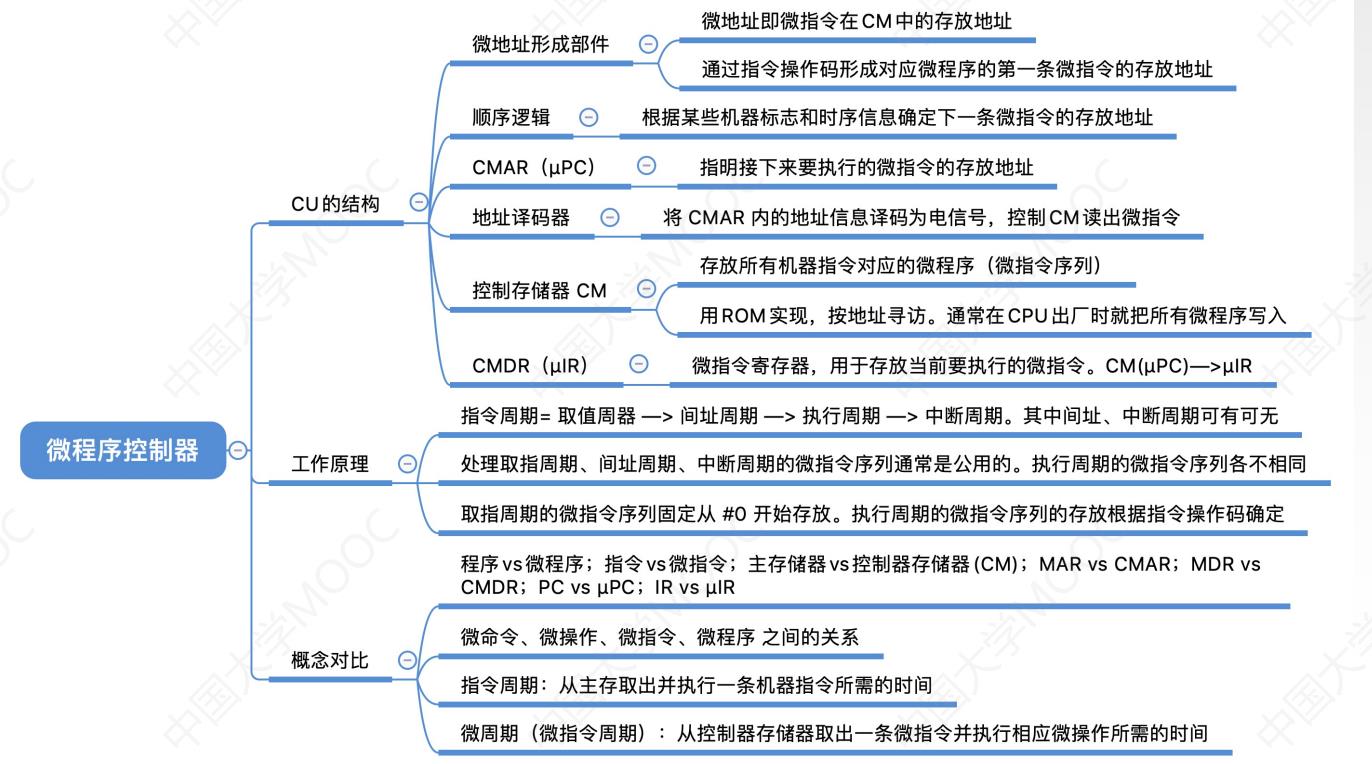

微程序控制器

硬布线控制器 虽然很难,但不是考试的重点,微程序控制器 大题有可能考察;

1. 微程序控制器设计思路

组合逻辑电路设计:用 门电路 直接进行控制;

微程序电路设计:仿照程序思想,由 控制存储器 发出控制信号;

程序员编写的代码,被翻译成一系列机器指令;

每条 机器指令 的执行包含多个阶段,每个 机器阶段 需要执行多条微指令,每条 微指令 由多个 微操作 构成;

【注意】

微命令 与 微操作 一一对应;

微指令 中可能包含 多个 微命令 ;

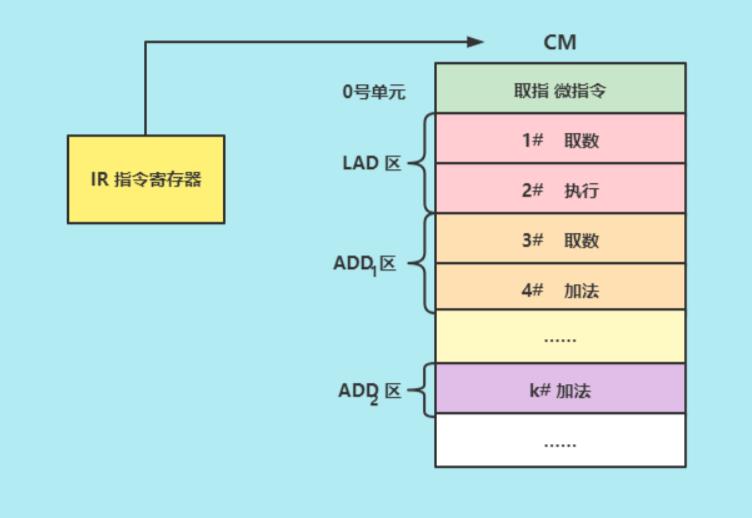

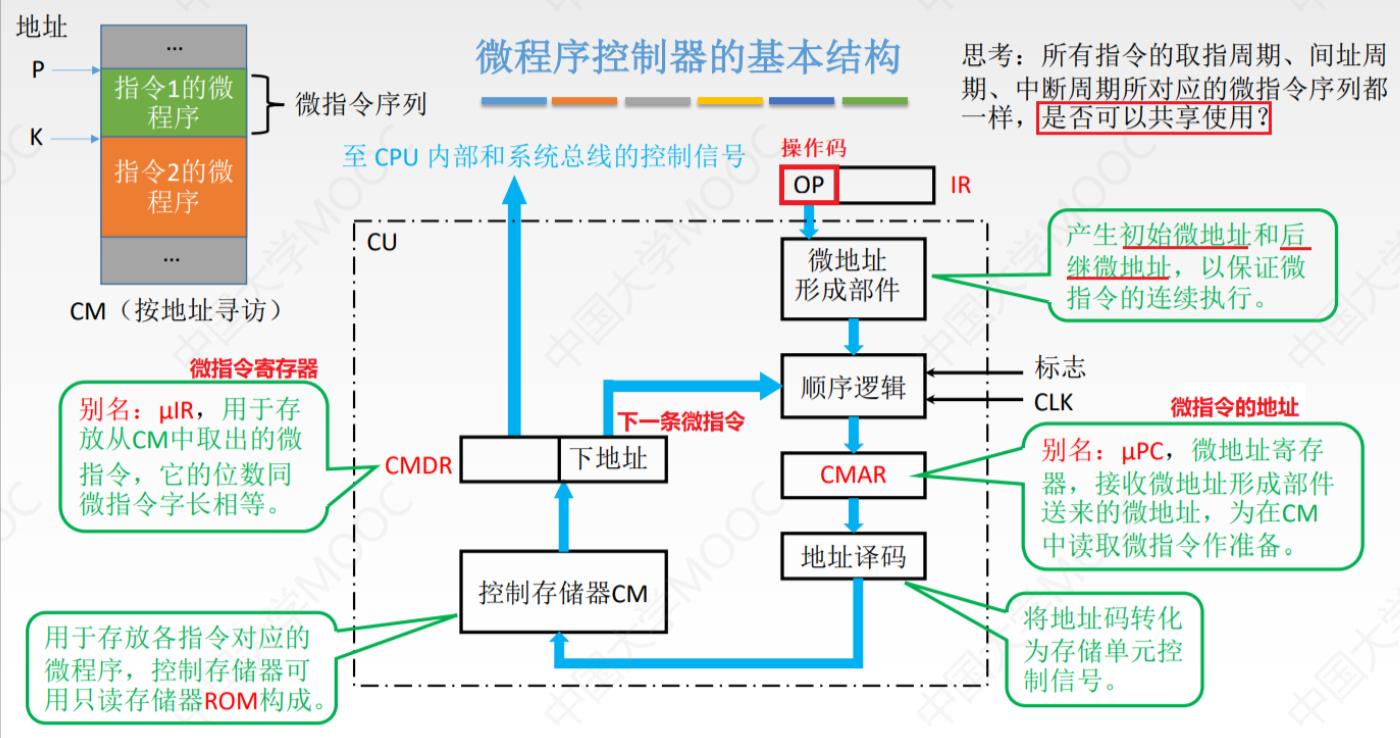

2. 微程序控制器的基本结构

重要部件: 控制存储器 uCM ,存放各指令对应的微程序;

CM被分为若干个区域,每个区域对应一条机器指令在执行过程中,除 取指微指令 之外的微指令;

ADD1 R1 ,(R2) ,需要两条微指令(取数 + 加法);

ADD1 R1 ,R2 ,只需要一条微指令(加法);

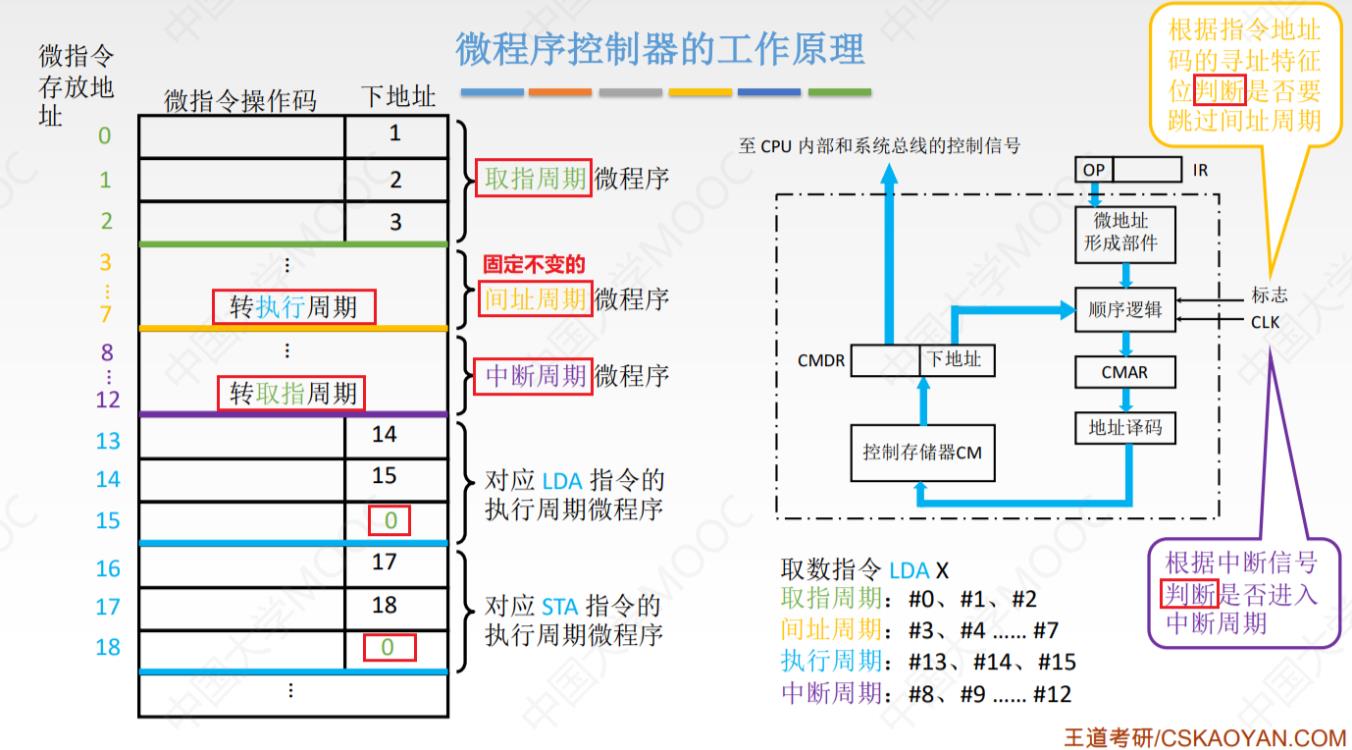

3. 微程序控制器的工作原理

下图中的 LDA X 指令是缩写,实际含义是 Load ACC X ,把X里的数据放进ACC里去;

由于机器指令LDA X可能不需要通过间指周期寻址,因此会有标志位指明并进行判断。

小结

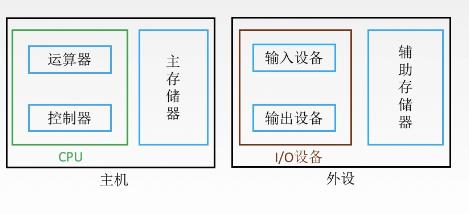

王道计算机组成原理笔记4 CPU及工作过程IO设备

功能部件—运算器和控制器

通常把运算器和控制器合在一起称为中央处理器,简称CPU。

计算机的工作过程—取数指令

功能部件—I/O设备

以上是关于计算机组成原理王道中央处理器学习笔记的主要内容,如果未能解决你的问题,请参考以下文章

专栏必读王道考研408计算机组成原理万字笔记(有了它不需要你再做笔记了):各章节内容概述导航和思维导图