DP/eDP协议学习--视频传输格式

Posted 九月庭月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DP/eDP协议学习--视频传输格式相关的知识,希望对你有一定的参考价值。

接上篇文章control symbols插入规则

协议里面关于对这部分还是讲的很清楚,但如果真的要实现,也没那么容易,因为支持得格式太多了。这里还是要简单介绍一下,不然总感觉漏了一部分。

视频数据流传输格式

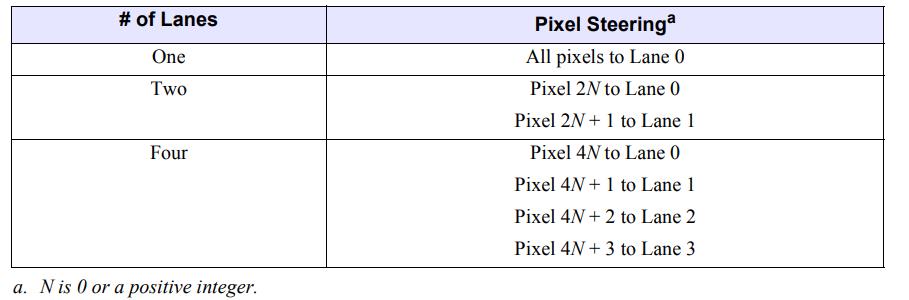

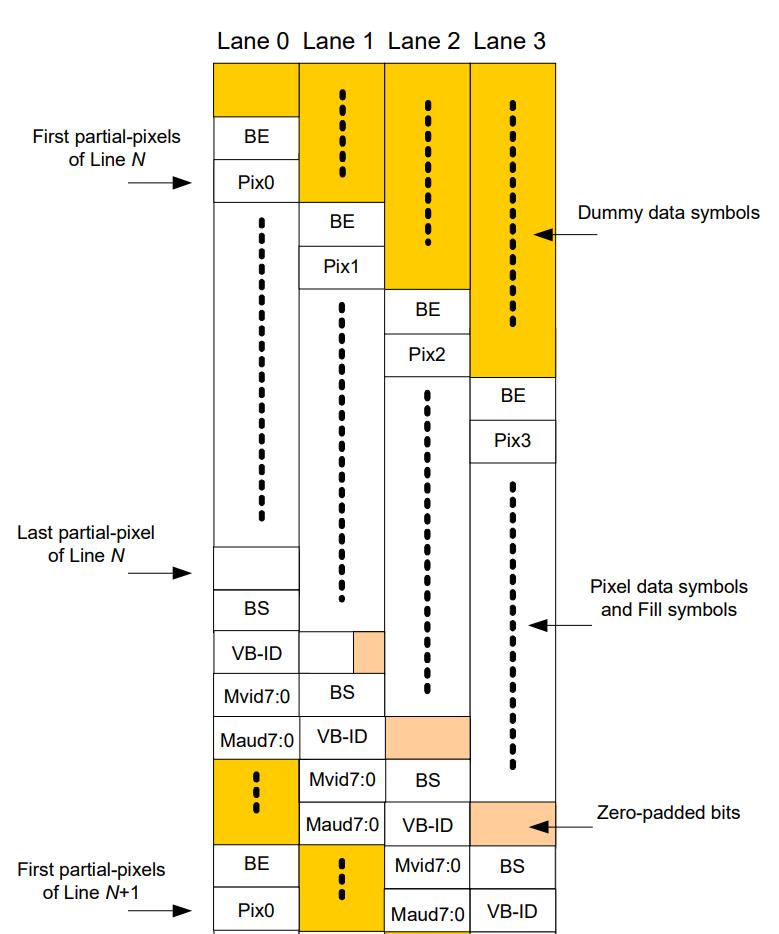

如下图所示,不同的lane数量和像素的传输有一定的关系,如:使用4条lane,4N像素职能在lane0传输,即使在10ppc时,也不能把剩余的bit放在lane1传输,这个规定实际上简化了Tx和Rx的实现。

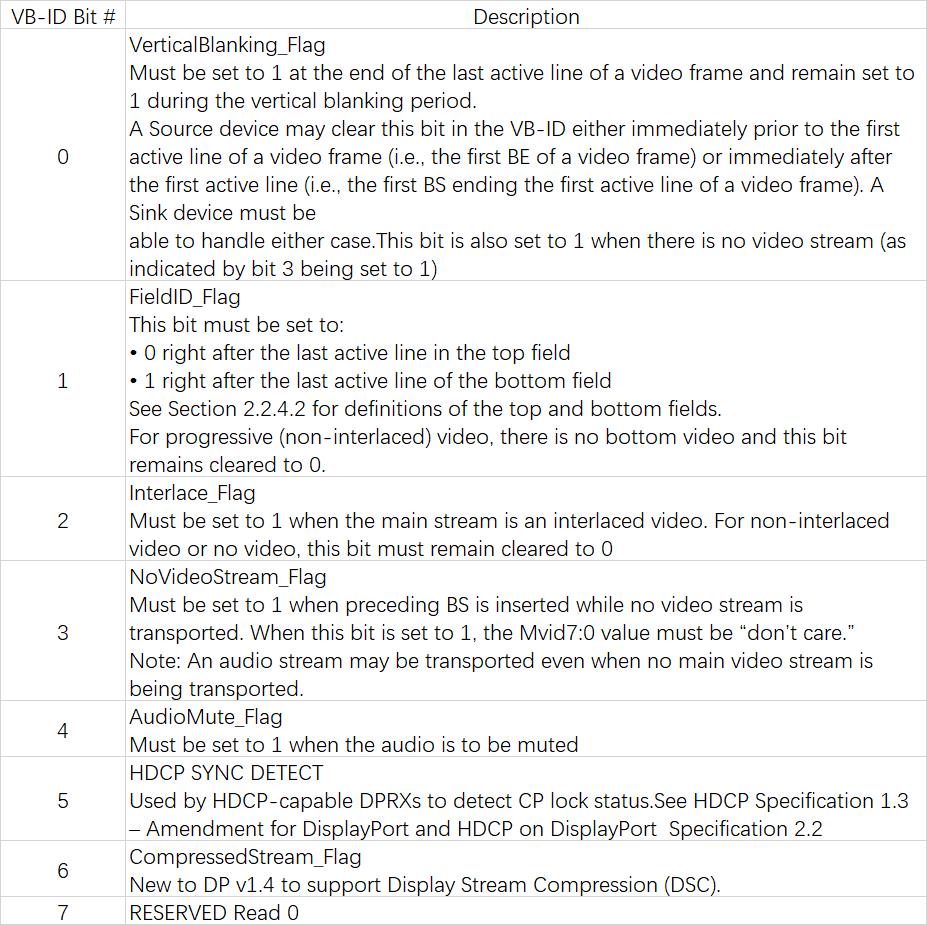

协议中规定BS后面必须跟着VBID+MVID+MAUD,VB-ID的定义如下图所示:

根据该定义可知,VB-ID可能随时在变化,最少vertical blanking区域和vertical display区域是不一样的,这里实现直接用组合逻辑就行:

always@(*)begin

vbid[0]=逻辑;

vbid[1]=逻辑;

。。。。

vbid[7]=reserved;

end

还有一个重要规则是,无论使用几条lane,BS+VB-ID+Mvid+Maud都要发送4遍。这个规则应该就是增强鲁棒性,大家看视频的时候应该能体会到,人感知音频比视频敏感,所以后面协议介绍音频数据传输是有校验的,视频数据是没有校验的。同理,这些控制位要是出错了,那RX就别想解对数据。协议后面还讲到lane数据之间要有skew,也是为了增强鲁棒性,防止高频脉冲把同一时刻的所有数据都影响了。

另外这个还涉及到一个功能的实现-------在无视频传输的情况下,每条lane上,每8192个symbols要插入一个BS(上篇文章讲过),也就是每8188个symbols插入一个“BS+VB-ID+Mvid+Maud”

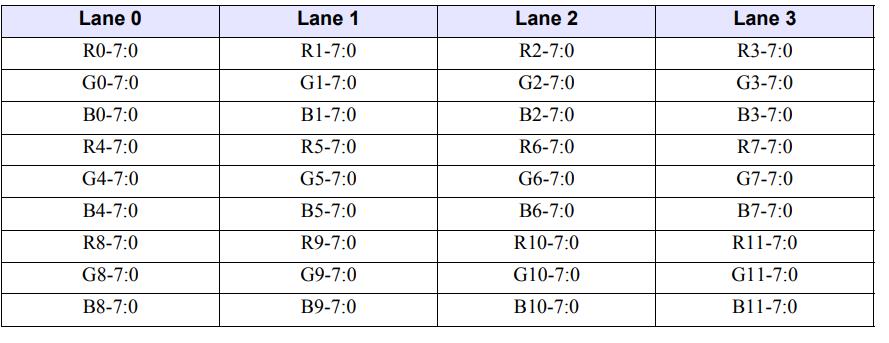

8bpc RGB/YCbCr 4:4:4 (24 bits per pixel)

相信大家都喜欢这种规则的排序

可是现实如果都是这么简单,DP协议的逼格何在!!!

10bpc RGB/YCbCr 4:4:4 (30 bits per pixel)

For YCbCr 4:4:4, replace R with Cr, G with Y, and B with Cb

我所接触项目的色深也就这两种,也是现在大部分视频的色深吧。

这里还有一个实现技巧:

就是无论色深是多少,先把有效像素截位,然后按照要求顺序拼在一起送你FIFO,这要读的时候按照8bit截取就好了。

!!!最重要的提示:

协议中规定,link_clk是链路速率的10分之一,也就是说当链路速率是5.4Gbps时,link_clk就是540MHz。但是DP1.4a中,当链路速率为8.1Gbps时,link_clk时810MHz,这个即使在14nm工艺下,芯片的时序也是难以承受的。所以可以在一个时钟周期产生4个symbols,这样link_clk就时链路速率的40分之以一,即使链路速率到了20Gbps,500MHz对于芯片时序还是完全可以接受的。

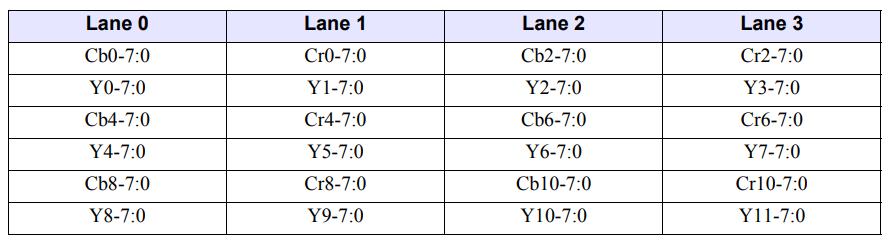

8bpc YCbCr 4:2:2 (16 bits per pixel)

10bpc YCbCr 4:2:2 (20 bits per pixel)

YCbCr444和YCbCr422区别请参考YCbCr444和YCbCr422区别

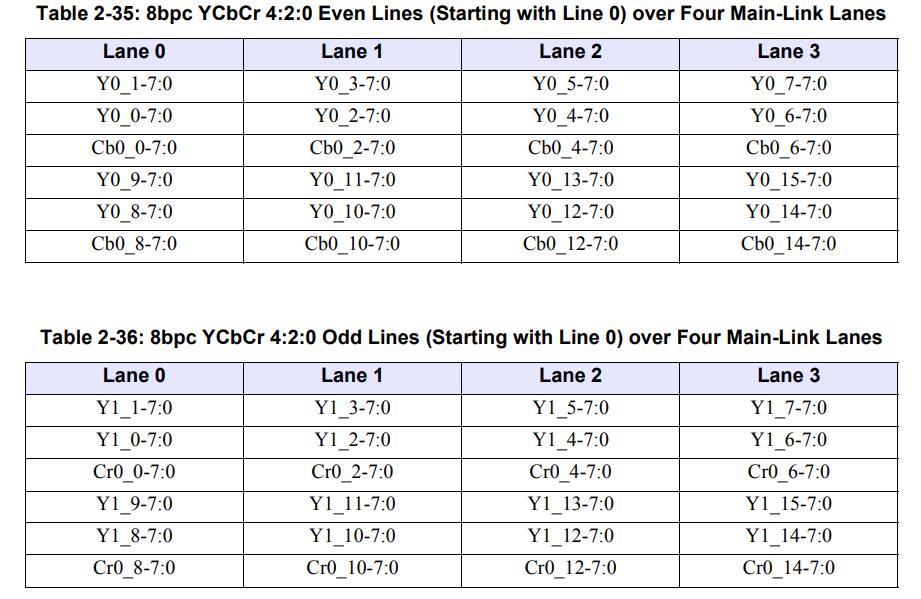

8bpc YCbCr 4:2:0 (12 bits per pixel)

YCbCr420这个比较有意思,一般情况下DP的视频数据接口是48bit的,对于420来说有些浪费,所以在实现的时候,可能Tcon的数据是Cb+Y0+Y1,这个时候像素时钟是减半的。

FS/FE的插入

diFS与FE时为了像素输入速率与发送速率的平衡,像素的打包速率只能小于等于发送速率,如果时小于,那么肯定要插入FS/FE。

这里面讲了TU中active symbol的计算协议简介

Inter-lane Skewing

inter-lane skewing就是在最终输出时,每条lane要有两个时钟的skew,其目的就是防止高频噪声的干扰。

DP/eDP协议学习--协议简介

最近一段时间由于项目接触到该协议,该协议不像HDMI,USB资料那么多,虽然应用还是很广泛的,但是生态不是很好。自己看了一段时间的协议,想着记录下来大家一起讨论学习。

1综述

eDP(Embedded DisplayPort)是数字显示技术领域的标准协议,其创始者为视频电子标准协会(VESA),创始成员包括戴尔、惠普、三星、飞利浦以及英伟达等。eDP协议是针对DP(Display Port)应用在嵌入式方向架构和协议的拓展,所以eDP协议完全兼容DP协议。相对于DVI/HDMI来说,eDP具有高带宽、整合性好、相关产品设计简单,该接口已广泛应用于笔记本电脑、平板电脑、手机等其它集成显示面板和图像处理器的领域。eDP接口降低设备复杂性,支持关键跨行业应用程序的必要功能,并提供性能可伸缩性,以支持具有更高颜色深度、刷新率和显示分辨率的下一代显示器。

eDP是被设计来取代比较旧的数字影音传送界面如LVDS,尤其在全高清PHD(1920x1080或1920x1200)或超过FHD解析度的面板上。

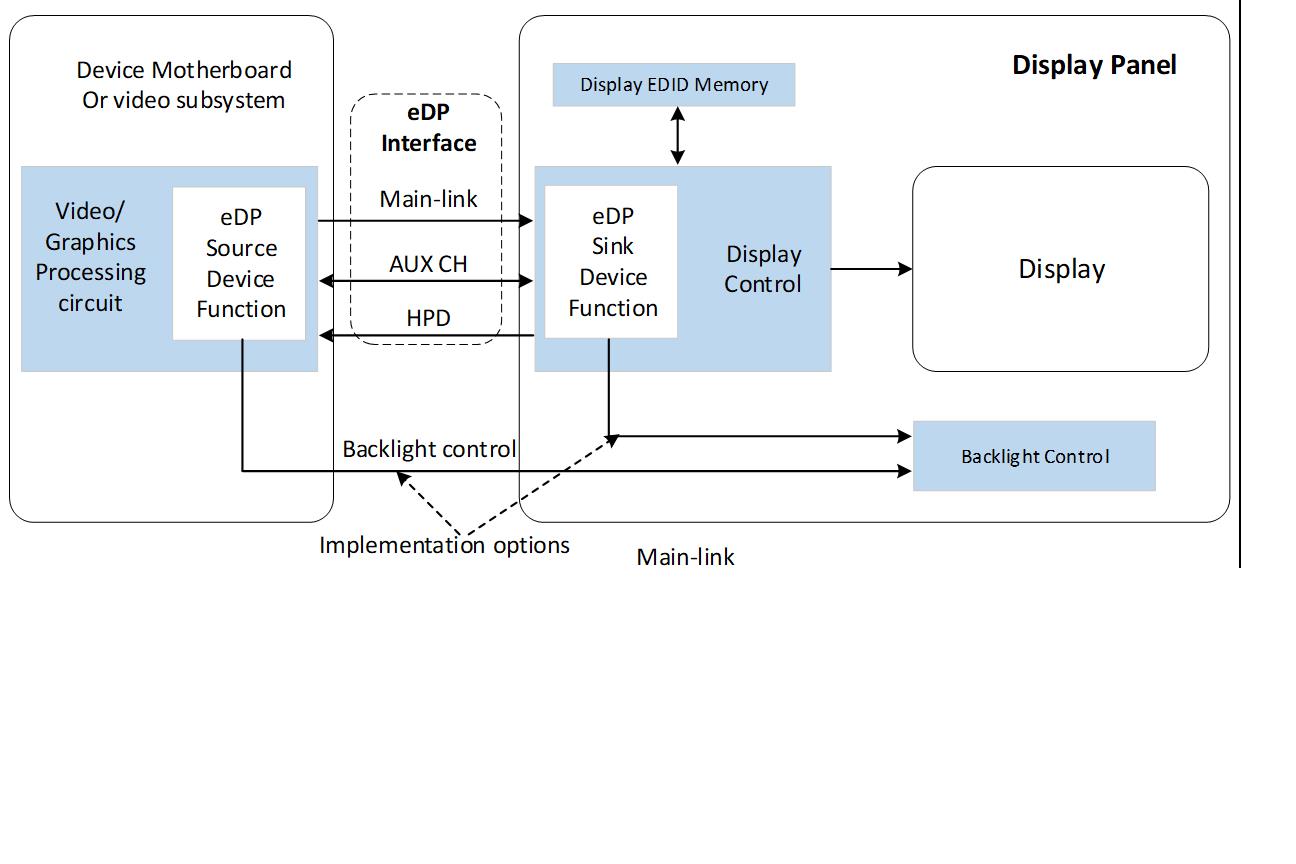

eDP具有三大基本架构包含影音传输的主要通道(Main Link)、附属通道(AUX)、与热插拔(HPD)。

Main Link:用来传输各种类型的视频数据和音频数据,Main Link由1~4对差分线构成,这些数据线是单向的,从source指向sink。每对差分线采用交流耦合技术,发送端与接收端可以具有不同的共模电压,因此可以把接口做的更小。数据采用ANXI 8B/10B编码方式,eDP1.4中每条lane的速率最大为5.4Gbps,最小为1.62Gbps。没有专门的时钟线,时钟从数据中恢复。对于一款液晶屏而言,Main Link具体需要几对数据线,取决于屏幕的分辨率和颜色位数。

AUX:是一条独立双向半双工的传输通道,它也是一对差分信号线。其数据传输速率最大1Mbps,用来传输配置参数与指令。该通道提供Link Services和Device Services。具体来说它与EDID及DPCD存储器相连,并通过总线方式读写。其中EDID为显示标识数据,用于存储显示器的相关参数。DPCD为eDP接口配置数据,与链路管理层相连,用于链路层面的配置。

HPD:该项功能在eDP中是可选的。与DP一样,eDP支持与此信号相关的所有功能,包括中断以及链路故障通知。如果不使用HPD功能,source端可以通过轮询的sink方式来检查链路的完整性,但是这种方式会增加source的功耗,所以还是推荐使用HPD的方式。

支持2~8声道音频传输,支持非压缩和压缩格式,非压缩格式LPCM最大支持192KHz采样率(bit rate<=6.144Mbps),压缩格式(IEC61937)支持384KHz与768KHz两种采样率。

下图给出了eDP系统的基本框图。

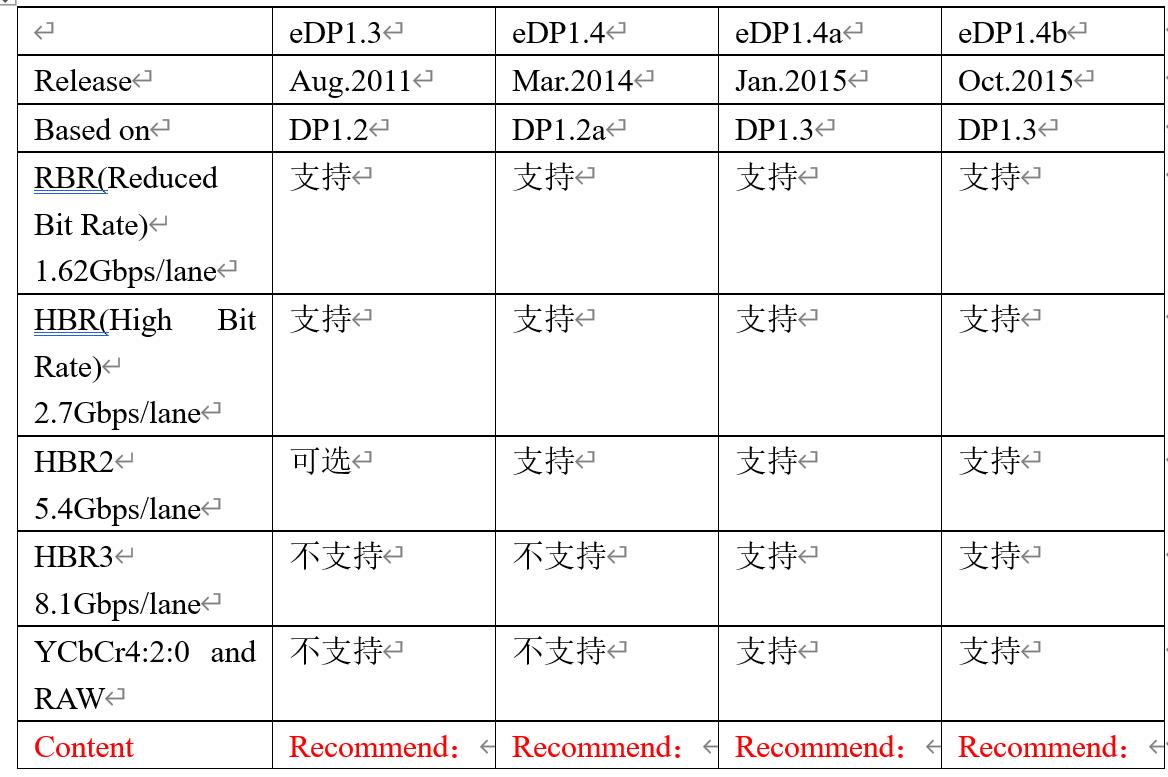

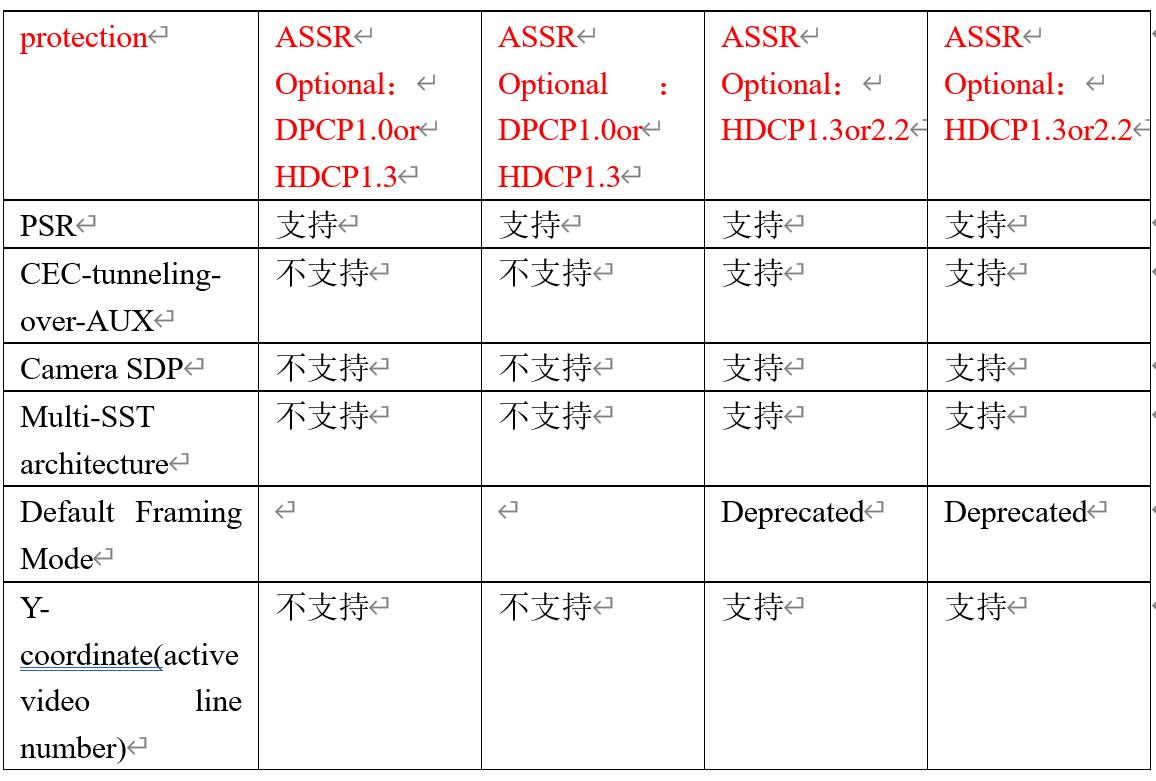

2 各版本特性比较

注:由于eDP时嵌入式的应用场景。所以一般不使用HDCP,而且嵌入式的屏幕也没有支持HDCP。对于eDP只需要使用ASSR(加扰)就行。

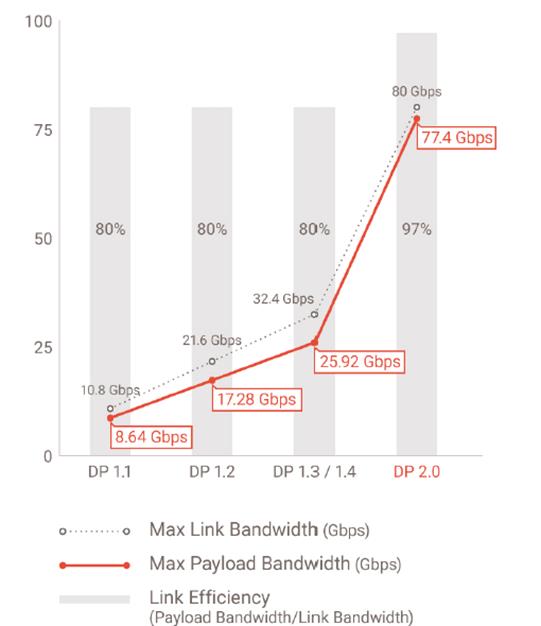

3 性能计算方法

3.1. Lane与rate的需求计算

以1920x1080@60Hz计算,其像素时钟为148.5MHz,如果传输像素单元为24bpp,则其传输带宽为:

148.5MHz24bpp=3.564Gbps

eDP 1.4支持最大单lane 5.4Gbps,其传输有效数据带宽为:

5.4Gbps0.8=4.32Gbps

结论:单lane 5.4Gbps 即可满足传输需求;

3.2. 基本传输单元(TU)插入空闲字符的个数

为了避免link 带宽过载,数据的打包速率只能等于或者小于link symbol的速率,如果是小于的情况,则需要传输空闲字符,空闲字符放在FS与FE之间。一个基本传输单元具有32~64个link symbol,而且在传输过程中不能改变。

假如显示规格为1920x1080@ 60Hz,24bpp,strm_clk=148.5MHz,采用2.7Gbps,4lane传输,TU的大小固定为64

Packt data rate=148.5*24/8/4=111.375MHz;

平均每个TU中有效数据的个数=(111.375M/270M)*64=26.4;

所以单lane中TU的大小为64,active symbol为27个。

!!!下篇我会写DP特殊字符的插入规则与时序。

以上是关于DP/eDP协议学习--视频传输格式的主要内容,如果未能解决你的问题,请参考以下文章