PCB模块化设计10——PCI-E高速PCB布局布线设计规范

Posted 朱万利

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了PCB模块化设计10——PCI-E高速PCB布局布线设计规范相关的知识,希望对你有一定的参考价值。

目录

PCB模块化设计10——PCI-E高速PCB布局布线设计规范

PCI-E是英特尔在2001年提出的一种取代以前的PCI、AGP的计算机内部互联总线标准。特点是串行(以前的ISA、PCI、AGP等都是并行的),并且支持1到32条通道(然而常见的最长的就是显卡上最常用的X16)。

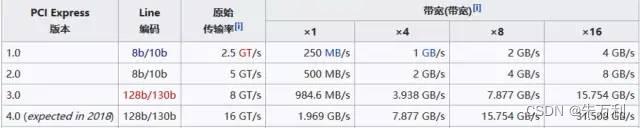

几种PCI-E速度表

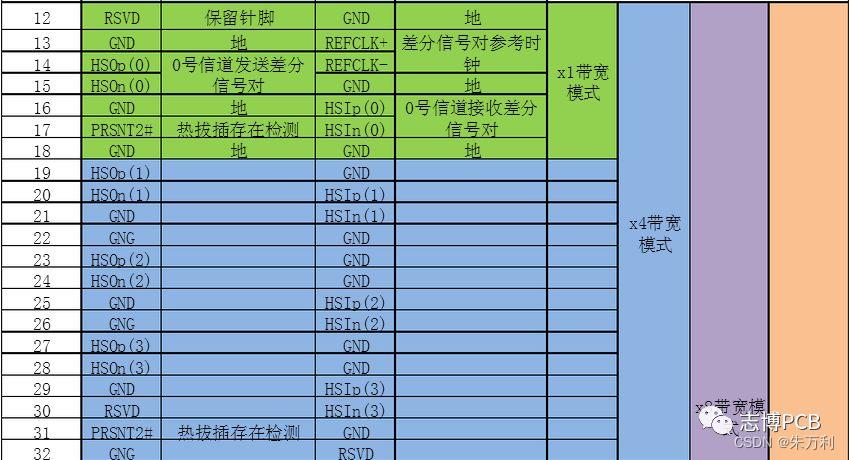

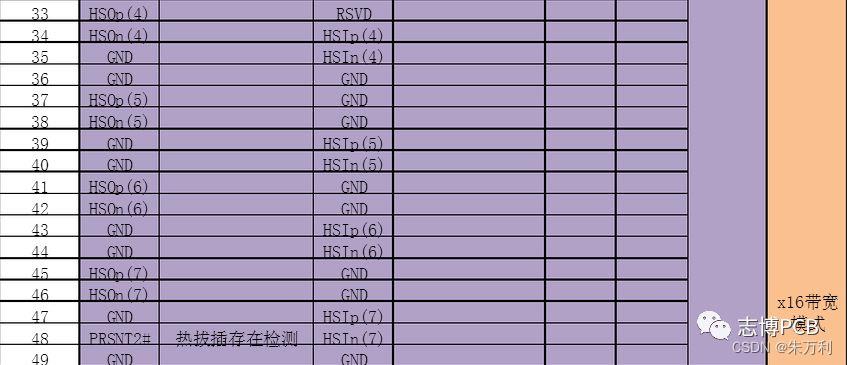

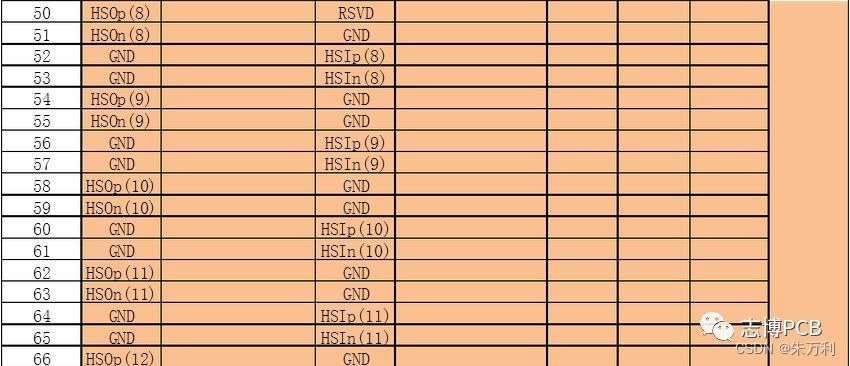

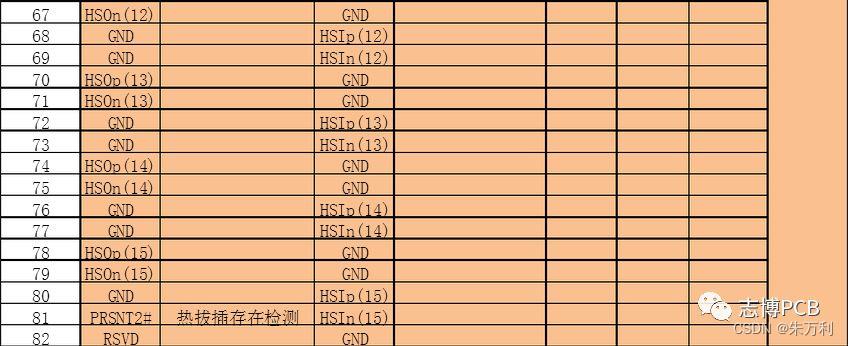

1、PCI-E管脚定义

有4种接口尺寸,每种接口的1到11对引脚都是一样的,剩下的是差分数据线和时钟,数据线数量不同对应的PCIe尺寸也不一样,X1的PCIe板子可以插在X4的插槽上。

由于PCI-E传输的信号是差分信号,所以这里有必要讲解一下差分线的定义:

相位信号和单端信号对比:传统的单端信号通过相对于地线的电势差的高低来传递,所以只需要一根地线就可以,传递几路信号只需要相应数量的信号线就可以了;而差分信号使用一根公共地线(电势为0),传输一路信号时,需要两根信号线,一根相对于地线的电压是正的(电势为正),另一根电压为负的(电势为负),绝对值相同(相位相差180度),用两根信号线的电势差高低来传递信号,只不过传递两个信号,假如一根信号线为3.3V,另一根信号线就是-3.3V,地线是0。这种看似浪费线的传输方式其实有很多优势:第一,因为地线是可以控制的,所以不会因为线长带来的压降而导致地线的差异,进而可以降低传输的电压来降低功耗(早期的AGP 2X的工作电压高达5V,而现在的PCI-E已经低于1.5V了);第二,因为电磁干扰对差分信号两根信号线的影响几乎相同,即使有干扰,高电势依然相对于低电势高,而单端信号则可能因为干扰而将低电势变成高电势,导致传输错误,因此差分信号抗干扰性强。现在,大多数高速串行接口都采用了差分信号,比如USB3.0/3.1、PCI-E、HDMI、以太网等。

2、PCI-E叠层和参考平面

一般的PC主板设计成4层叠层,而服务器,工作站和移动系统主板多使用6层或是更多层的叠层。

插卡可以使用4层或是6层叠层。使用0.5OZ的镀铜微带线和1OZ的铜带状线。

插卡的整体电路板的厚度必须是 0.062inch。移动平台的PCB厚度可以是0.062inch或是0.050inch。

为了尽可能的减少损耗和抖动预算,最重要的考虑因素是设计的目标阻抗,而且要保持阻抗的公差足够小。更厚的介质层和更宽的走线将会减少损耗。

微带差分线会比带状差分线产生更大的阻抗变化。

信号对应避免参考平面的不连续,譬如分割和空隙。

当信号线变化层时,地信号的过孔应放得靠近信号过孔。

对每对信号的建议是至少放 1 到 3 个地信号过孔。还有永远不要让走线跨过平面的分割。

3、 PCB设计指南

1、阻抗要求

PCI Express的连接走线阻抗在4层或6层板时必须保持100Ω差分/60Ω单端;而对8层或10层板阻抗为85Ω差分/55Ω单端。

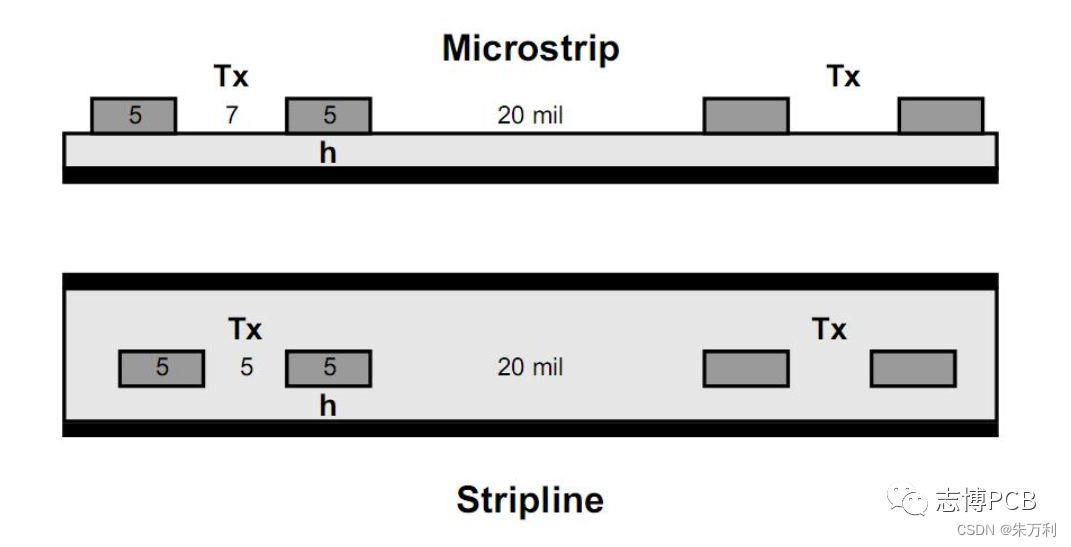

2、线宽线距

差分信号的内部耦合和增加与周边的信号间距有助于减少有害串扰的影响和电磁干扰(EMI)的影响。在微带情况下,差分线的宽度是5mil,差分对中的2条走线的间距是7mil。差分对中信号线中有100mil或超过 100mil 其信号线间距超过7mil,那么可以把信号线走成7mil的线宽。在带状情况下,差分线的宽度是 5mil,差分对

中的 2 条走线的间距是 5mil。差分对之间的距离和差分对和所有非的 PCI Express信号的距离是20mils 或介质的厚度的4倍,选择其中更大的。如果非PCI Express信号电压明显高于或者非 PCI Express 信号边缘比PCI Express 信号边缘快的话,2者的空间应增加至30 mil,以避免耦合。

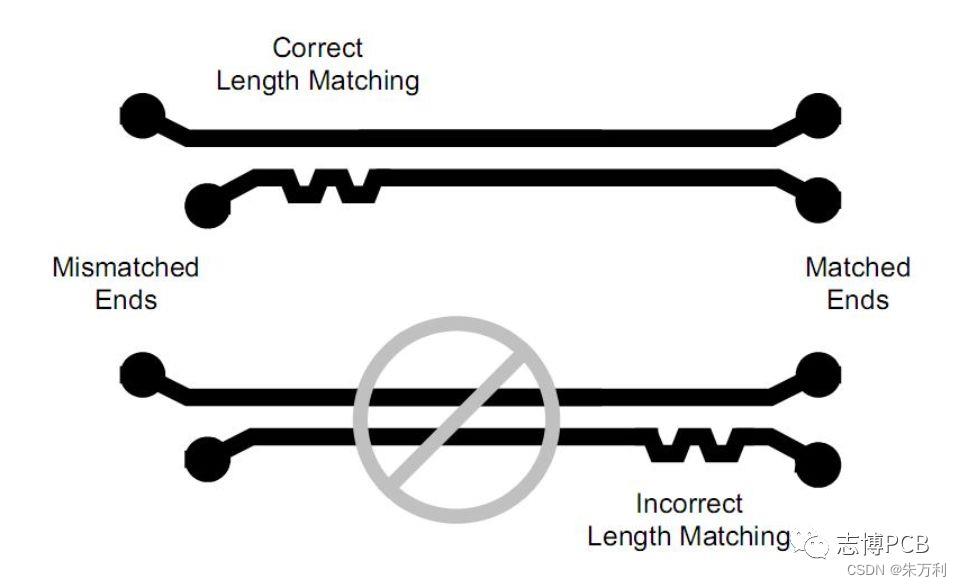

3、长度匹配

差分对中2条走线的长度的差距限制在最多5mil。

每一部分都要求长度匹配,与任何长度的增加(典型的是“蛇形线”部分)为差分线长度匹配而增加的任何长度的走线应放在不匹配出现的位置。

没有传输差分对和接收差分对长度匹配的要求(即只要求差分线内部而不是不同的差分对之间要求长度匹配)。

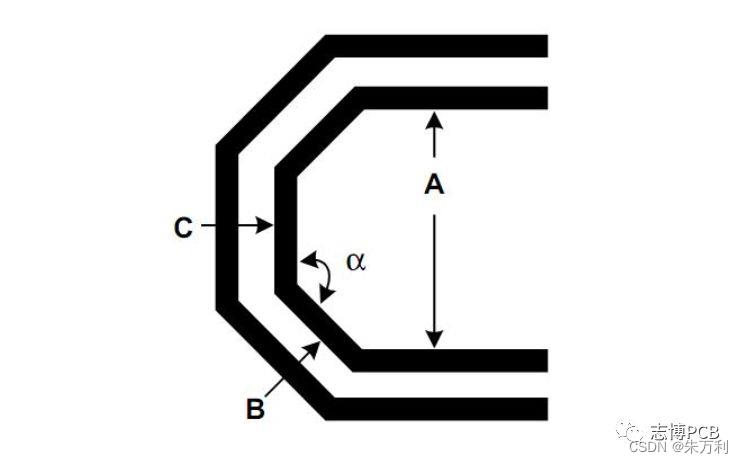

4、走线弯曲角度

应尽量不使用弯曲,因为弯曲会给系统引入共模噪声,而这将影响差分对的信号完整性和 EMI.

弯曲的痕迹应≥135°。更严格的弯曲应避免的影响,因为他们的损失和抖动预算预算。

走线的弯曲应该≥135°。应该避免小角度的弯曲因为这样的话,将会影响到损耗和抖动预算。

如果使用了弯曲,推荐使用下面的指南,以避免小角度弯曲。参见下图。

1.使所有走线的弯曲角度(α)≥135°。

2.保持走线间距( A )≥ 20 mil。

3.片段,譬如B和C,其侧翼有一个弯曲,其长度应该≥1.5 倍走线的宽度。

为了最小化长度的不匹配,左弯曲的数量应该尽可能的和右弯曲的数量相等。

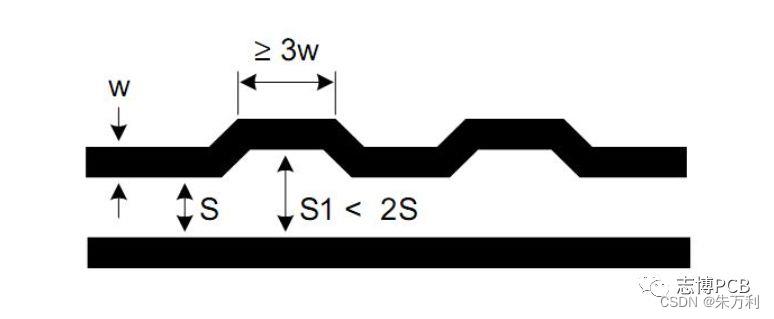

当一段蛇形线用来和另外一段走线来进行长度匹配,如下图所示,每段长弯折的长度必须至少有15mil(3 倍于 5mil 的线宽) 。

蛇形线弯折部分和差分线的另一条线的最大距离必须小于小于正常差分线距的 2 倍。

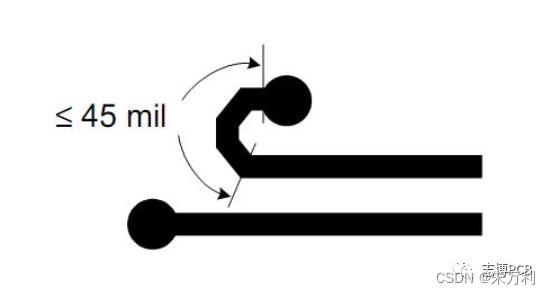

当使用多重弯曲布线到一个管脚或是一个 BGA 的焊球是非匹配部分的长度应该≤45mil。 如下图所示:

5、测试点、过孔、焊盘

信号过孔影响整体的损耗和抖动预算。每一个过孔对可能会增加0.25 分贝的损失。

还有过孔可能会限制最大的走线长度。

在 TX 差分对中最多可以使用四个过孔对。

而在 RX 差分对中最多只可以使用 2 个过孔对。

过孔应该有一个 25 mil 或更小的焊盘,

并且其完成内孔径为 14 mil 或更小。

两个过孔必须放成在一位置上互相对称的。

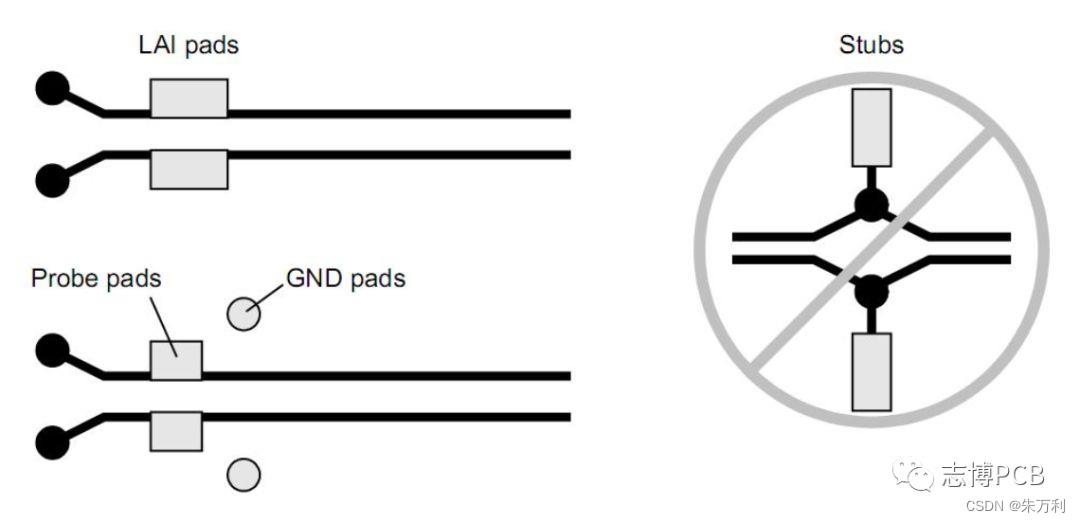

测试点(可以是过孔,焊盘或是元件)及探针脚应置于对称的系列。

不应当在差分对引入 stub。下图说明了正确和不正确的放置。

6、AC去耦电容放置方法

PCI Express 需要在发射端和接收端之间交流耦合。

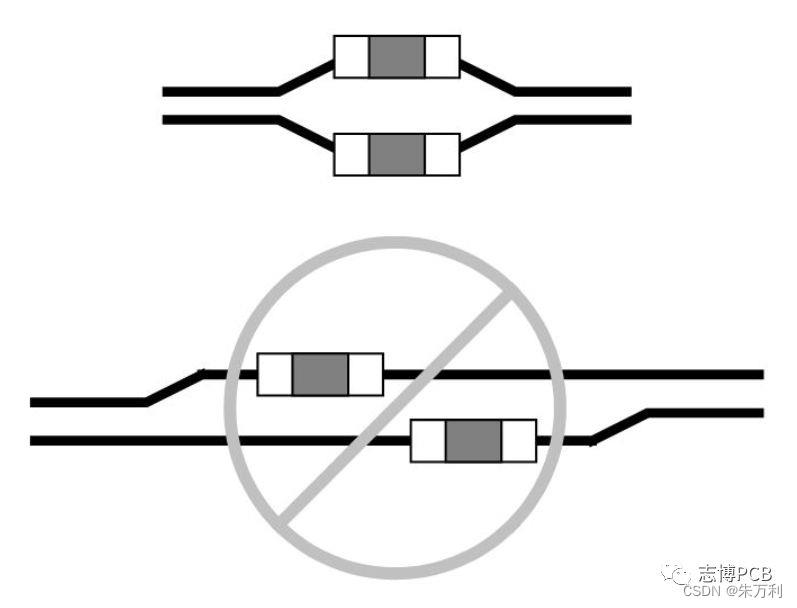

差分对两个信号的交流耦合电容必须有相同的电容值,相同的封装尺寸,并且位置对称。

如果可能的话,TX 应该在顶层走线。电容值必须介于 75nF 到 200nF 之间(最好是 100nF)。

推荐使用0402 的封装,但 0603 是可接受的。不允许使用插件封装。

差分对的两个信号线的电容器输入输出走线应当对称的。

追踪分离垫路由必须尽量减少,为了优化差分信号对之间的紧耦合,走线分离到焊盘的的长度应该尽可能的短。

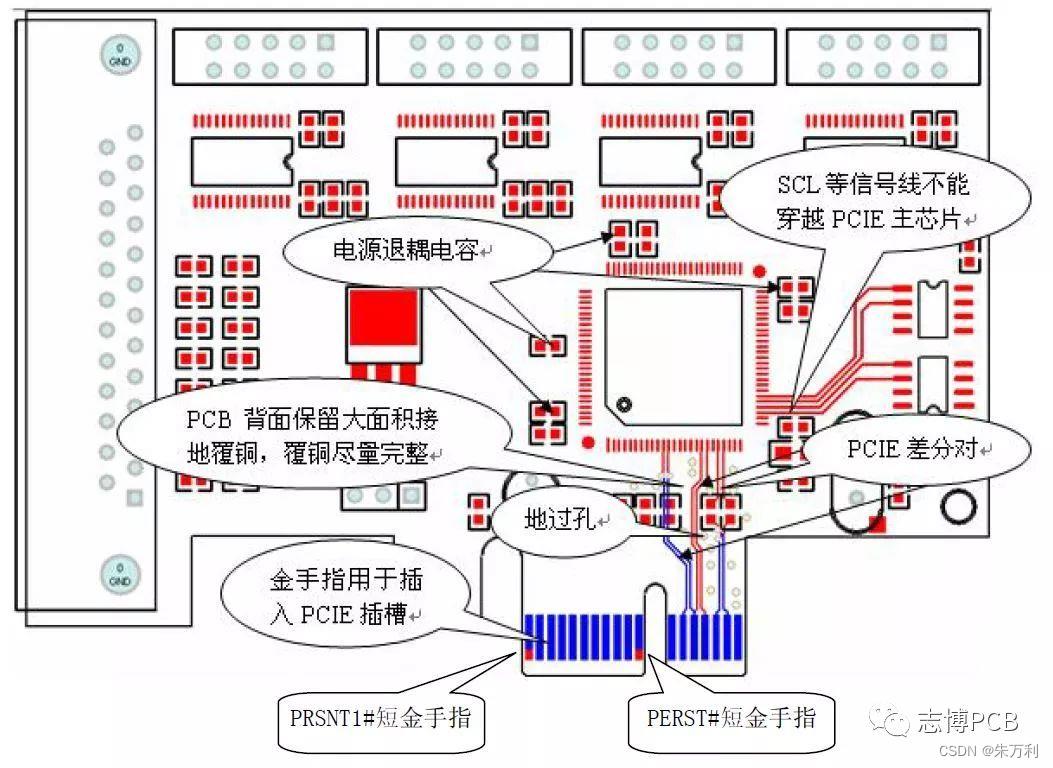

7、金手指和连接器的注意事项

参考平面的边缘手指垫应予删除,以满足阻抗的目标。这些飞机应去掉沿整个长度手指的边缘部分。

这两个痕迹的差分对线路应该成为一个领域的连接器引脚从同一层。

为了满足阻抗目标,在边缘金手指下面的参考平面应该被删除掉。

而且整个金手指下面的参考片面都要完全删除掉。

差分对的 2 个信号应该在同一层上布线连接到连接器的管脚上。

8、其他的注意事项

1、差分对反相满足3W间距,同相满足5W间距。

2、PCI-E差分线的正负两条线长度要满足匹配要求,但是差分线之间的长度并不需要匹配。

3、极性确保相反。

4、PCI-E并不支持LANE的翻转。

5、PCI-E芯片,尤其是PCIE信号线的PCB反面,应尽量避免走高频信号线,最好全GND地铺铜。

6、在PCB设计时,应该在PCIE芯片的每对电源管脚附近放置一个0.1uF左右的高频退藕电容,离芯片不能太远。

7、连接PCIE芯片的电源或者GND走线上的过孔使用大过孔、双过孔或者双回路电源。

8、将PCIE的PESET#引脚信号的金手指设计与PRSNT1#长度差不多的金手指。

9、金手指部分不允许铺铜覆盖,要每一层都进行挖铜处理。

PCB模块化设计11——VGA高速PCB布局布线设计规范

目录

PCB模块化设计11——VGA高速PCB布局布线设计规范

1、什么是VGA?

说到VGA接口,相信很多朋友都不会陌生,因为这种接口是电脑显示器上最主要的接口,从块头巨大的CRT显示器时代开始,VGA接口就被使用,并且一直沿用至今,另外VGA接口还被称为D-Sub接口。

早前大多数的计算机和外部显示设备的连接还是通过模拟VGA接口进行的,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。对于模拟显示设备,比如说模拟CRT显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像;而对于LCD、DLP等数字显示设备,显示设备中需配置相应的A/D(模拟/数字)转换器,将模拟信号转变为数字信号。在经过D/A和A/D这两次转换后,不可避免地造成了一些图像细节的损失。VGA接口应用于CRT显示器无可厚非,但用于连接液晶之类的显示设备,则转换过程的图像损失会使显示效果略微下降。

VGA连接器用于显示设备,用于将计算机连接到显示器,投影仪或电视。

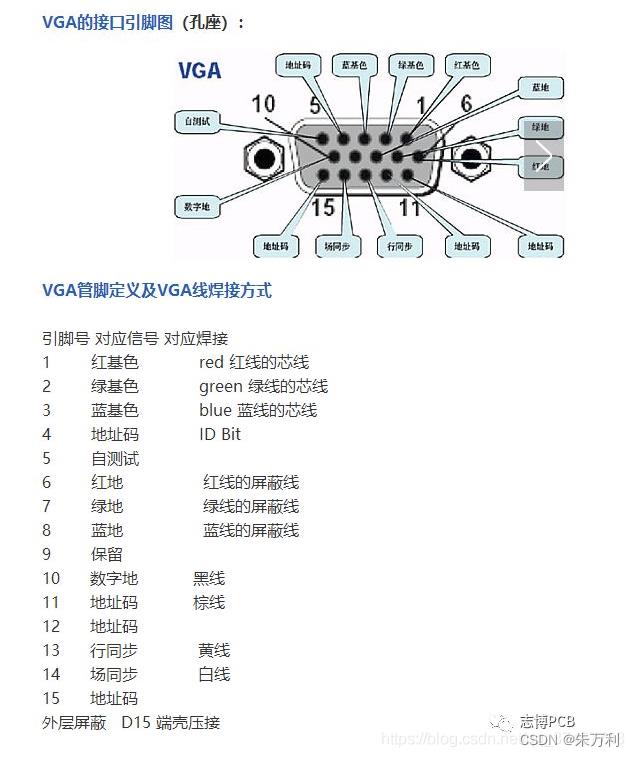

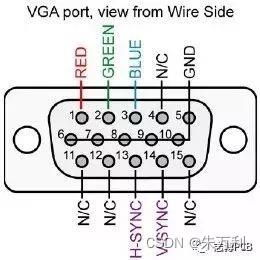

2、VGA接口管脚定义

管脚定义:

3、VGA电缆究竟是如何工作的?

这是一个DE-15 15针连接器(有点像用于RS-232的DB-9连接器,VGA多了一个行):

H-SYNC和V-SYNC代表水平和垂直同步。其余的都是不言自明的。H-SYNC和V-SYNC是数字(TTL)电平信号,低电平有效,彩色信号是模拟信号,0V(黑色)到0.7V(全彩色)。

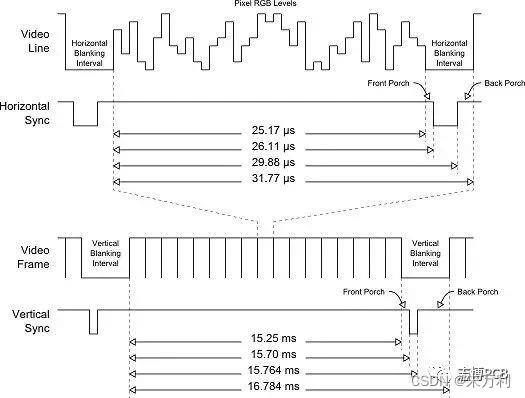

正如H-SYNC和V-SYNC的存在所暗示的那样,存在水平定时和垂直定时。此图显示了640x480 VGA的时序,这是原始VGA格式之一。

如上图所示的水平定时表示屏幕的一行(例如640x480显示器的640个可见像素)。在每行像素数据之间,存在水平消隐区域,其中没有显示视频(这最初主要用于电视中以允许CRT迹线从屏幕的右侧移回到左侧,为下一个准备好线)。

水平同步用于开始每条线的定时。它不像消隐区那么宽。就在水平脉冲之前,有一个称为前沿的延迟。紧接着水平脉冲是另一个叫做后门廊的延迟。

虽然显示了640个像素,但每行实际需要800个像素:水平同步为96,后沿为48,视频为640,前沿为16。

如图所示,每条线长31.77μs。以800像素潜水,每像素39.7 ns。这相当于25.1 MHz的时钟速率。

线条被聚集成帧,显示在图片的底部。与每条线的时序一样,每帧开始时都有一个垂直消隐间隔(这最初主要用于电视机,以允许CRT轨迹从屏幕底部向后移动到顶部,为下一帧做好准备)。在一些较旧的CRT电视机上,有可能将照片“滚动”下来,实际上将这个间隔看作屏幕上的黑条。与线路时序一样,时间有前廊和后廊区域。

尽管显示了480行,但每帧实际需要521行:垂直同步为2行,后沿为29行,可见行视频为480行,前沿为10行。

如图所示,每帧的长度为16.784 ms。这对应于59.5Hz的帧速率。

4、VGA参考设计原理图

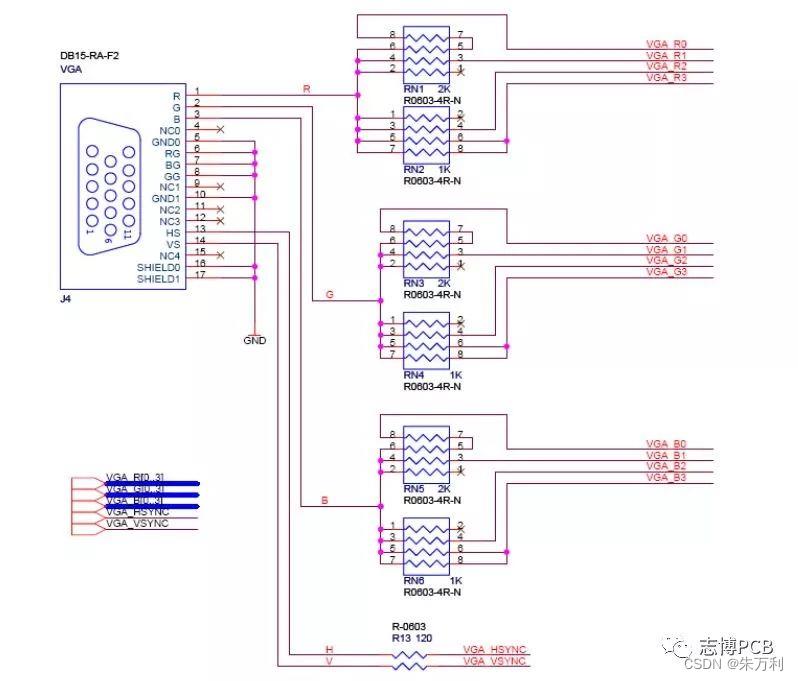

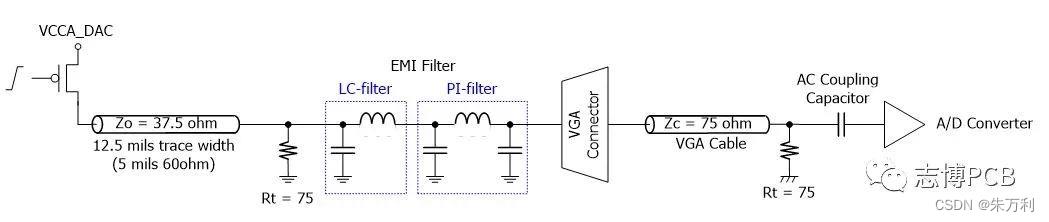

参考一:

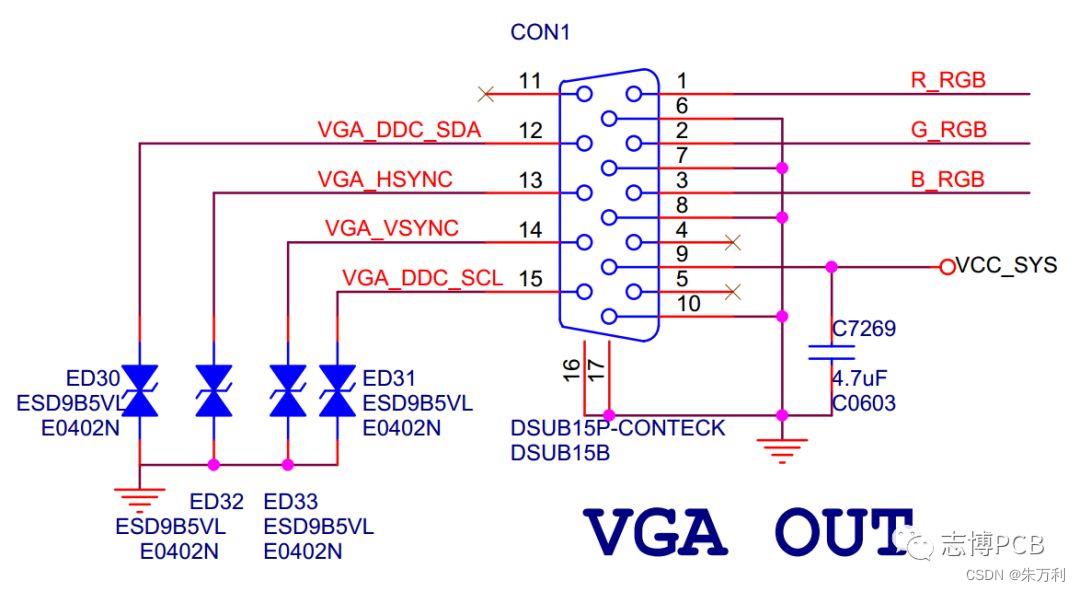

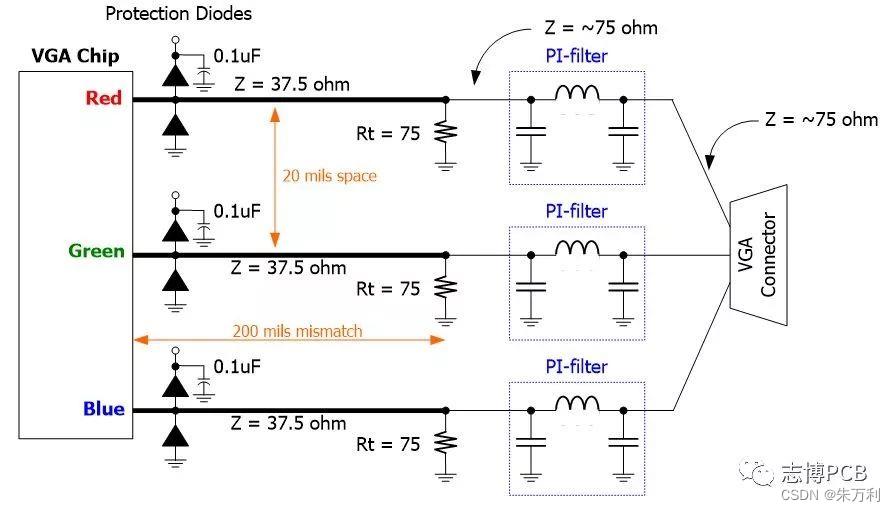

参考二:

5、PCB设计指南

1、R,G,B LAYOUT注意事项

rgb 输出缓冲区为"开源", 每个 dac输出时的等效 dc电阻为37.5。每个通道上也有一个用于降低高频噪声和 emi 的可比滤波器。上图是一个示例。为了最大限度地提高性能, 应匹配滤波器阻抗、电缆阻抗和负载阻抗。

rgb 跟踪应以37.5 的目标阻抗从输出缓冲器路由到75 1% 终止电阻, 然后继续以理想的跟踪目标阻抗75, 一直路由到至少有20英里间距的vga连接器。

rgb信号的长度应尽可能匹配,不应超过200英里的不匹配。用于rgb信号的端子电阻和可滤波器是相同的, 并且可滤波器靠近vga连接器。

rgb信号需要 dac 电源和接地之间的保护二极管。这些二极管的位置取决于dac功率平面。功率导轨与上拉二极管的电感应该是最小的, 以最大限度地提高性能。有关详细信息, 请参见图。

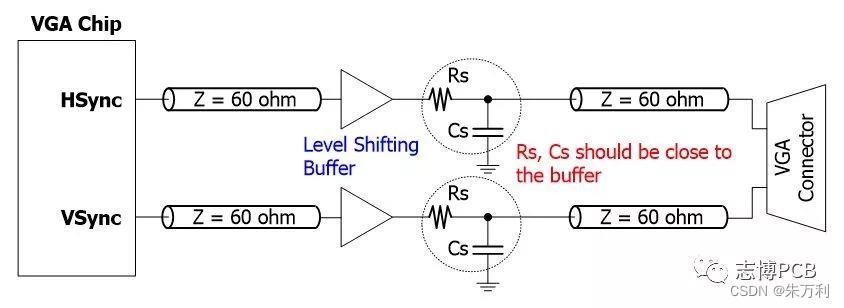

2、HSYNC,VSYNC Layout注意事项

hsync 和 vsync是 vga 芯片的输出或由液位移动设备缓冲的输出, 并且每个电平上都有串联源端接电阻, 如上图所示。r 和 c 应接近水平转移缓冲区。

3、其他注意事项

①:模块化布局操作,电阻电容离VGA接口最少保持1.5mm以上的间距,确保烙铁能方便焊接维修。

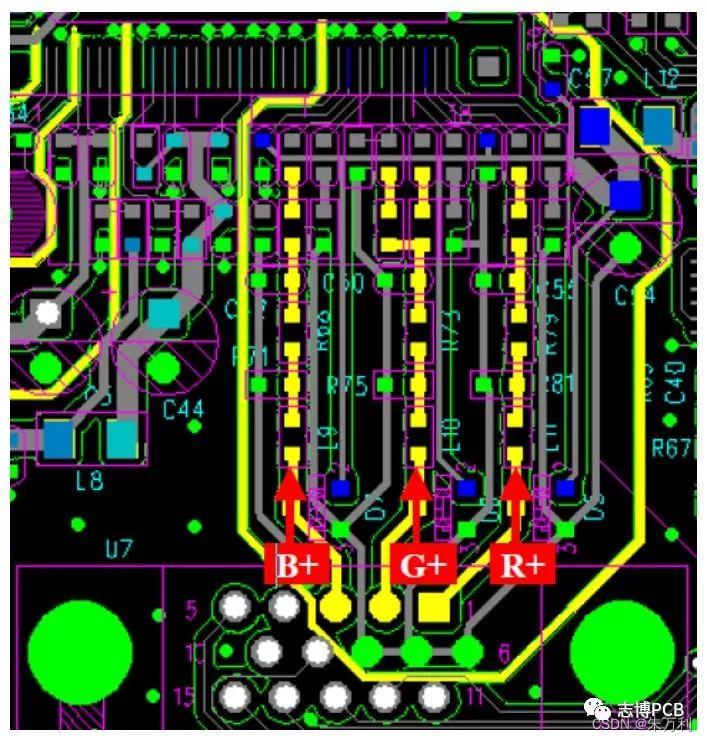

②:RGB信号,尽可能加粗,推荐线宽为6-8mil。

③:空间允许情况下对RGB信号做包地处理。

④:线和线之间尽可能满足3W原则。

⑤:VGA前端滤波器应遵循差分布局规则。

⑥:VGA前端滤波器靠近D-SUB连接器。

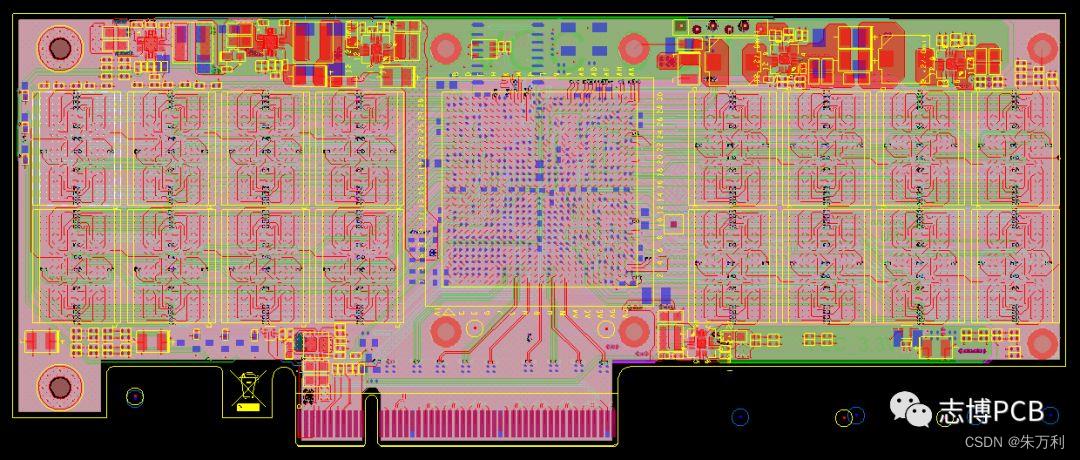

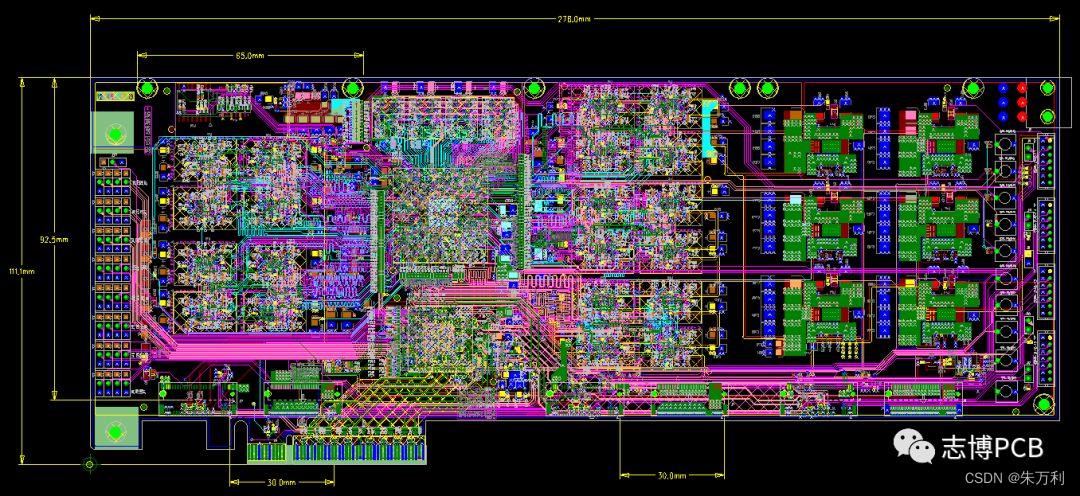

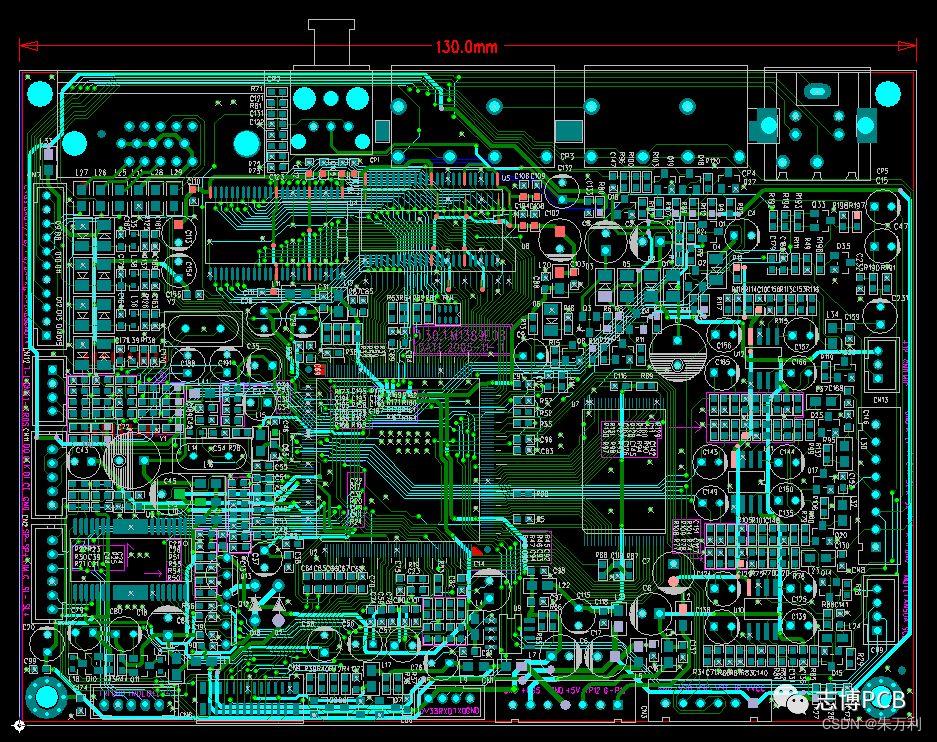

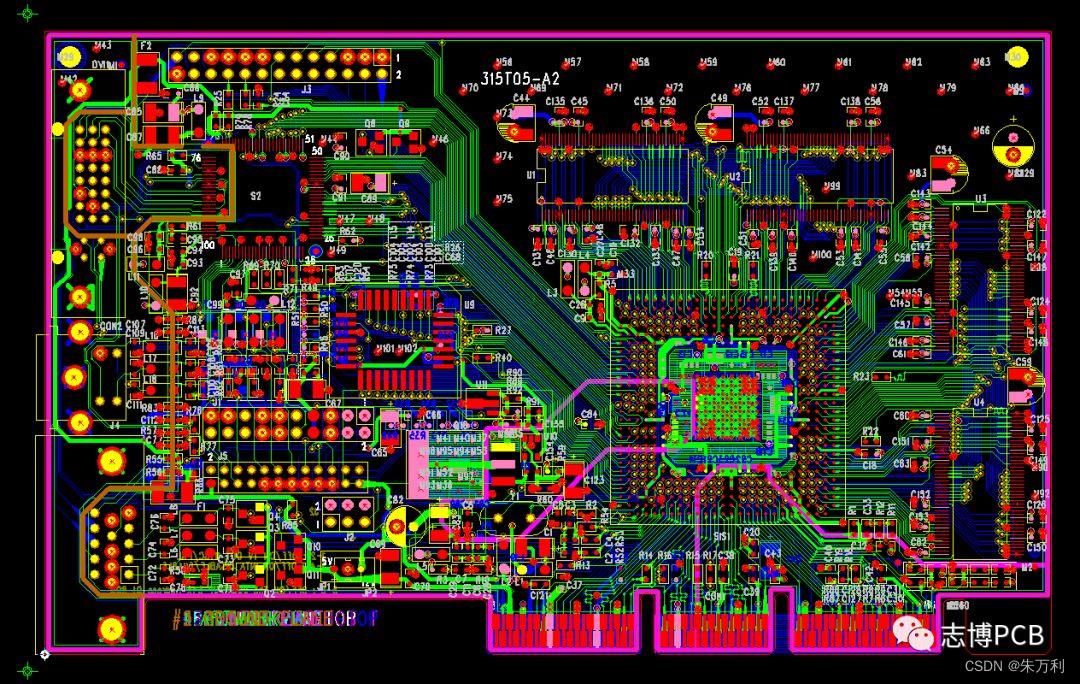

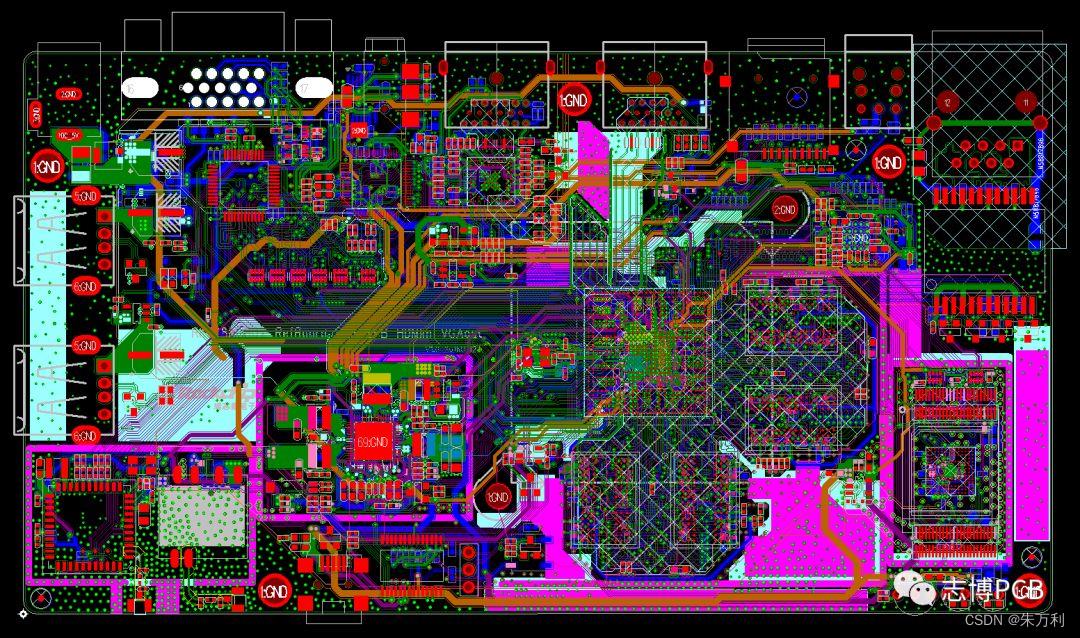

1、工控主板

2、DVD主板

3、SIS显卡主板

4、RK3288安卓广告机

以上是关于PCB模块化设计10——PCI-E高速PCB布局布线设计规范的主要内容,如果未能解决你的问题,请参考以下文章