计算机的存储器

Posted 计算机小白的爬坑之路

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机的存储器相关的知识,希望对你有一定的参考价值。

计算机的存储器

一、概述

1、存储器的分类

(1) 按存储介质分类

- 半导体存储器----TTL、MOS-----易失

- 磁表面存储器----磁头、载磁体-----不易失

- 磁芯存储器----硬磁材料、环状元件-----不易失

- 光盘存储器----激光、磁光材料-----不易失

(2) 按存取方式分类

- 存取时间与物理地址无关(随机访问):随机存储器(程序执行过程中可读可写);只读存储器(程序执行过程中只读)

- 存取时间与物理地址有关(串行访问):顺序存取存储器(磁带);直接存取存储器(磁盘)

(3) 按在计算机中的作用分类

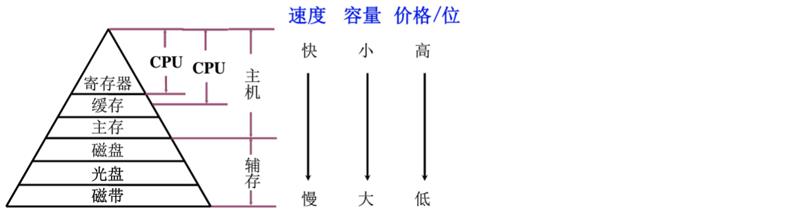

2、存储器的层次结构

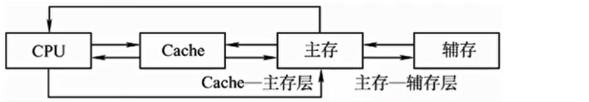

缓存——主存层次和主存——辅存层次

- 缓存与主存之间主要解决速度问题(cpu和主存速度的不匹配),因此通过硬件方法实现(主存速度的更新换代远跟不上CPU的发展,速度差异存在“剪刀差”)。

- 主存与辅存之间主要解决容量问题,因此使用软硬件相结合的方法。

- 缓存与主存使用的是主存储器的地址,也就是实地址(也叫物理地址);主存与辅存构成虚拟存储器,使用的是虚地址(也叫逻辑地址)。

二、主存储器

1、概述

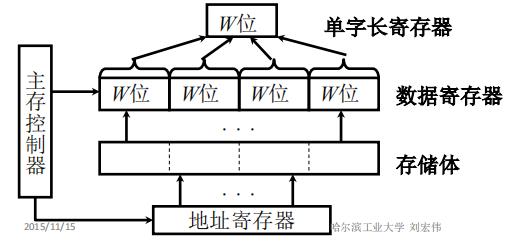

(1) 主存的基本组成

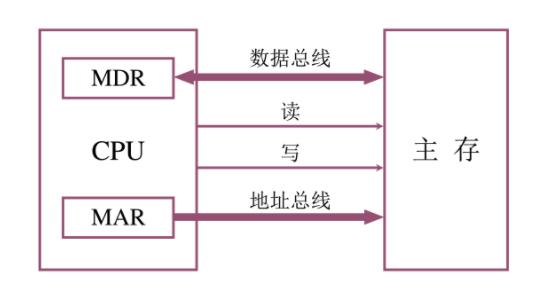

(2)主存和CPU的联系

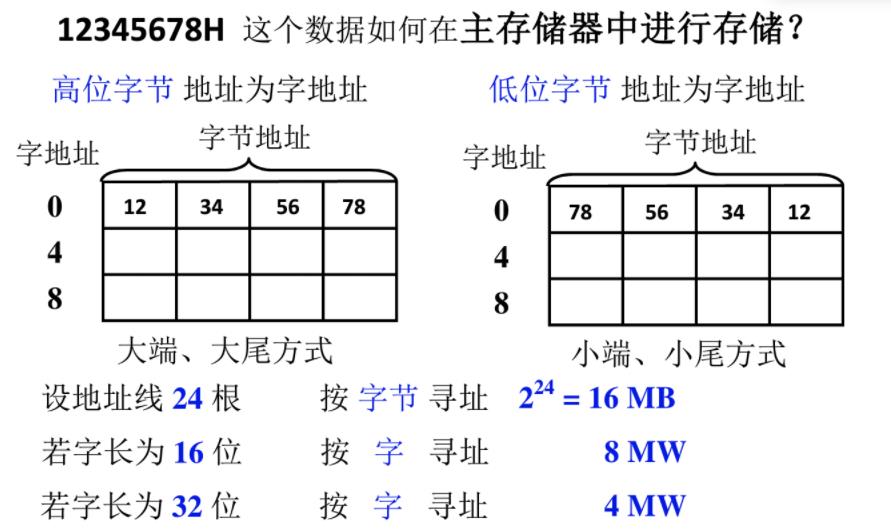

(3) 主存中存储单元地址的分配

2、半导体存储芯片

RAM 和 ROM 都属于半导体存储器,ROM 在系统停止供电的时候仍然可以保持数据,而 RAM 通常都是在掉电之后就丢失数据,所以 RAM 是易失性半导体存储器,ROM 是非易失性半导体存储器。

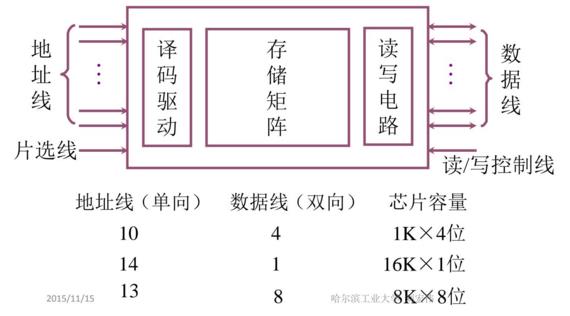

(1) 半导体存储芯片的基本结构

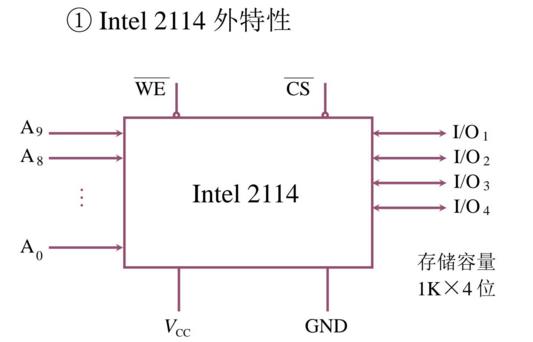

- 地址线(单向):由CPU或I/O设备的控制器指向存储器

- 数据线(双向)

- 芯片容量:如果地址线是10位,数据线是4位,则芯片容量=2的10次方×4

- 读/写控制线:

WE(低电平写、高电平读)

OE(允许读)WE(允许写) - 片选线用来选择存储芯片,由于半导体存储器是由许多芯片组成的,为此需用片选信号来确定哪个芯片被选中。

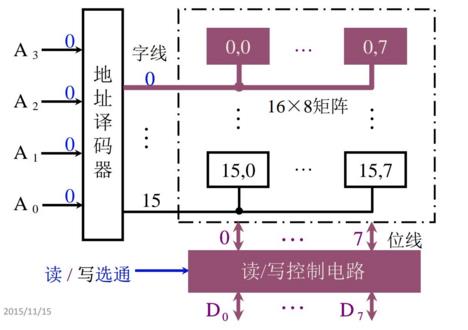

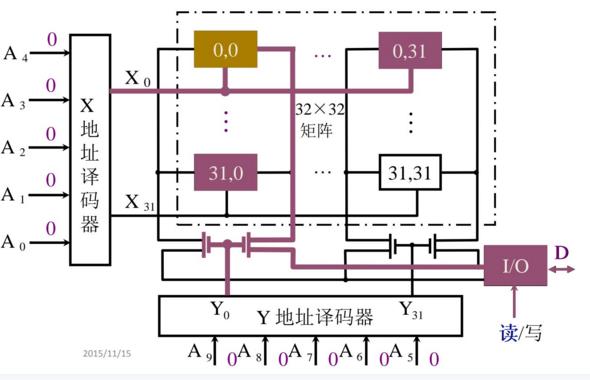

(2) 半导体存储芯片的译码驱动方式

译码驱动:如何找到给定存储单元,把地址总线送来的地址信号翻译成对应存储单元的选择信号,该信号在读/写电路的配合下完成对被选中单元的读/写操作。

-

线选法

-

重合法

3、随机存取存储器(RAM)

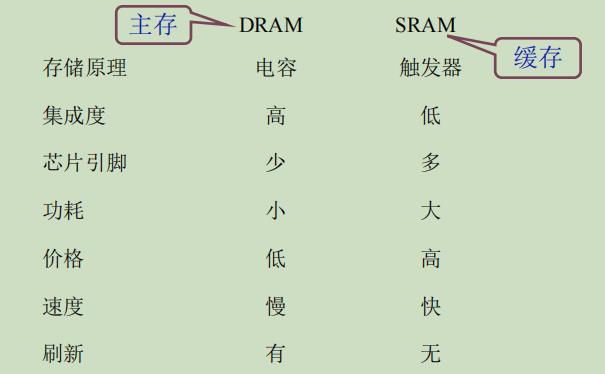

随机存取存储器按其存储信息的原理不同,可分为静态 RAM 和动态 RAM。静态 RAM 采用触发器原理来存储信息,动态 RAM 采用电容存储电荷原理来存储信息,都属于易失性半导体存储器。

(1) 静态RAM(SRAM)

静态 RAM 是用触发器工作原理存储信息,因此即使信息读出后,它仍然保持其原状态,不需要再生。

静态RAM基本电路

T1~T4:构成一个双稳态触发器,存放0,1

T5~T6:对存储元件读或写

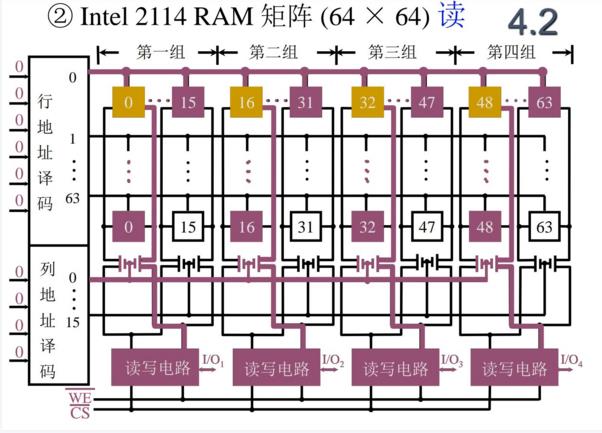

静态RAM芯片举例

(2) 动态RAM(DRAM)

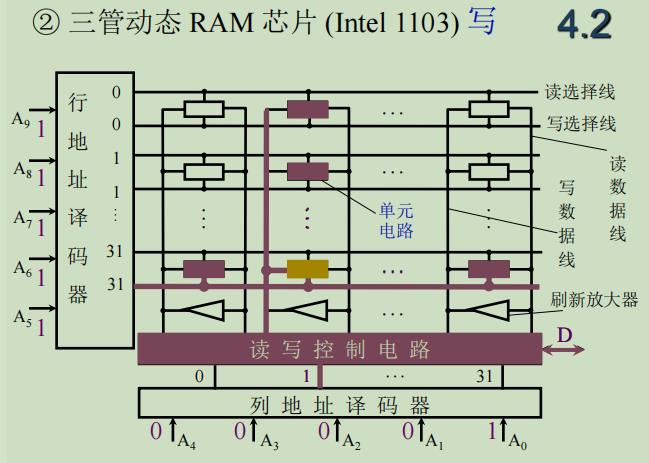

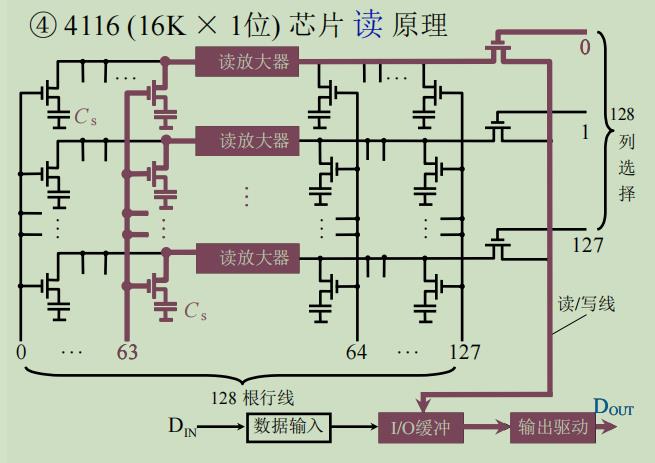

常见的动态 RAM 基本单元电路有三管式和单管式(MOS 管)两种,分别如下面左右两图所示,它们的共同特点都是靠电容存储电荷的原理来寄存信息。若电容上有足够多的电荷表示存“1”,电容上无电荷表示存“0”。

动态RAM基本单元电路(左:三管式;右:单管式)

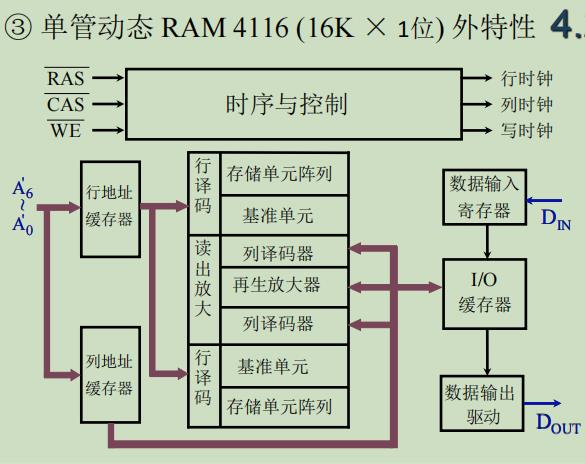

动态 RAM 芯片举例

动态RAM刷新

(3) 动态 RAM 和静态 RAM 的比较

4、只读存储器

(1) 掩模 ROM ( MROM )

只能读、不能擦除

行列选择线交叉处有 MOS 管为“1”

行列选择线交叉处无 MOS 管为“0”

(2) PROM (一次性编程)

如果保存“0”,用大的电流将熔丝烧断;破坏性编程

如果保存“1”,熔丝不烧断;

(3) EPROM (多次性编程 )

(4) EEPROM (多次性编程 )

电可擦写

局部擦写

全部擦写

(5) Flash Memory (闪速型存储器)

比 EEPROM快,具备 RAM 功能

5、存储器与CPU的连接

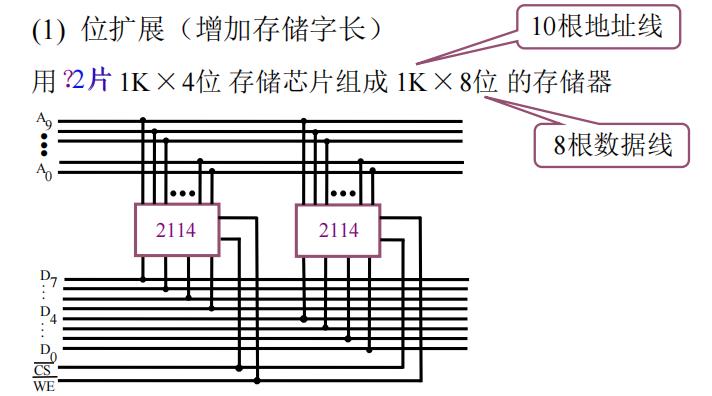

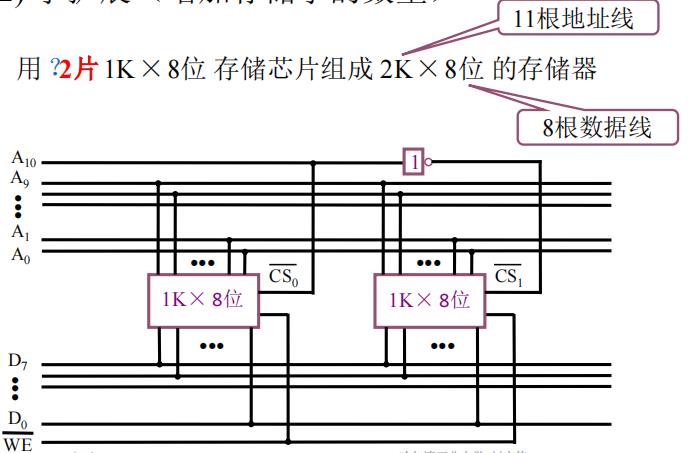

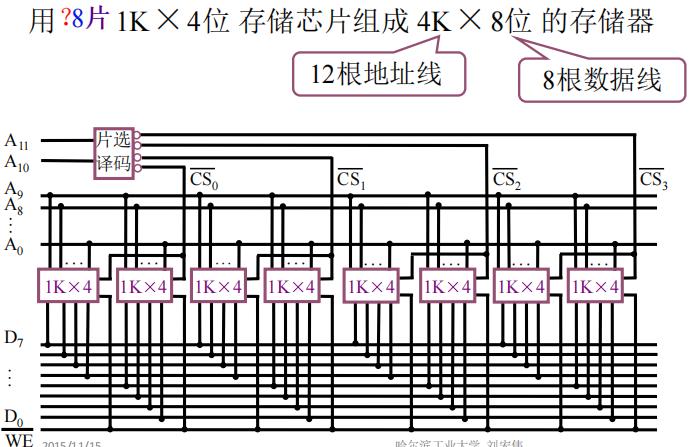

(1) 存储器容量的扩展

-

位扩展

-

字扩展

A10为两个芯片的片选信号,如果A10为0,选择第一个芯片;如果A10为1,选择第二个芯片。

-

字、位扩展

8个芯片分成4组,每组为 1K×8 位。

片选译码器:如果是00,选择第一组芯片;01选择第二组芯片;10选择第三组芯片;11选择第四组芯片。

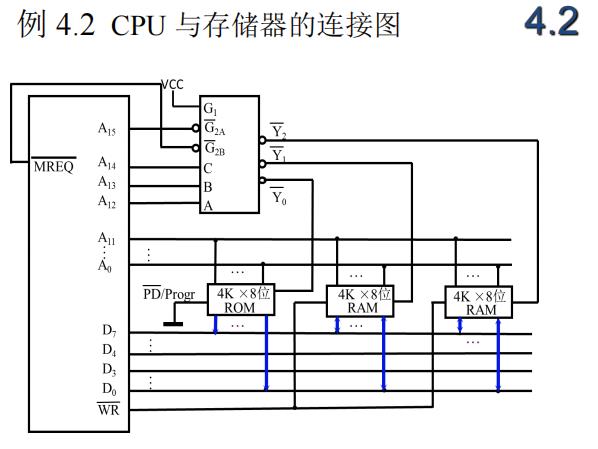

(2) 存储器与CPU的连接

- 地址线的连接

- 数据线的连接

- 读/写命令线的连接

- 片选线的连接

- 合理选择存储芯片

- 其他 时序、负载

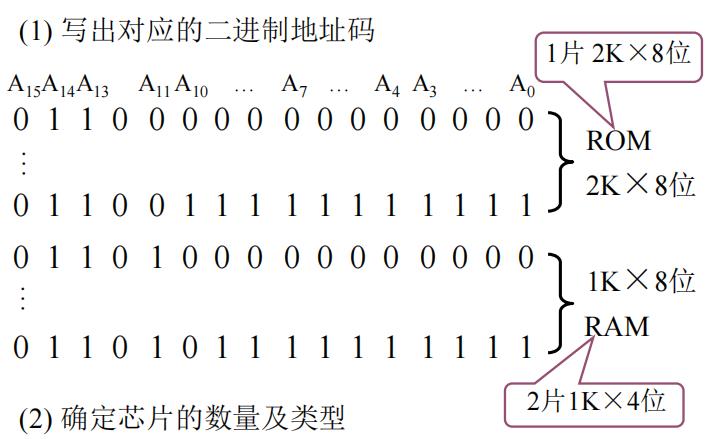

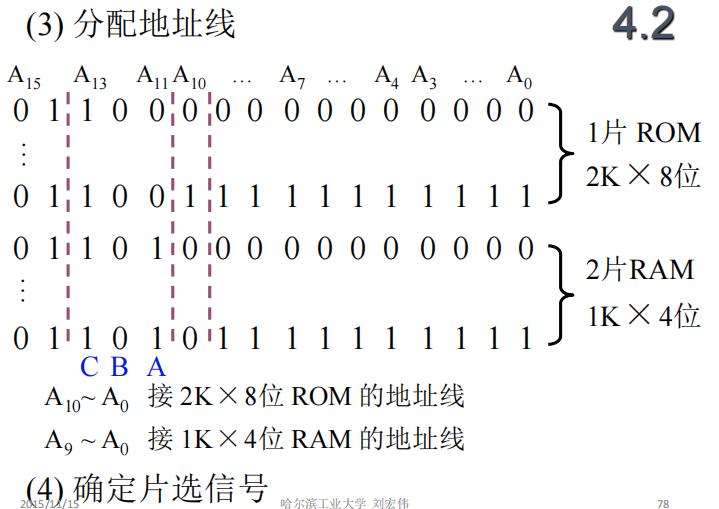

示例一

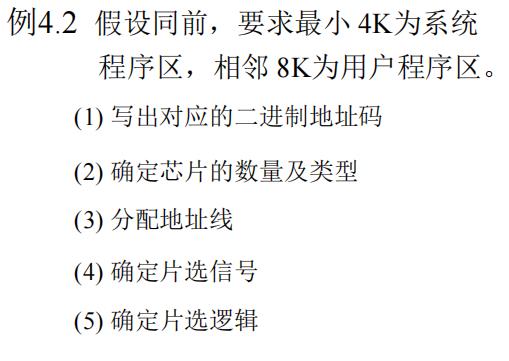

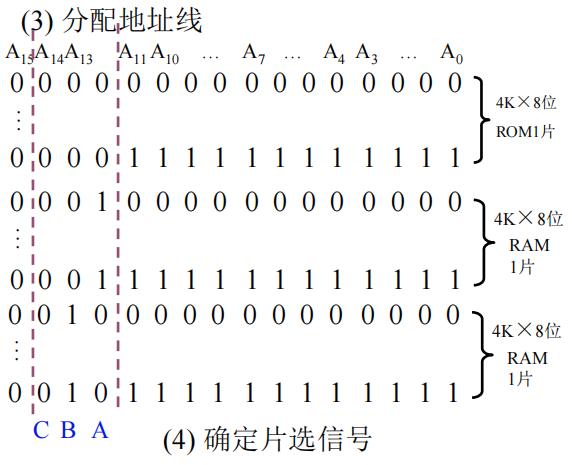

示例二

6、存储器的校验

为什么要有校验码?

因为在数据存取和传送的过程中,由于元器件或者噪音的干扰等原因会出现错误,这个时候我们就需要采取相应的措施,发现并纠正错误,对于错误的检测和校正,大多采取“冗余校验”的思想,即除原数据外,额外增加若干位编码,这些新增的代码称为校验位。

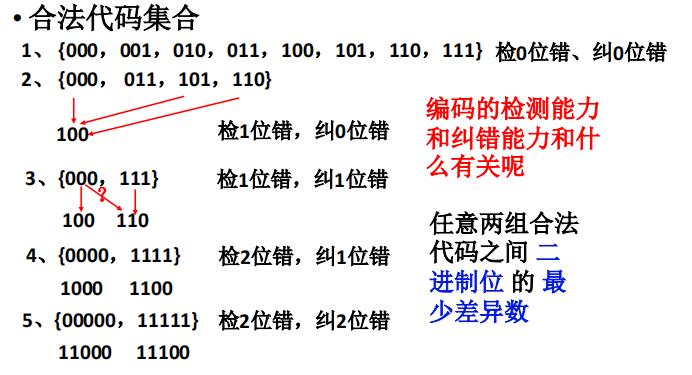

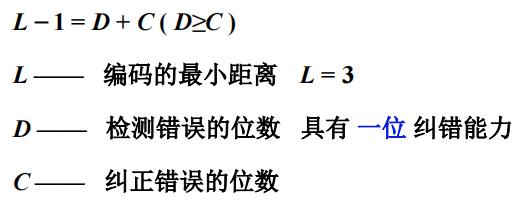

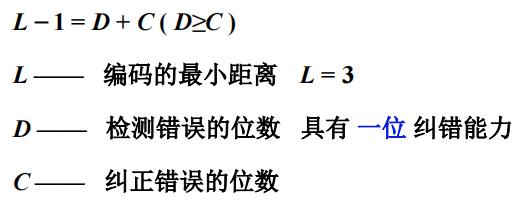

(1) 编码的最小距离

任意两组合法代码之间二进制位数的最少差异

编码的纠错、检错能力与编码的最小距离有关。

汉明码是具有一位纠错能力的编码

(2) 奇偶校验码

奇偶校验码的实现方法是在每个被传送码的左边或右边加上1位奇偶校验位“0”或“1”,若采用奇校验位,只需把每个编码中1的个数凑成奇数;若采用偶校验位,只要把每个编码中1的个数凑成偶数。

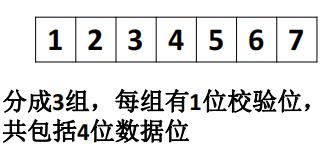

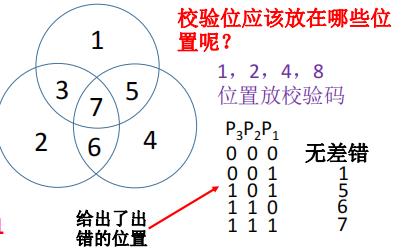

(3) 汉明码的组成

汉明码采用分组的奇偶检验、分组校验

划分方式:

汉明码的分组是一种非划分方式。

汉明编码分组规则:

组成汉明码的三要素

汉明码的组成需增添 ?位检测位

检测位的位置 ?

检测位的取值 ?

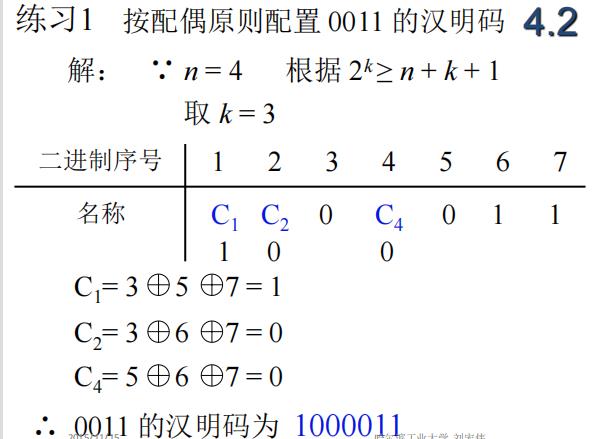

(4) 汉明编码示例

依据汉明编码分组规则所得:

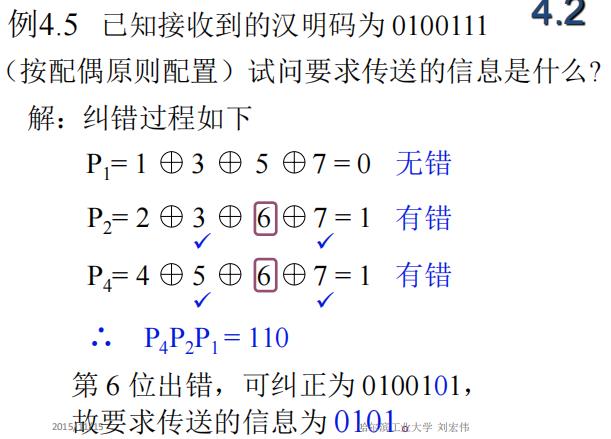

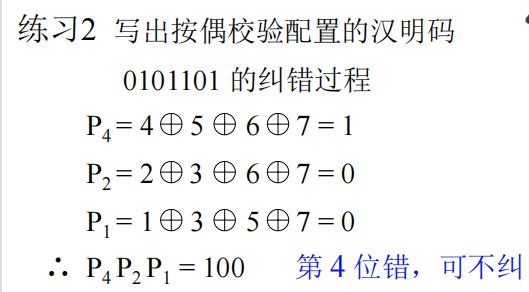

(5) 汉明码的纠错过程

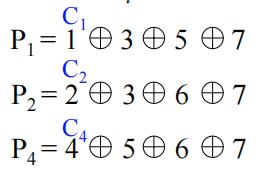

形成新的检测位 Pi,如增添 3 位(k = 3)。新的检测位为 P4 P2 P1。以 k = 3 为例,Pi的取值为

对于按“偶校验”配置的汉明码不出错时,P1=0,P2=0,P4=0。

(6) 汉明编码纠错示例

示例:

汉明编码可检错1位,纠错1位,根据公式得:码距为3

7、提高访存速度的措施

- 采用高速器件

- 采用层次结构 Cache -主存

- 调整主存结构

(1) 单体多字系统

增加存储器的带宽

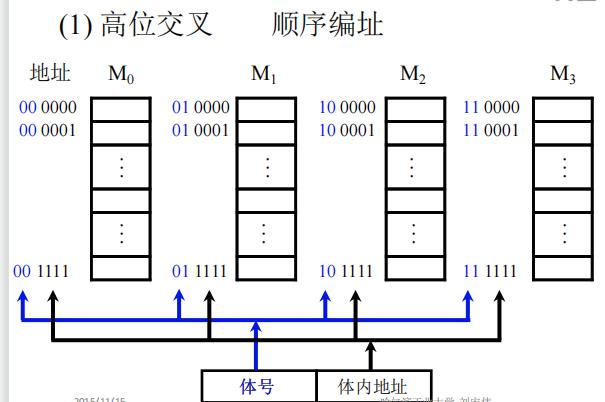

(2) 多体并行系统

高位前面2位对存储体进行编号

低位后面4位是对存储体内部地址编码

将M0存放满后再存放入M1

缺点:造成某一存储体(M0)繁忙,其他存储体空闲

依次存放至M0、M1、M2、M3的第一个存储单元,以此类推。

三、高速缓冲存储器

1、概述

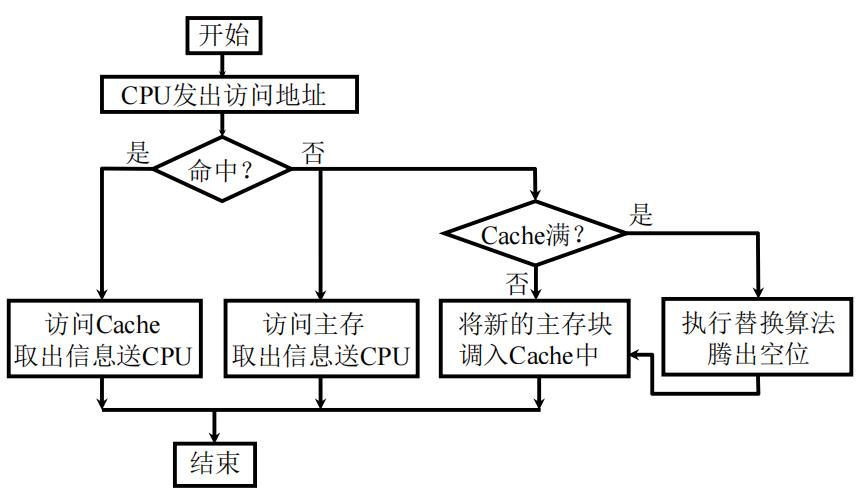

(1) Cache 的工作原理

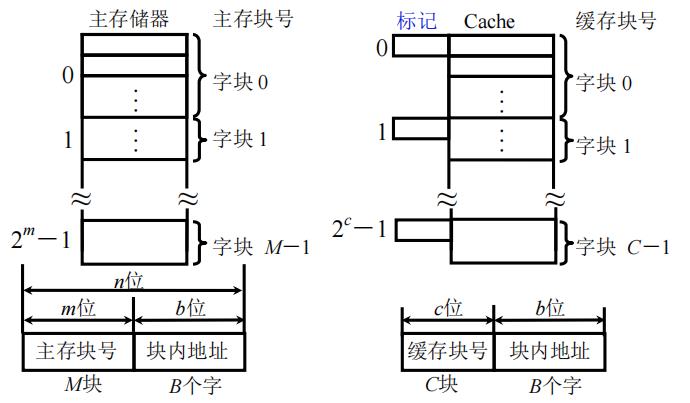

主存和缓存的编址

备注:

主存和缓存的块内地址完全一致。

缓存中的标记对应主存中的主存块号,像指针一样。

主存和缓存按块存储,块的大小相同,B 为块长。

(2) 命中与未命中

缓存共有 C 块,主存共有 M 块。其中,M >> C。

命中:主存块调入缓存,主存块与缓存块 建立 了对应关系。

未命中:主存块未调入缓存,主存块与缓存块未建立对应关系。

(3) Cache 的命中率

Cache 的命中率:CPU 欲访问的信息在 Cache 中的比率

命中率 与 Cache 的 容量 与 块长 有关

容量越大,命中率越大。容量越小,命中率越小。

块长越大,命中率越大。块长越小,命中率越小。

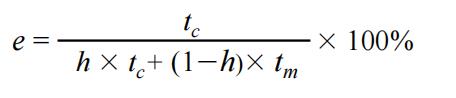

(4) Cache –主存系统的效率

访问效率 e 与 命中率 有关

设 Cache 命中率 为 h,访问 Cache 的时间为 tc , 访问 主存 的时间为 tm。并行访问:同时访问主存和缓存。

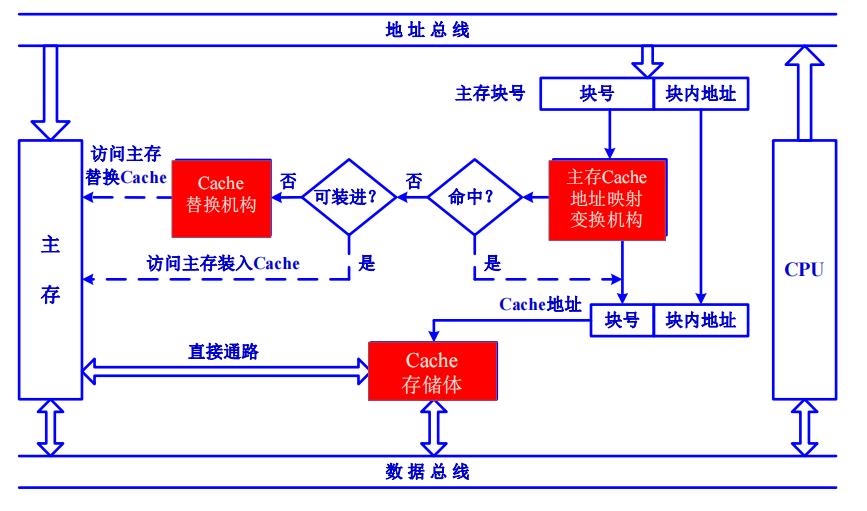

(5) Cache 的基本结构

(6) Cache 的读写操作

读操作:

写操作:Cache 和主存的一致性

• 写直达法(Write – through):写操作时数据既写入Cache又写入主。写操作时间就是访问主存的时间,Cache块退出时,不需要对主存执行写操作,更新策略比较容易实现。

• 写回法(Write – back):写操作时只把数据写入 Cache 而不写入主存。当 Cache 数据被替换出去时才写回主存,写操作时间就是访问 Cache 的时间,Cache块退出时,被替换的块需写回主存,增加了Cache 的复杂性。

2、Cache-主存的地址映射

(1) 直接映射

主存储体划分成若干与Cache存储体相等的区,每个区的大小与Cache存储体的大小相同。在进行映射时,主存储体中任何一个区的第0号只能放入Cache存储体字块0中…以此类推。

每个缓存块 i 可以和 若干 个 主存块 对应

每个主存块 j 只能和 一 个 缓存块 对应

直接映射:硬件简单,成本低,地址变换速度快,而且不涉及替换算法问题。但是这种方式不够灵活,Cache的存储空间得不到充分利用,每个主存块只有一个固定位置可存放,容易产生冲突,使Cache效率下降,因此只适合大容量Cache采用。

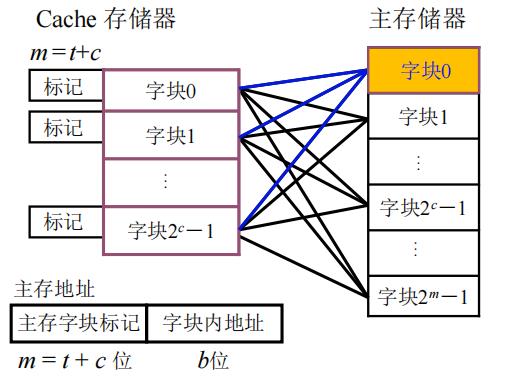

(2) 全相联映射

主存 中的 任一块 可以映射到 缓存 中的 任一块。当寻找一个地址是否已经被cache时,需要遍历每一个cache line来寻找,这个代价很高。

全相联映射方式:比较灵活,主存的各块可以映射到Cache的任一块中,Cache的利用率高,块冲突概率低,只要淘汰Cache中的某一块,即可调入主存的任一块。

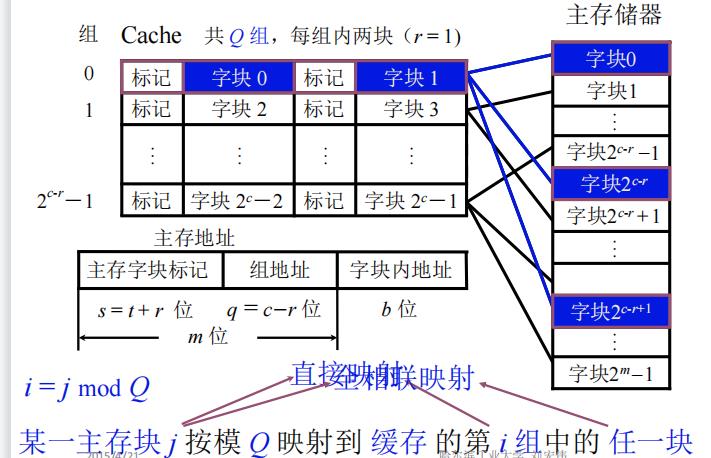

(3) 组相联映射

主存和Cache都分组,主存中一个组内的块数与Cache中的分组数相同,组间采用直接映射,组内采用全相联映射。即:将Cache分成2u组,每组包含2v块,主存块存放到哪个组是固定的,至于存到该组哪一块则是灵活的。

如果组相联方式Cache中所有的块都分成一组,组相联的映射方式变为全相联;

如果组相联方式中每一组只有唯一的一块,组相联就变成直接相连。

靠近CPU的Cache层次,采用直接相连或者路数比较少的组相联;中间的层次采用组相联;距离CPU最远的采用全相联(Cache的利用率高)。

3、替换算法

- 先进先出 ( FIFO )算法

- 近期最少使用( LRU)算法

四、辅助存储器

1、概述

特点:不直接与 CPU 交换信息。

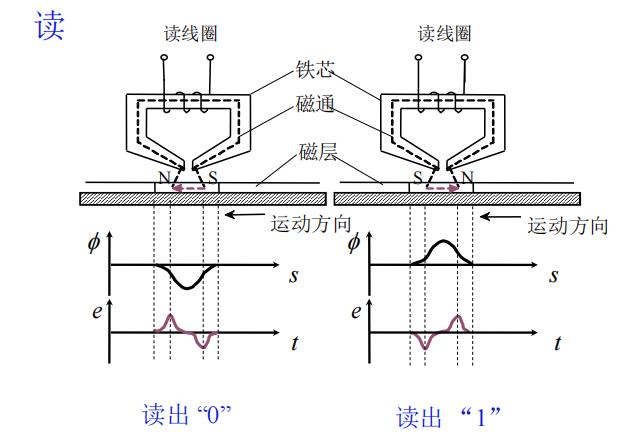

2、磁记录原理

3、硬磁盘储存器

(1) 硬磁盘存储器的类型

- 固定磁头和移动磁头

- 可换盘和固定盘

(2) 硬磁盘存储器结构

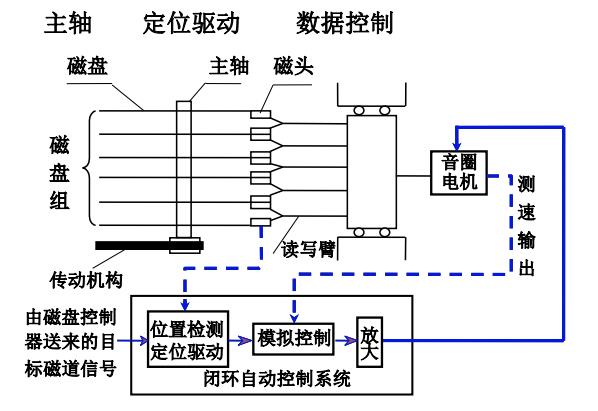

磁盘驱动器

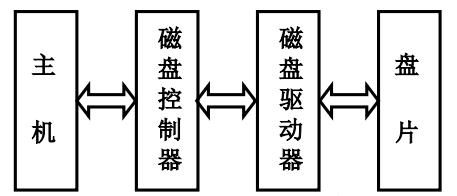

磁盘控制器

接收主机发来的命令,转换成磁盘驱动器的控制命令。

实现主机和驱动器之间的数据格式转换。并控制磁盘驱动器读写。

4、软磁盘存储器

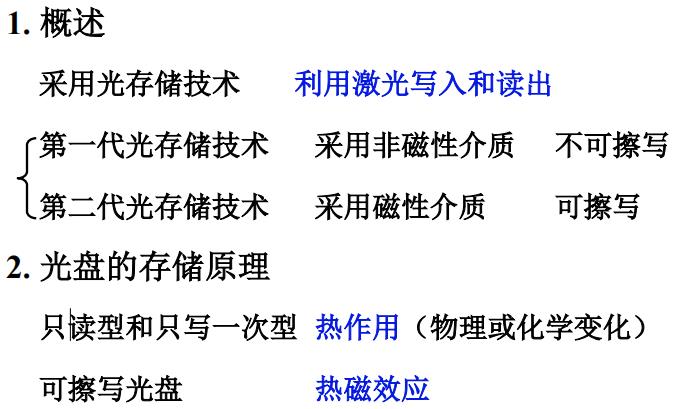

5、 光盘存储器

以上是关于计算机的存储器的主要内容,如果未能解决你的问题,请参考以下文章