参考技术A

Verilog中,数据类型主要分为两类: 物理数据类型 (主要包括连线型和寄存器型)和 抽象数据类型 (主要包括:整型、时间型、实型和参数型)

物理数据类型与实际硬件电路的硬件关系比较明显,抽象程度比较低

抽象数据类型是进行辅助设计和验证的数据类型

Verilog中主要的物理数据类型是:连线型、寄存器型、存储器型

使用四种逻辑电平(0,1,x,z)和八种信号强度(strength)对实际的电路进行建模

四种逻辑电平是对信号的抽象

信号强度表示数字电路中不同强度的驱动源,用来解决不同驱动强度下的赋值冲突,八种强度如下, 自上往下,强度递减

连线表示逻辑单元的物理连接,可以对应电路中的物理信号连线,这种变量不能保持电荷(trireg除外)

连线型变量必须要有驱动源,一种是连接到一个门或者模块的输出端,另一种是用assign对它进行赋值,若没有驱动源,将保持高阻态z

连线型有如下几种:

wire(连线)和tri(三态线)是最常见的,语法和语义是一致的。

不同之处如下:

wand和triand便是 与逻辑 ,因此当0和1同时出现时,结果是 0&1 的结果

tri的特征是,若无驱动源,其值为紧跟的数字

supply0表示GND,supply1表示VCC

trireg线网型可以存储数值,类似于寄存器数据类型,用于电容节点的建模。

当三态寄存器(trireg)的所有驱动源都处于高阻态 z 时,trireg保持作用在线网的最后一个逻辑值。

trireg的缺省初始值为x

存储电荷强度有如下几个关键字控制:

small、medium、large,默认电荷强度为medium

对于trireg型数据,仿真时其电荷衰减时间应制定为延迟时间

reg型变量对应的硬件电路元件具有状态保持作用,能够存储数据

reg型变量常用于行为级描述,由过程赋值语句对其进行赋值

reg和wire的区别:

reg型变量一般是无符号的,若将负数赋值给reg型变量,会自动转成其补码形式

语法为 <net_declaration><drive_strength><range><delay><list_of_variables>

drive_strength、range、delay是可选项目,list_of_variables为必选项

语法为: reg <range><list_of_variables>

存储器型本质上是寄存器型变量的阵列,所以用reg型变量建立寄存器组实现存储器功能。

存储器变量声明格式: reg<range1><name_of_list><range2>

其中,range1和range2是可选项,缺省是都为1

说明:

例如: reg [7:0] mem [255:0] 表示由256个位宽为8bit的寄存器组成的存储器

抽象型数据类型有:整型(integer)、时间型(time)、实型(real)和参数型(parameter)

整型数据常用于对循环控制变量的说明,在算术运算中被视为 二进制补码 形式的有符号数

整型数据默认为32bit有符号数

时间型与整型数据类似,不过时间型是64bit无符号数

时间型数据主要用于对模拟时间的存储与计算处理,常与系统函数 $time 一起使用

Verilog支持实型常量与变量,实型数据在机器码表示法中是浮点型数据,可用于对延迟时间的计算

参数型数据属于常量,在仿真开始之前就被赋值,并在仿真过程中保持不变

参数定义方法可以提高程序可可读性和可维护性,常用来定义延迟时间和变量的位宽

Verilog HDL有两大类数据类型

1.线网类型

net type表示verilog结构化元件间的物理连线。值由驱动元件的值决定,如果没有驱动元件连接到线网,线网的缺省值为z。

2.寄存器类型

register type表示一个抽象的数据存储单元。只能在always和initial中赋值,并且它的值从一个赋值到另一个赋值被保存下来。寄存器类型的变量缺省值为x。

线网类型包含不同的线网子类型:wire,tri,wor,trior,wand,triand,trireg,tri1,tri0,supply0,supply1

线网类型语法说明:

net_kind [msb:lsb] net1,net2,....,netN

net_kind是上述线网类型的一种

msb和lsb是用于定义线网范围的常量表达式

例如: wire Rdy Start---->两个1位的连线

wand [2:0] Addr----->Addr是3位线与

当一个线网有多个驱动器时,即对一个线网有多个赋值时,不同的线网产生不同的行为。

例如:

wor Rde;

...

assign Rde = Blt & Wyl;

...

assign Rde = Kbl | Kip; Rde有两个驱动源,由于它是线或线网,Rde的有效值由使用驱动源的值的线或表决定。

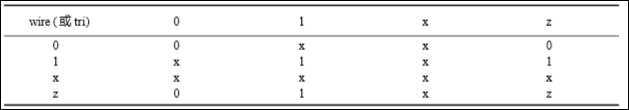

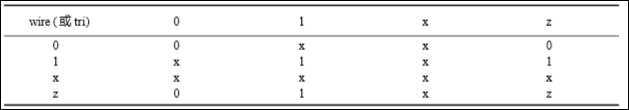

1.wire和tri线网:用于连接单元的连线是最常见的线网类型

连线与三态线网(tri)语法和语义一致,三态线可以用来描述多个驱动源驱动同一根线的线网类型。如果有多个驱动源,线网的有效值如下表:

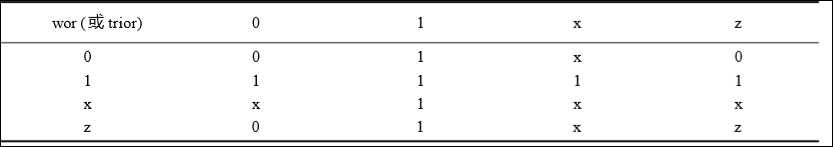

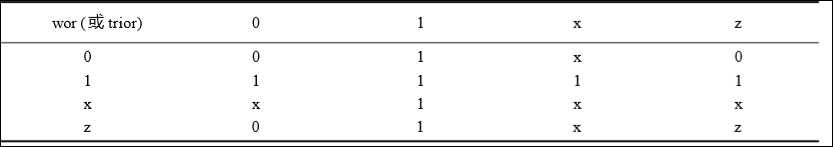

2.wor和trior线网:线或者如果某个驱动源为1,那么线网的值也是1.线或和三态线或(trior)在语法和功能上是一致的。

wor [MSB:LSB] Art;

trior [MAX-1:MIN-1] Rdx,Sdx,Bdx

如果多个驱动源驱动这类网,网的有效值由下表决定:

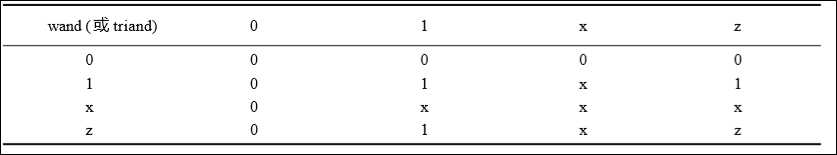

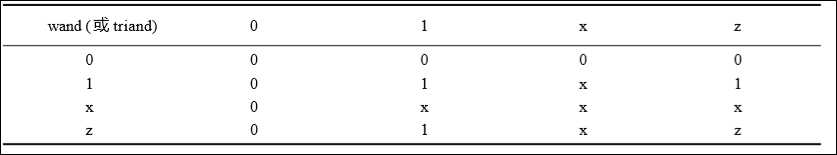

3.wand和triand线网

线与(wand)网如果某个驱动源为0,那么线网的值为0.线与和三态线与(triand)网在语法和功能上是一致的。

wand [-7:0] Dbus;

triand Reset,Clk

4.trireg线网

此线网存储数值,并且用于电容节点建模。当三态寄存器(trireg)的所有驱动源都处于高阻态,即值为z时,三态寄存器线网保存作用在线网上的最后一个值。三态寄存器线网的缺省初始值为x。

trireg [1:8] Dbus,Abus

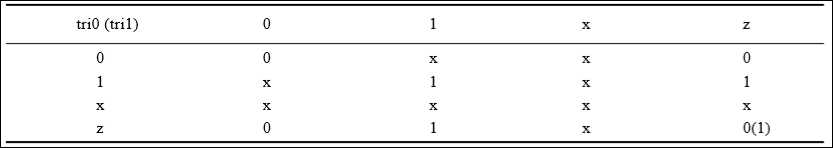

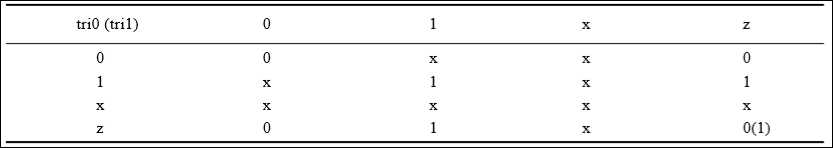

5.tri0和tri1线网

这类线网可用于线逻辑的建模,即线网有多于一个驱动源。tri0线网的特征是,若无驱动源驱动,它的值为0。tri1与其相反。

6.supply0和supply1线网

supply0用于对地建模,即低电平0

supply1用于对电源建模,即高电平1

7.未说明的线网

在Verilog HDL中,有可能不必生命某种线网类型,在这样的情况下,缺省线网类型为1位线网。

可以使用`define_nettype编译器指令改变隐式线网说明,例如:`default_nettype wand

向量和标量线网

在定义向量线网时可选用关键词scalared或vectored。如果一个线网定义时使用了关键词vectored,那么就不允许位选择和部分选择该线网。如果没有定义关键词,缺省值为标量。

寄存器类型:reg,integer,time,real,realtime

1.reg寄存器类型----->最常见的数据类型

形式如下:reg [msb:lsb] reg1,reg2,........,regN [msb:lsb]定义了范围,并且均为常数值表达式,缺省值位1位寄存器。

reg [3:0] Sat;-------->Sat为4位寄存器

寄存器可以取任意长度。寄存器中的值为无符号数,例如:

reg [1:4] Comb;

...

Comb = -2;-------->Comb的值为1110,1110是2的补码

Comb = 5 ;--------->Comb的值为0101

2.存储器

存储器是一个寄存器数组,例如:reg [0:3] MyMem [0:63]----------->MyMem为64个4位寄存器的数组

reg Bog [1:5]------------>Bog为5个1位寄存器的数组。MyMem和Bog都是存储器。数组的维数不能大于2.注意存储器属于寄存器数组类型,线网数据类型没有对应的寄存器类型。

parameter ADDR_SIZE = 16,WORD_SIZE = 8;

reg [1:WORD_SIZE] RamPar [ADDR_SIZE-1:0],DataReg;

RamPar是存储器,是16个8位寄存器数组,而DataReg是8位寄存器。

对寄存器赋值和对存储器赋值是不同的,存储器赋值不能在一个赋值语句中完成。

reg [1:5] Dig;

‘‘‘

Dig = 5‘b11011;

对存储器赋值:

reg [0:3] Xrom [1:4]

...

Xrom[1] = 4‘hA;

Xrom[2] = 4‘h8;

Xrom[3] = 4‘hF;

Xrom[4] = 4‘h2;

为存储器赋值的另一种方法是使用系统任务:

1.$readmemb(加载二进制值)

2.$readmemh(加载十六进制值)

系统任务从指定的文本文件中读取数据并加载到存储器。文本文件必须包含相应的二进制或十六进制数

reg [1:4] RomB [7:1];

$readmemb ("ram.patt",RomB); --------------------->Romb是存储器,文件ram.patt必须包含二进制值,文件也可以包含空白空间和注释。

系统任务$readmemb促使从索引7即为Romb最左边的字索引,开始读取值。

如果只加载存储器的一部分,值域可以在$readmemb方法中定义。

$readmemb("ram.patt",RomB,5,3);此时只有Romb[5]~Romb[3]从文件头开始被读取。

文件可以包含显式的地址形式。@hex_address value例如:@5 11011,这种情况下,值被读入存储器指定地址。

3.Integer寄存器类型

整数寄存器包含整数值。整数寄存器可以作为普通寄存器使用,典型应用为高层次行为建模。使用整数型形式说明如下:

integer integer1,integer2,...,integerN[msb:lsb];

例如:integer A,B,C------->表示三个整数型寄存器 integer Hist [3:6]----------->一组四个寄存器

一个整数型寄存器可存储有符号数,并且算术操作符提供2的补码运算结果。整数不能作为位向量访问。一种截取位值的方法是将整数赋值给一般的reg类型变量,然后从中选取相应的位

================

reg [31:0] Breg;

integer Bint;

Breg = Bint;//直接访问Bint[6]和Bint[20:10]是不允许的,但是Breg[6]和Breg[20:10]是允许的了。

================

4.time类型

time类型的寄存器用于存储和处理时间。例如:time Events [0:31]------->时间值数组

time CurrTime-------->currtime存储一个时间值

5.real和realtime类型

实数寄存器使用如下:

real real_reg 1, real_reg2, . . ., real_regN;

real和realtime类型和使用完全相同。

real说明的变量的缺省值为0.不允许对real声明值域、位界限或字节界限。