怎么用debug c语言

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了怎么用debug c语言相关的知识,希望对你有一定的参考价值。

怎么用debug c语言

简单来说,有两种方式,一种是源码debug,即分析源码来找出bug位置,一般使用printf()打印出程序执行每一步的信息,一种是可执行文件debug,需要使用调试器来进行。

1、源码debug

类似于下面的源码,主要通过程序执行时输出的信息,来定位bug出现的位置,然后再修改源码。

#include <stdio.h>

void f() ;

int main()

#ifdef _DEBUG

printf("start main function!\\n");

#endif

void f();

#ifdef _DEBUG

printf("leave main function !\\n");

#endif

return 0;

2、可执行文件调试,windows平台常用的就是vs/vc自带的调试,另外一个就是微软自家开发的调试器windbg。Linux平台以gdb为常用。

IDE自带的调试器以VC6.0为例,编写完代码后,按快截键盘F11,即可进入调试,此时右键,选择“go to disassembly"即可查看到程序的反汇编代码 。一般这种情况,主要是为了对C语言进行反汇编学习。

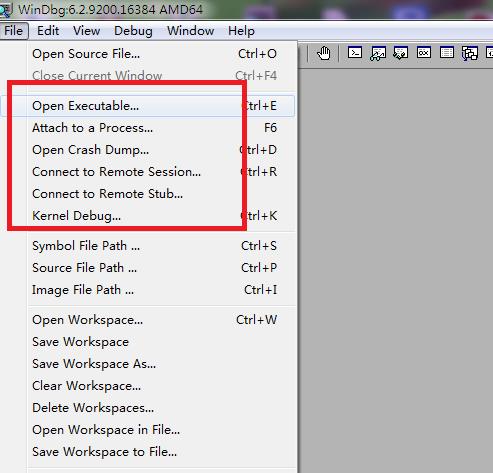

Windbg的功能非常多,可以进行源码调试、可以调试可执行文件、还可以进行内核调试,也可以调试dump文件,用的多了,自然熟悉,要调试可执行文件,只需要点击”File"在弹出的对话框中选择“Open Executeable",然后找到自己要调试的程序即可。

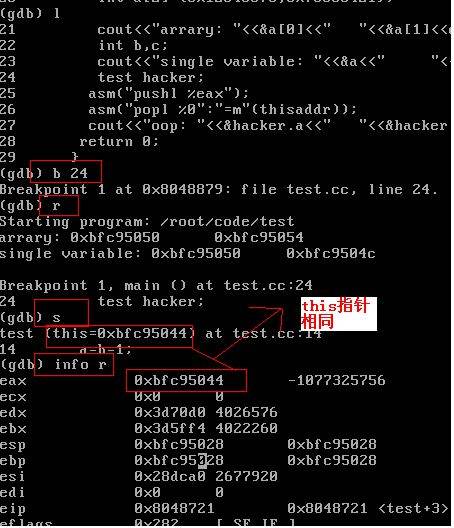

Linux常用的是Gdb调试器,值得注意的是,要使用gdb调试,在使用gcc或者g++编译C/c++文件时,需要添加-g参数才可以生成符号表。下图是用gdb分析C++中变量分布的一张截图,大体上看一下长什么样,用的多了自然熟悉,不需要可以去学习。

Vivado的debug core怎么用

使用vivado isim仿真的方法和过程如下:1) 测试平台建立;

a) 在工程管理区点击鼠标右键,弹出菜单选择New Source,弹出界面; b) 输入文件名,选择Verilog Test Fixture,打钩add to project,单击NEXT;

c) 选择要仿真的文件,点击NEXT;

d) 点击“FINISH”,就生成一个Verilog测试模块。

ISE能自动生成测试平台的完整构架,包括所需信号、端口声明以及模块调用的实现。所需要完成的工作就是initial….end模块中的“//Add stimulus here”后面添加测试向量生成代码。

这里给出示例测试代码,将其添加于//Add stimulus here处

#100;

SW = 7;

#100;

SW = 11;

#100;

SW = 13;

#100;

SW = 14;

2) 测试平台建立后,在工程管理区将状态设置为“Simulation”;选择要仿真的文件名,

过程管理区就会显示“Isim simlator”;

3) 下拉“Isim simlator”,选择“Simulate Behavioral Model”,单击鼠标右键,现在“Process Properties”可修改仿真远行时间等。

4) 修改后,直接双击“Isim simlator”中的“Simulate Behavioral Model”进行仿真。

检查仿真结果是否达到预期设计目标。

Vivado设计套件,是FPGA厂商赛灵思公司2012年发布的集成设计环境。包括高度集成的设计环境和新一代从系统到IC级的工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。集成的设计环境——Vivado设计套件包括高度集成的设计环境和新一代从系统到IC级的工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。 参考技术A HLS的输出sh不能作为IP直接被ISE使用,源代码可以。

以上是关于怎么用debug c语言的主要内容,如果未能解决你的问题,请参考以下文章