ARMv8基础篇400系列控制器IP

Posted 漫游嵌入式

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ARMv8基础篇400系列控制器IP相关的知识,希望对你有一定的参考价值。

🌟🌟🌟博主主页:MuggleZero 🌟🌟🌟

《ARMv8架构初学者笔记》专栏地址:《ARMv8架构初学者笔记》

前文:

这一节我们简单介绍一下ARMv8架构中的一些控制器。这里主要介绍400系列的IP。

GIC-400

GIC-400是一个高性能、区域优化的中断控制器,具有高级微控制器总线架构(AMBA)高级可扩展接口(AXI)接口。它在片上系统(SoC)配置中检测、管理和分配中断。你可以对GIC-400进行配置,以便为你的预期应用提供所需的最佳功能、性能和门数量。

通过GIC-400的下列软件可配置设置,提供的中断控制选项如下所示:

-

启用或禁用。

-

分配到两个组中的一个,组0或组1。

-

优先处理。

-

在多处理器实现中向不同的处理器发出信号。

-

可以是电平敏感的,也可以是边沿触发的。

GIC-400实现了以下的功能:

-

GIC安全扩展,支持。

-

将0组中断作为安全中断,将1组中断作为非安全中断。

-

可以选择使用FIQ中断请求,向连接的处理器发出安全中断信号。GIC-400总是使用IRQ中断请求发出第1组中断的信号。

-

GIC虚拟化扩展,为管理虚拟化中断提供硬件支持。 关于GIC安全扩展和GIC虚拟化扩展的更多信息,请参阅ARM通用中断控制器架构规范。

我们可以在最多有八个处理器的多处理器系统中使用GIC-400。GIC-400 支持并非每个处理器都实现了 ARM 安全扩展或 ARM 虚拟化扩展的系统。在这种情况下,每个处理器只使用它所知道的功能。有关信息,请参阅 ARM 通用中断控制器V3/V4架构规范。

GIC-400实现了以下的中断类型:

-

16个软件产生的中断(SGI)。

-

每个处理器有6个外部私有外设中断(PPI)。

-

每个处理器有1个内部PPI。

-

可配置的共享外设中断(SPI)的数量。

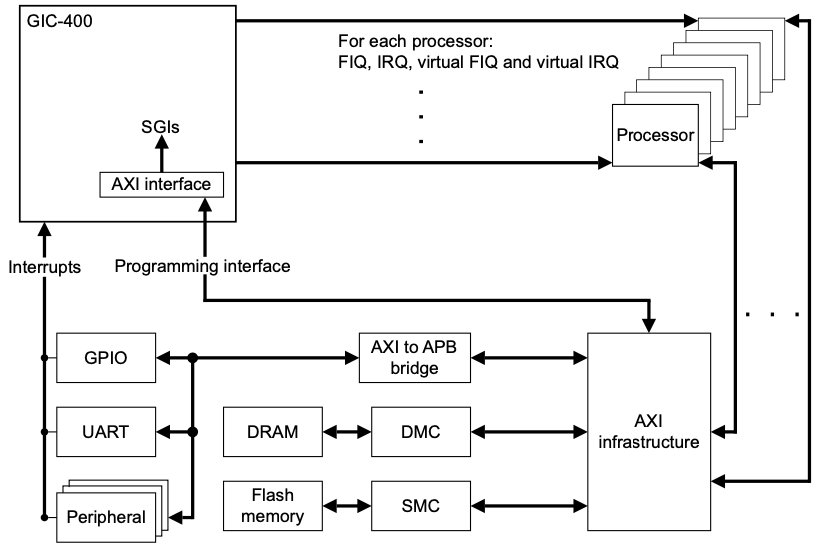

GIC-400的BD如下图所示,GIC-400从中断输入信号中检测PPI和SPI。每个处理器的每个PPI中断ID都有一个信号。每个SPI中断ID只有一个输入信号,与SoC中处理器的数量无关。SGI没有输入信号,在GIC-400中使用AXI编程接口生成。

GIC-400通过使用中断输出信号来通知每个处理器中断或虚拟中断的存在。还有中断输出信号,为系统电源控制器提供唤醒功能,见第2-12页的电源管理。

虚拟中断是由在运行虚拟机的每个处理器上执行的特殊软件创建和管理的。这种管理程序不是GIC-400架构的一部分,但对于使用中断控制器虚拟化中断是必要的。有关管理程序的概述,请参见ARM通用中断控制器架构规范。

GIC-400实现了ARM通用中断控制器架构规范所描述的分区。它由一个分配器和一个CPU接口以及系统中每个处理器的虚拟CPU接口组成。

GIC-400实现了可选的GIC虚拟化扩展,使其能够管理虚拟中断,前提是系统中至少有一个处理器实施了管理程序。尽管管理程序软件将物理中断转化为虚拟中断并处理复杂的情况,但GIC-400经常在硬件中处理来自虚拟机的中断访问的确认和结束。在处理器上运行的管理程序和GIC-400中的虚拟接口控制块构成了虚拟分配器。

CCI-400

CCI(Cache Coherent Interconnect)是ARM中的cache一致性控制器。

CCI-400将互连和一致性功能结合到一个模块中。它支持多达两个ACE 主节点的连接,例如:

-

Cortex®-A7 processor

-

Cortex-A15 processor

-

Cortex-A17 processor

-

Cortex-A53 processor

-

Cortex-A57 processor

CCI-400还支持多达三个ACE-Lite主站,例如,ARM MaliTM-T600系列图形处理器单元(GPU)。

所有这些接口都有可选的DVM消息支持,以管理分布式内存管理单元(MMU),例如CoreLink MMU-400。这些单元可以通过CCI-400与最多三个ACE-Lite从机进行通信。

硬件管理的一致性可以通过共享片上数据来提高系统性能和降低系统功耗。

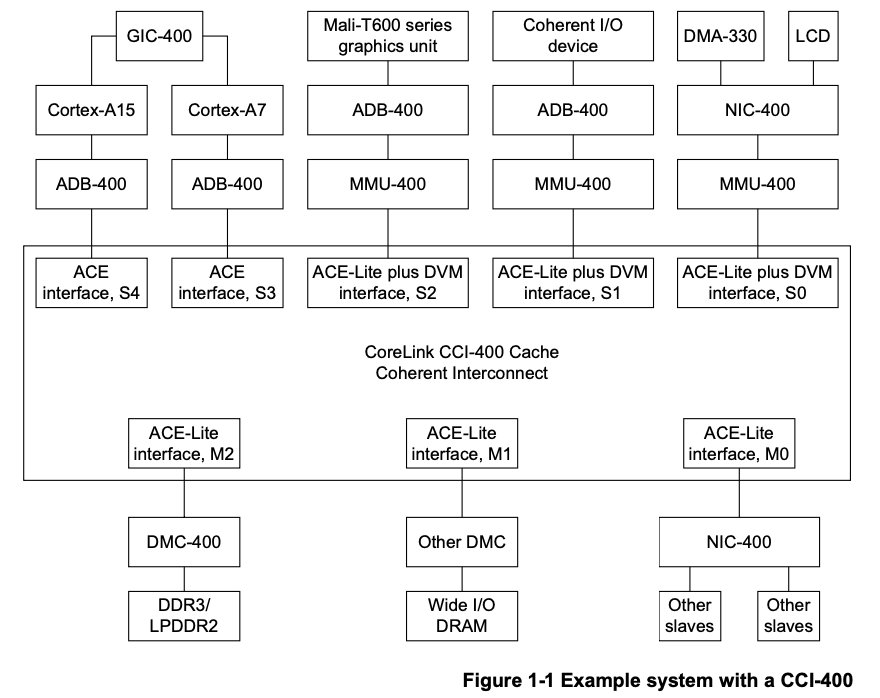

CCI-400cache一致性控制器实现了ACE协议,demo系统框图如下所示:

CCI-400cache一致性控制器是一个基础设施组件,支持以下内容:

-

在最多两个ACE主站和三个ACE-Lite主站之间的数据一致性,有三个独立的序列化点(PoS)和全屏障支持。

-

主站和最多三个从站之间的高带宽、跨栏互连功能。

-

主站之间的DVM消息传输。

-

QoS虚拟网络(QVN)。

-

服务质量(QoS)调节,用于塑造流量曲线。

-

性能监测单元(PMU),统计与性能有关的事件。

-

一个程序员视图(PV),控制一致性和互连功能。

NIC-400

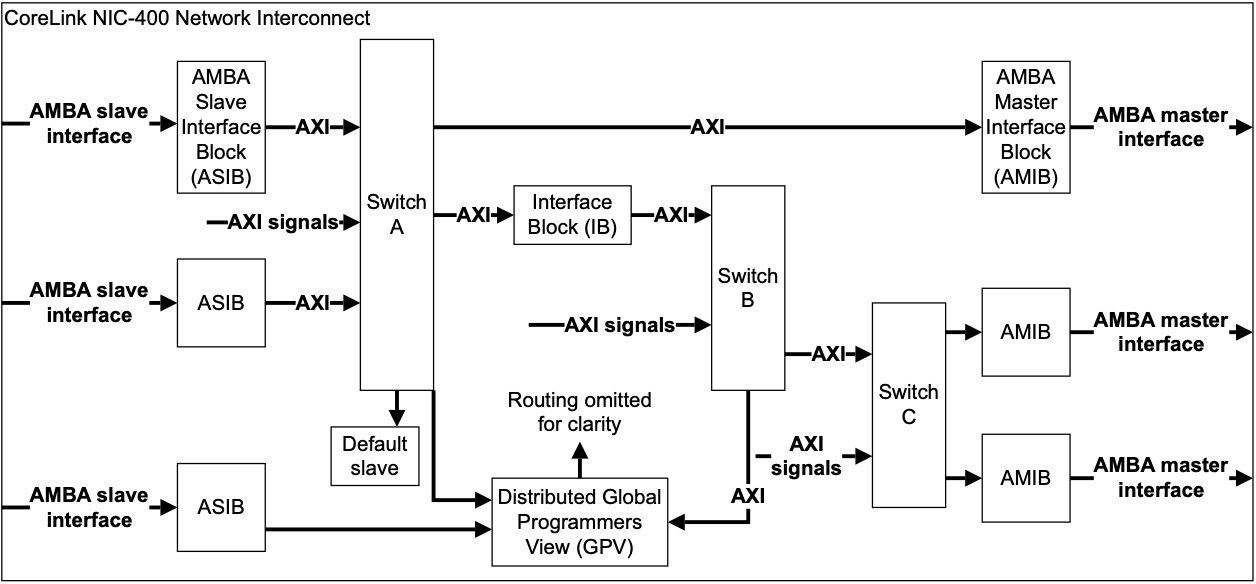

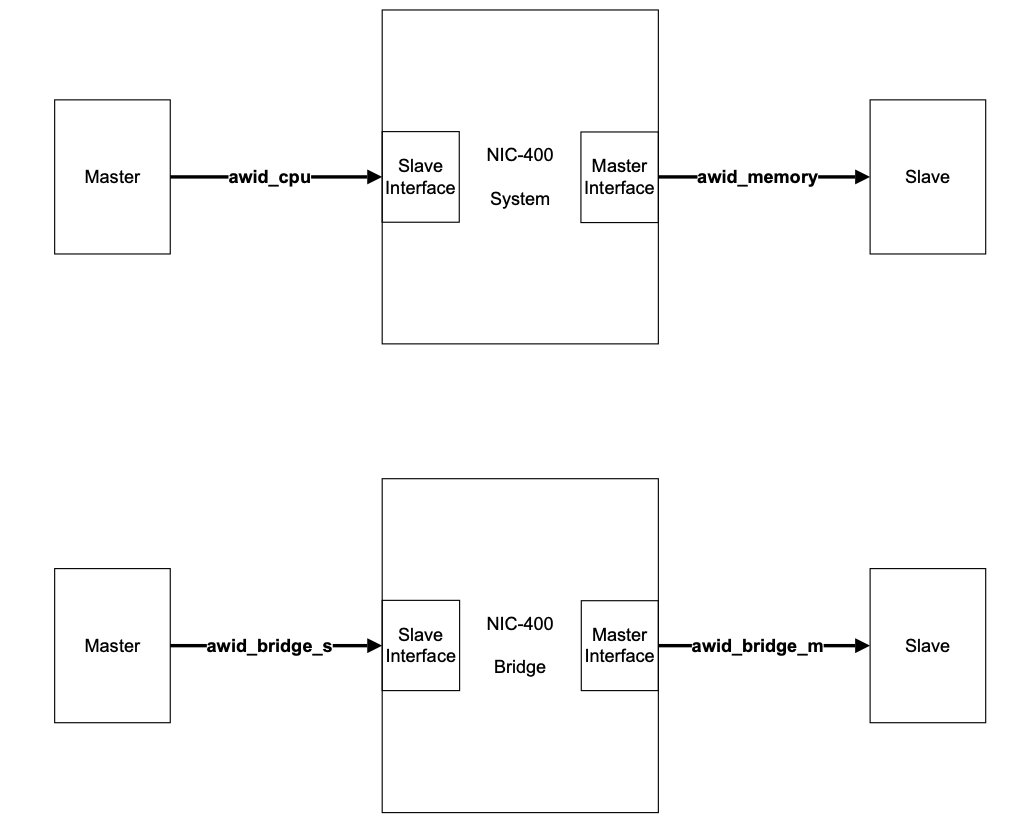

CoreLink NIC-400(Network Inter Connect)网络互连是高度可配置的,使您能够创建一个完整的高性能、优化和符合AMBA标准的网络基础设施。CoreLink NIC-400网络互连有许多可能的配置。它们的范围从单一的桥接组件,例如AHB到AXI协议转换桥,到由多达128个主站和64个AMBA协议的从站组成的复杂互连。我们可以把它看作是芯片内部的连接器。

NIC-400的配置可以由多个交换机组成,有许多拓扑结构选项。下面的图显示了NIC-400的顶层框图,其中包含:

-

多个开关。

-

多个AMBA从属接口块(ASIB)。

-

多个AMBA主接口块(AMIB)。

NIC-400支持以下特性:

-

1-128个slave接口,可以是AXI3/4,AHB-Lite salve和AHB-Lite 镜像master接口;

-

1-64个master接口,可以是AXI3/4,AHB-Lite salve,AHB-Lite 镜像master接口,APB/2/3/4;

-

APB/2/3/4;

-

层次化的时钟门控;

-

Switch之间的Noc技术(Network on chip)

-

….吧啦吧啦一堆特性

NIC-400和AMBA寄存器之间的区别

AMBA Designer是一种配置工具,可以生成CoreLink NIC-400网络互连的具体实现。AMBA Designer驱动CoreLink NIC-400网络互连生成引擎,为一组配置参数和实现脚本提供以下内容:

-

Verilog寄存器传输级(RTL)。

-

测试平台和stimulus。

-

合成脚本。

CoreLink NIC-400网络互连和AMBA设计器的文档套件和实现脚本是一起使用的。它们描述了CoreLink NIC-400网络互连的原理和配置选项。这两套文档之间没有重复的内容。以下章节描述了每套文档所提供的信息。

-

CoreLink NIC-400 Network Interconnect documentation on page 1-6.

-

AMBA Designer documentation.

-

Documentation for optional CoreLink features on page 1-6

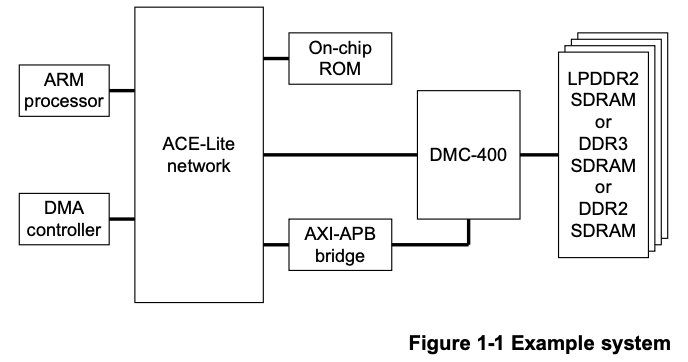

DMC-400

DMC(Dynamic Memory Controller)-400是400系列的一个动态内存控制器。DMC-400是一个符合高级微控制器总线结构(AMBA)的片上系统(SoC)外设,由ARM开发、测试和授权。它是一个高性能、区域优化的内存控制器,与AMBA ACE-Lite协议兼容。它支持以下内存设备:

-

双倍数据速率2(DDR2)同步动态随机存取存储器(SDRAM)。

-

低功耗双倍数据速率2(LPDDR2)-S2 SDRAM

-

lpddr2-s4 SDRAM

-

双倍数据速率3(DDR3)SDRAM

-

低电压DDR3 SDRAM。

DMC-400实现了SoC和芯片外部DRAM设备之间的数据传输。它通过一个或多个ACE-Lite接口连接到片上系统。它通过其存储器接口块和DFI接口连接到DRAM设备。

它实现了与以下协议的兼容:

-

ACE-Lite协议

-

AMBA3 APB协议

-

JEDEC LPDDR2 JESD209-2标准

-

JEDEC DDR3 JESD79-3D标准

-

JEDEC DDR2 JESD79-2E标准

-

DFI v2.1.1规范。

DMC400有以下特性:

-

可在Verilog中使用的软宏单元

-

可配置的硬件,支持面积和性能优化

-

多个ACE-Lite系统接口

-

多个未完成的交易

-

系统服务质量(QoS)和请求仲裁,以实现低延迟传输和内存带宽的最佳利用

-

对交易障碍的保护

-

ACE-Lite系统接口的可配置位宽

-

独立的读接受能力和写接受能力

-

AMBA ACE-Lite独占访问传输

-

ACE-Lite和APB接口之间的同步n:1时钟连接

-

多个内存接口

-

优化使用外部存储器总线

-

DRAM省电

-

可编程的外部存储器宽度

-

每个内存接口的可配置的内存芯片选择数量

-

用于64位和32位SDRAM的内存纠错码(ECC)。

-

使用DFI2.1.1接口的物理层(PHY)接口。

MMU-600

MMU-600是一个系统级内存管理单元(SMMU),将输入地址转换为输出地址。这种转换是基于地址映射和内存属性信息,这些信息可以从存储在内存中的配置表和转换表中获得。 MMU-600实现了Arm SMMU架构3.1版,即SMMUv3.1,正如Arm®系统内存管理单元架构规范,SMMU架构3.0版和3.1版所定义的。 从输入地址到输出地址的地址转换被描述为地址转换的一个阶段。MMU-600可以执行。

-

阶段1翻译,将一个输入虚拟地址(VA)翻译成一个输出物理地址(PA)或中间物理地址(IPA)。

-

阶段2翻译,将输入的IPA翻译成输出的PA。

-

第1阶段和第2阶段的组合翻译,将输入的VA翻译成IPA,然后再将该IPA翻译成输出的PA。

MMU-600为每个阶段的翻译执行翻译表行走。

除了将一个输入地址翻译成一个输出地址,一个阶段的地址翻译还定义了输出地址的内存属性。通过两阶段翻译,第二阶段翻译可以修改第一阶段翻译定义的属性。一个地址转换阶段可以被禁用或旁路,MMU-600可以为禁用和旁路的转换阶段定义内存属性。

MMU-600可以将翻译表的查找结果缓存在翻译旁观缓冲器(TLB)中。它还可以将配置表缓存在一个配置缓存中。

MU-600包含以下关键部件:

-

翻译缓冲单元(TBU),使用TLB来缓存翻译表,

-

翻译控制单元(TCU),控制和管理地址翻译。

-

分布式翻译接口(DTI)互连部件,将多个TBU连接到TCU上。

欢迎关注我的个人微信公众号,一起交流学习嵌入式开发知识!

关注「求密勒实验室」

以上是关于ARMv8基础篇400系列控制器IP的主要内容,如果未能解决你的问题,请参考以下文章