fpga实操训练(硬件乘法器)

Posted 嵌入式-老费

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了fpga实操训练(硬件乘法器)相关的知识,希望对你有一定的参考价值。

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

fpga上面的资源一般分成lut、pin、dff、dsp、pll。至于rom、ram、fifo,一般也是基于dff和lut来创建的,之前我们也讨论过。今天正好可以讨论下乘法器的使用。

硬件乘法器在fpga上也是紧俏资源。对于fpga来说,加减运算、逻辑运算、移位运算,这些都是比较简单的。但是如果涉及到乘法,就比较麻烦一点了。而除法运算,对于fpga的开发者来说,一般也是转换成乘法运算。至于说浮点运算,通常是不会涉及的,这也不是fpga的强项所在。

1、创建一个ip_dsp工程

这一步骤和之前其他工程的创建方法没有太多的不同。

2、调用lpm_mult乘法器

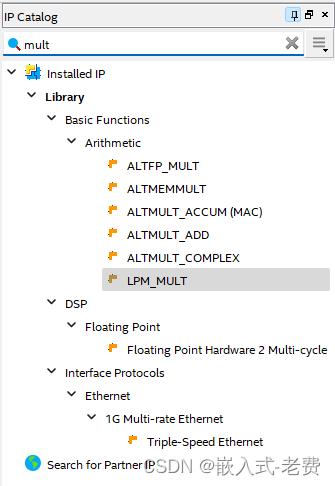

在ip catalog中输入mult,在提示的选项中选择lpm_mult,

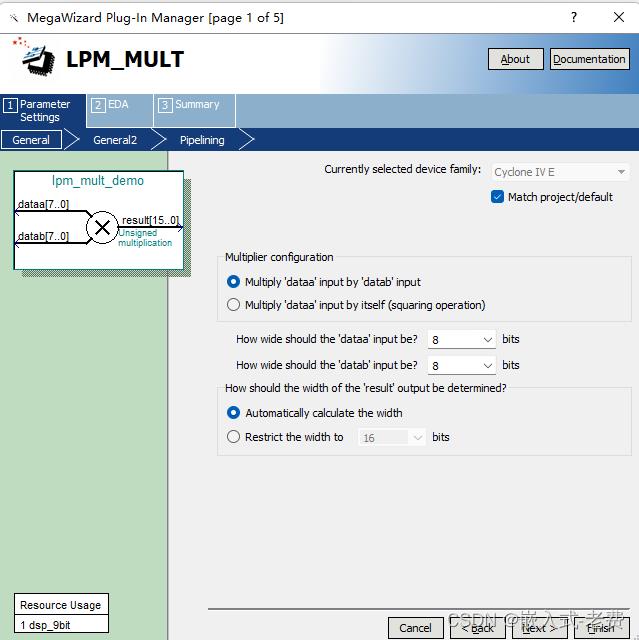

命名好文件之后,就可以开始配置了。这里面最重要的部分就是设置字节的宽度,

设置好宽度信息之后,其他部分都采用默认配置即可。

3、准备测试verilog文件

有了ip之后,下面需要做的工作就是开始编写测试verilog文件,

module top(clk, rst);

input clk;

input rst;

wire clk;

wire rst;

reg[7:0] data1;

reg[7:0] data2;

wire[15:0] result;

always@(posedge clk or negedge rst)

if(!rst)

data1 <= 8'd0;

else

data1 <= data1 + 1'b1;

always@(posedge clk or negedge rst)

if(!rst)

data2 <= 8'd0;

else

data2 <= data2 + 1'b1;

lpm_mult_demo lpm_mult_demo0(

.dataa(data1),

.datab(data2),

.result(result)

);

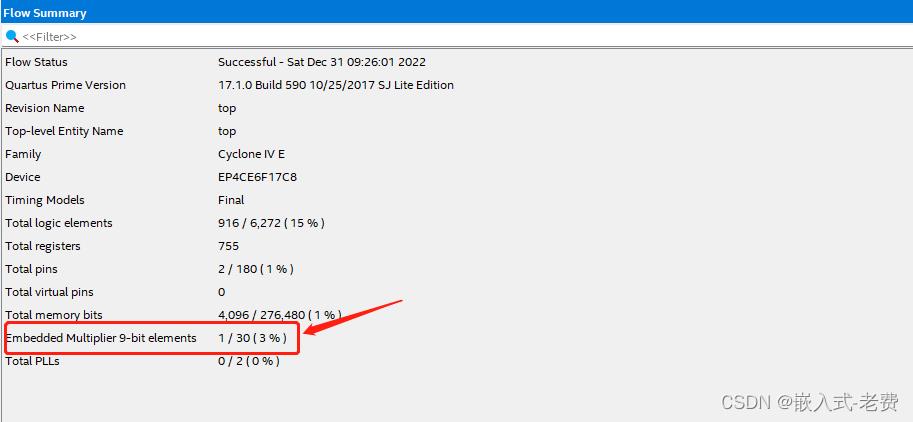

endmodule测试的方法比较简单,就是data1和data2不断自增,然后查看lpm_mult_demo的结果是多少。如果结果正确,那代表ip调用没有问题;反之则代表ip使用上面存在错误。这个时候,如果编译的话,通过compile report就会发现dsp资源确实被占用了,

4、配置sdc文件

前面说过,在fpga过程中,有必要调试编译器哪一个pin是时钟,时钟的频率是多少,这样综合器才能帮助我们做更好的优化和检查。

# Clock constraints

create_clock -name "clk" -period 20.000ns [get_ports clk]

# Automatically constrain PLL and other generated clocks

derive_pll_clocks -create_base_clocks

# Automatically calculate clock uncertainty to jitter and other effects.

derive_clock_uncertainty

# tsu/th constraints

# tco constraints

# tpd constraints

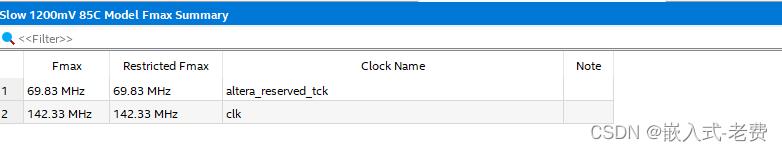

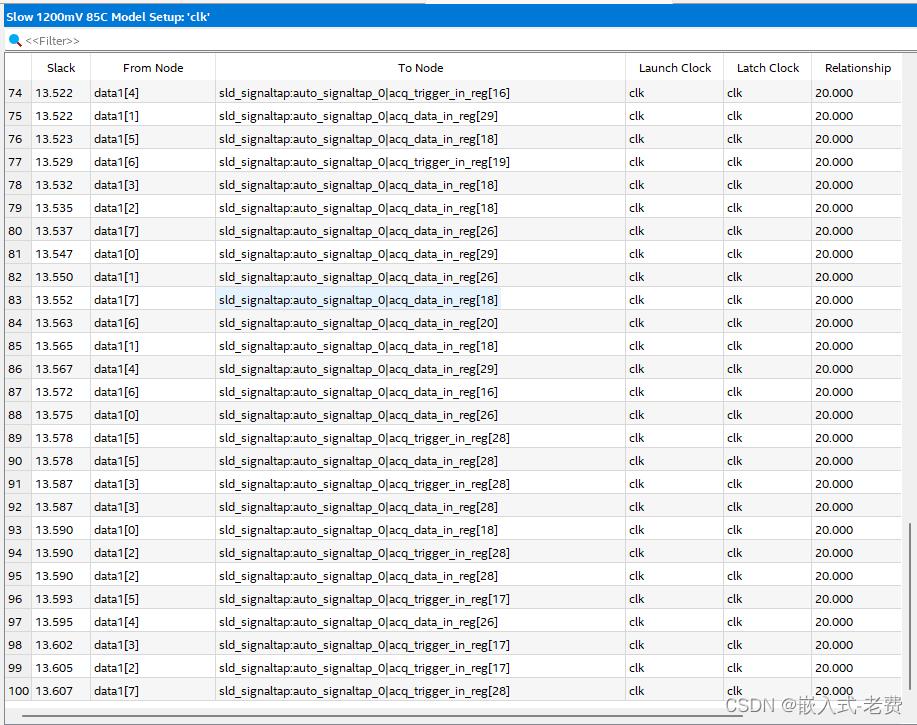

有了这一步,就可以在compile report中获取到当前最大允许的时钟频率、最差运行路径这些信息了。 比如下图,第一张是1.2v、室温85度时的最大允许频率,

最差路径信息,

5、配置pin引脚

pin的引脚部分只使用到了clk和rst,所以只要绑定到E1和N13即可。

6、配置stc文件

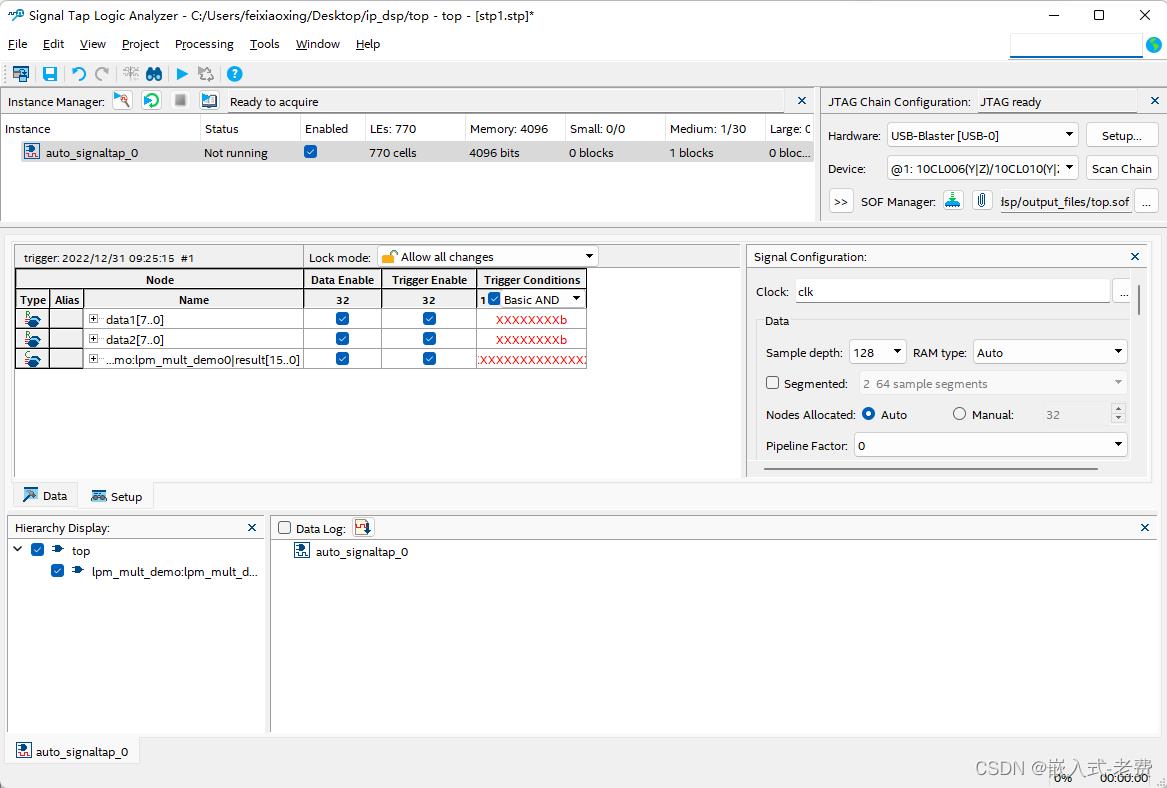

因为整个fpga工程没有信号输出,所以如果需要验证我们的测试有没有成功,有必要借助于signal tap来完成这个事情。

7、测试和验证

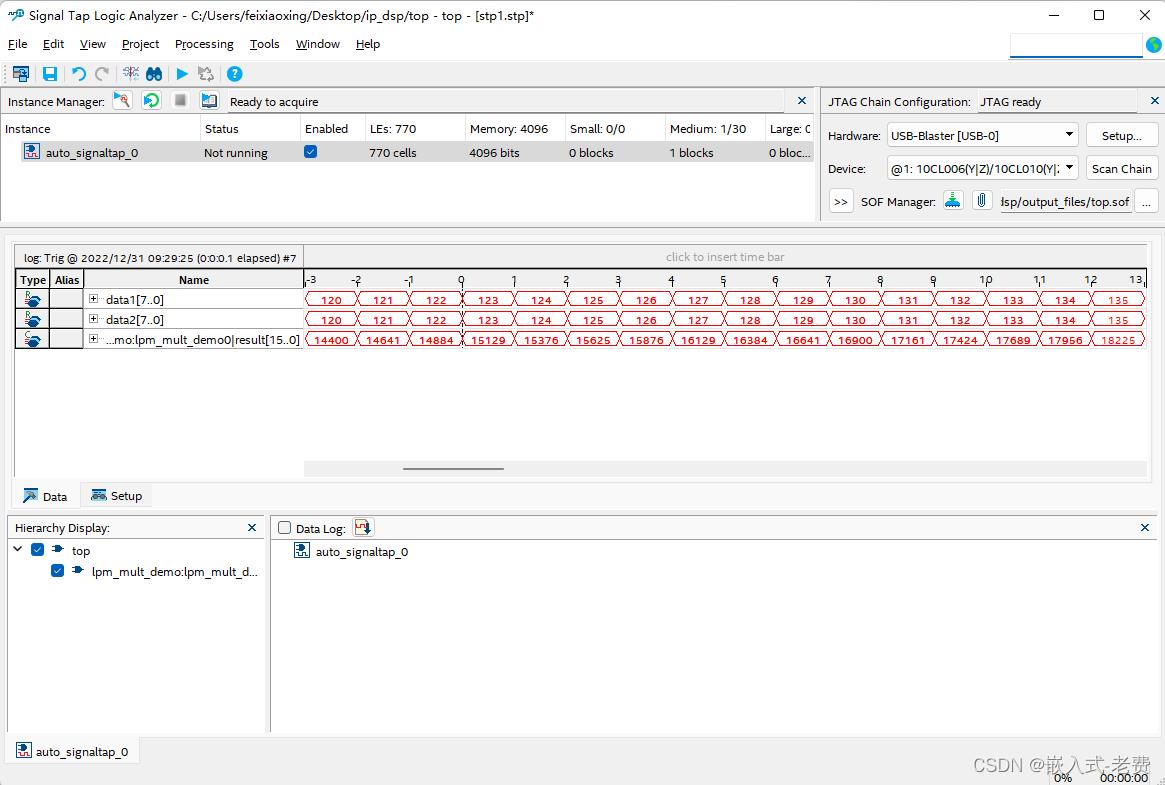

等这一切都准备好之后,就可以生成sof文件,烧入到fpga里面查看一下运行情况了。

通过观察可以看到一个有意义的现象,那就是和rom、ram不同,硬件乘法器是会立马给出运算结果的。比如说,当data1和data2都是120的时候,这个时候结果14400就出来了。这和之前的ip会在下一个节拍才给出结果是完全不一样的,这是需要注意的地方。

以上是关于fpga实操训练(硬件乘法器)的主要内容,如果未能解决你的问题,请参考以下文章