具有快表的地址变换机构以及两级页表的存储结构

Posted bfhonor

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了具有快表的地址变换机构以及两级页表的存储结构相关的知识,希望对你有一定的参考价值。

一、具有快表的地址变换机构

(一)什么是快表(TLB)

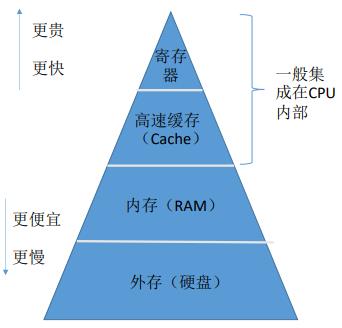

- 快表,又称联想寄存器(TLB, translation lookaside buffer ),是一种访问速度比内存快很多的高速缓存( TLB不是内存! ),用来存放最近访问的页表项的副本,可以加速地址变换的速度。

- 与此对应,内存中的页表常称为慢表。

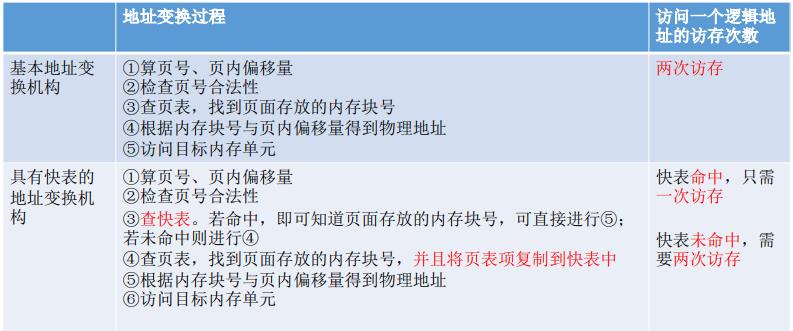

(二)引入快表后,地址的变换过程

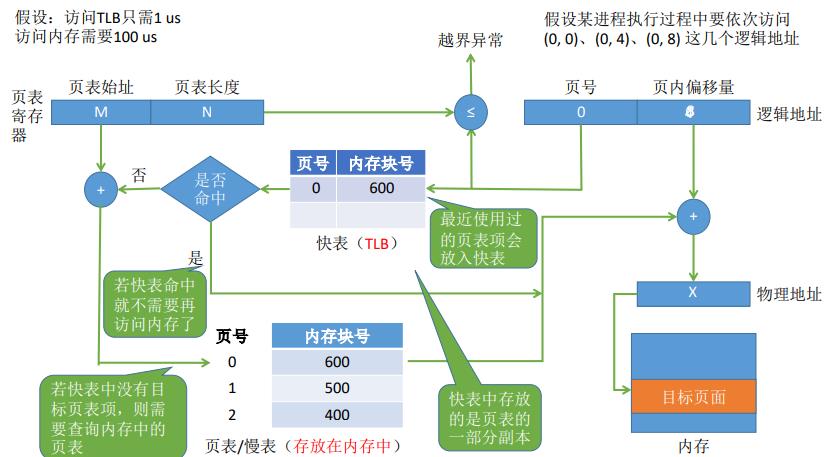

- ① CPU给出逻辑地址,由某个硬件算得页号、页内偏移量,将页号与快表中的所有页号进行比较。

- ② 如果找到匹配的页号,说明要访问的页表项在快表中有副本,则直接从中取出该页对应的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若快表命中,则访问某个逻辑地址仅需一次访存即可。

- ③ 如果没有找到匹配的页号,则需要访问内存中的页表,找到对应页表项,得到页面存放的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若快表未命中,则访问某个逻辑地址需要两次访存(注意:在找到页表项后,应同时将其存入快表,以便后面可能的再次访问。但若快表已满,则必须按照一定的算法对旧的页表项进行替换)

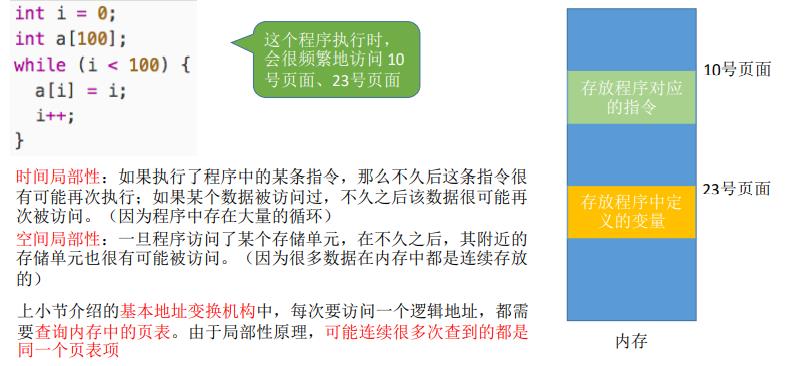

- 由于查询快表的速度比查询页表的速度快很多,因此只要快表命中,就可以节省很多时间。因为局部性原理,一般来说快表的命中率可以达到 90% 以上。

(三)局部性原理

- TLB 和 普通 Cache 的区别——TLB 中只有页表项的副本,而普通 Cache 中可能会有其他各种数据的副本

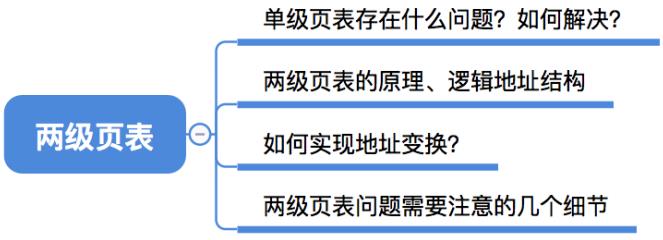

二、两级页表

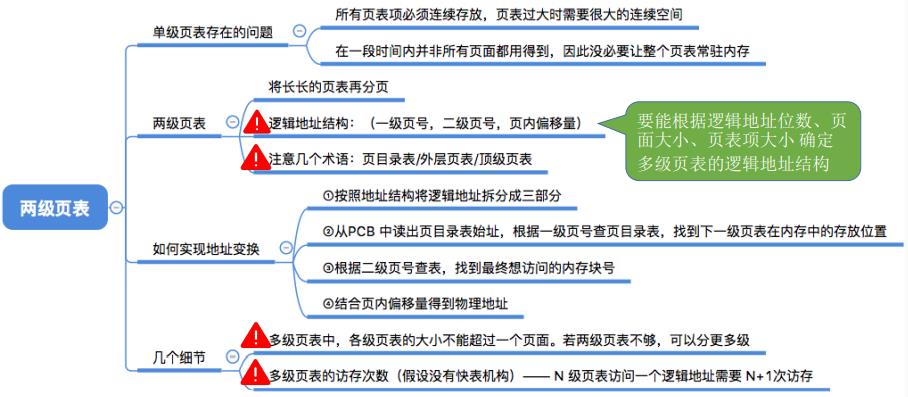

(一)单级页表存在的问题

- 根据局部性原理可知,很多时候,进程在一段时间内只需要访问某几个页面就可以正常运行了。因此没有必要让整个页表都常驻内存。

(二)如何解决单级页表的问题?

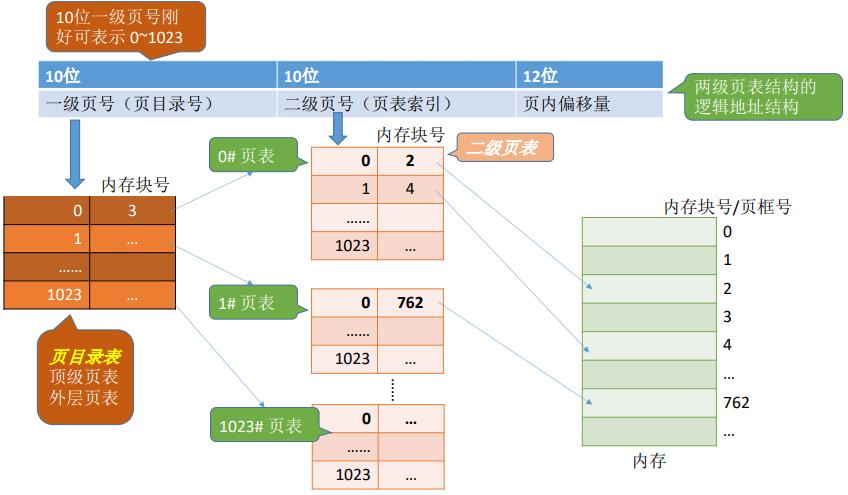

- 问题一:页表必须连续存放,因此当页表很大时,需要占用很多个连续的页框。

- 把页表再分页并离散存储,然后再建立一张页表记录页表各个部分的存放位置,称为 页目录表,或称 外层页表,或称 顶层页表

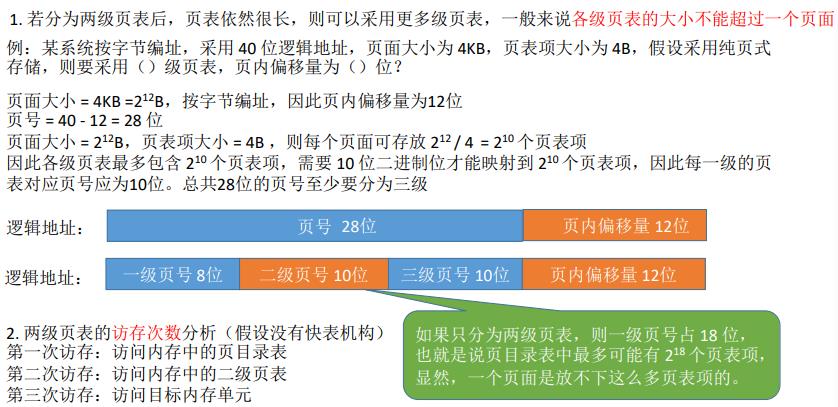

1. 两级页表的原理、地址结构

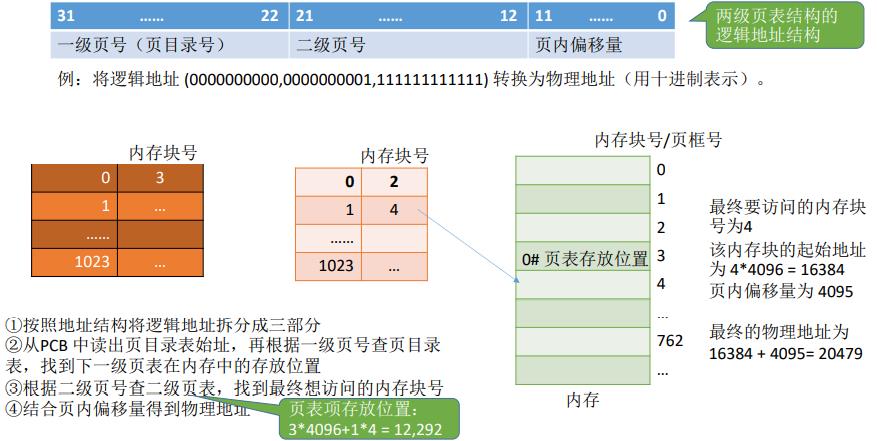

2. 如何实现地址变换

(三)如何解决单级页表的问题?

- 问题二:没有必要让整个页表常驻内存,因为进程在一段时间内可能只需要访问某几个特定的页面。

1. 需要注意的几个细节

以上是关于具有快表的地址变换机构以及两级页表的存储结构的主要内容,如果未能解决你的问题,请参考以下文章