高层次综合(HLS)常用时间术语的解释

Posted 朽月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了高层次综合(HLS)常用时间术语的解释相关的知识,希望对你有一定的参考价值。

高层次综合(HLS)常用时间术语的解释

参考文献

[1]、小鱼FPGA(微信公众号)

[2]、lauren的FPGA(微信公众号)

项目简述

前面一篇关于HLS的文章,我们已经进行了讲解,我们学习HLS并不是为了学习C、C++代码如何编写。我们是为了学习如何使用HLS进行加速,将高层次代码编译成底层逻辑。那么编译的好坏必然会引入一些指标,接下来我们将对这些指标进行进一步的说明,以便大家可以理解HLS设计。

HLS工作原理

进行HLS约束的主要原理如下:

这里说明HLS工具有两种仿真方式:

1、直接对C、C++函数进行仿真

2、对C、C++函数生成的HDL文件进行Modelsim仿真

通过上面两种仿真方式验证自己代码的正确性。其中Directives用来指导C代码编译成Verilog文件的策略。

对于HLS有以下几个特点:

1、顶层函数的参数综合成RTL代码的I/O引脚

2、不同的C函数综合成不同的RTL模块

3、默认的C函数是不展开的

4、C代码中的数组综合成Block RAM或者Ultra RAM

HLS综合主要分为三步:

1、Scheduling:决定了每一步C代码在多少周期内完成,每个周期完成什么样的操作。

2、Binding:决定了代码使用什么样的FPGA资源来实现。

3、Control logic extraction:从C代码中提取有限状态机来指导RTL设计。

高层次综合(HLS)指标

这里只有理解了HLS给我们报告中的指标是什么意思,才有可能看懂HLS的报告进而确定下一步的优化方向。

1、Area:实现该C代码多用的资源量,该资源包括LUT、registers、Block RAM、DSP48等等。

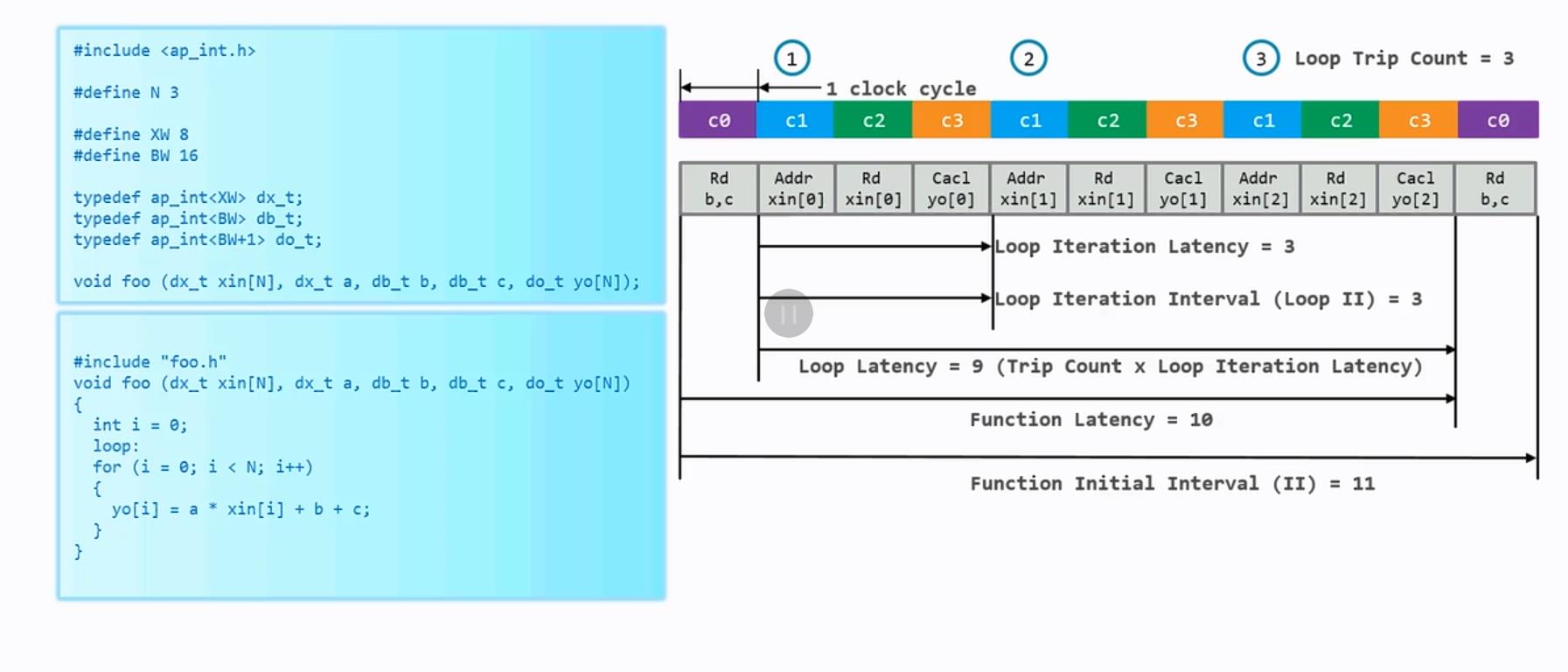

2、Latency:C函数完成所有的一次输出所需要的周期数。

3、Initiation interval(II):C函数需要多少时间才可以重新接受新的数据,也就是C函数本次开始到下一次开始所需要的周期数。

4、Loop iteration latendy:C函数中的for循环每迭代一次需要多少时钟周期。

5、Loop initiation interval:本次循环开始到下一次循环开始所需要的周期数。

6、Loop latency:完成整个循环需要多少个时钟周期。

7、Trip Count:for循环的循环迭代的次数。

下面的一个例子详细解释了上面的时间术语,大家一定要搞懂。

这里为了进一步理解上面的数据继续引入例子:

体现在时序图中如下:

对上面的例子加了流水线操作:

体现在时序图中如下:

总结

创作不易,认为文章有帮助的同学们可以关注、点赞、转发支持。为行业贡献及其微小的一部分。对文章有什么看法或者需要更近一步交流的同学,可以加入下面的群:

以上是关于高层次综合(HLS)常用时间术语的解释的主要内容,如果未能解决你的问题,请参考以下文章