标准单元库(下)

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了标准单元库(下)相关的知识,希望对你有一定的参考价值。

文章目录

3.5 状态相关时序模型(state-dependent models)

许多组合逻辑时序模块中,其输入和输出之间的时序弧依赖于模块中其他引脚的状态。输入和输出引脚之间的这些时序弧可以是正单边类型时序弧、负单边类型时序弧也可以既是正单边类型又是负单边类型时序弧。异或门( x o r xor xor)以及同或门( x n o r xnor xnor)单元就是一个例子,其输入到输出的时序弧可以是正单边类型的也可以是负单边类型的。 在这种情况下,其时序行为可能会有所不同,具体取决于该模块其他输入的状态。通常,取决于引脚状态的多个时序模型被称为状态相关的时序模型(state-dependent models)。

XOR, XNOR和时序逻辑元件

考虑一个双输入引脚的异或元件。输入引脚 A 1 A1 A1到输出引脚 Z Z Z当另一个输入引脚 A 2 A2 A2是逻辑 0 0 0状态时是正单边类型的,当是逻辑 1 1 1时则是负单边类型的。这两个时序模型是使用状态相关的时序模型指定的。 A 2 A2 A2为逻辑 0 0 0时从 A 1 A1 A1到 Z Z Z的时序模型如下所示:

pin (Z)

direction : output;

max_capacitance : 0.0842;

function : "(A1^A2)";

timing()

related_pin : "A1";

when : "!A2";

sdf_cond : "A2 == 1'b0";

timing_sense : positive_unate;

cell_rise(delay_template_3x3)

index_1 ("0.0272, 0.0576, 0.1184"); /* Input slew */

index_2 ("0.0102, 0.0208, 0.0419"); /* Output load */

values( \\

"0.0581, 0.0898, 0.2791", \\

"0.0913, 0.1545, 0.2806", \\

"0.0461, 0.0626, 0.2838");

. . .

状态相关条件使用

w

h

e

n

when

when条件进行指定。尽管元件模型摘要只展示了cell_rise时延,但其他时序模型(cell_fall,rise_transition和fall_transition表)同样是使用

w

h

e

n

when

when条件指定的。当

w

h

e

n

when

when条件所指定的改变时,如

A

2

A2

A2是逻辑

1

1

1的时候,会有一个单独的时序模型如下:

timing()

related_pin : "A1";

when : "A2";

sdf_cond : "A2 == 1'b1";

timing_sense : negative_unate;

cell_fall(delay_template_3x3)

index_1 ("0.0272, 0.0576, 0.1184");

index_2 ("0.0102, 0.0208, 0.0419");

values( \\

"0.0784, 0.1019, 0.2269", \\

"0.0943, 0.1177, 0.2428", \\

"0.0997, 0.1796, 0.2620");

. . .

sdf_cond用来指定生成SDF文件时要使用的时序弧的条件,详情参见后边3.9节中的实例。

状态相关的时序模型可用于各种类型的时序弧,许多时序逻辑单元会使用状态相关的时序模型指定建立时间或保持时间的时序约束。以下是使用状态相关的时序模型进行保持时间约束的扫描触发器(scan flip-flop)的一个示例。其中,分为 S E SE SE引脚有效或是无效这两类时序模型。

pin (D)

. . .

timing()

related_pin : "CK";

timing_type : hold_rising;

when : "!SE";

fall_constraint(hold_template_3x3)

index_1("0.08573, 0.2057, 0.3926");

index_2("0.08573, 0.2057, 0.3926");

values("-0.05018, -0.02966, -0.00919",\\

"-0.0703, -0.05008, -0.0091",\\

"-0.1407, -0.1206, -0.1096");

. . .

上述时序模型是在当SE引脚为

0

0

0的时候使用,当SE引脚为

1

1

1的时候即

w

h

e

n

when

when条件为

1

1

1时的模型是相似的。

可同时使用状态相关时序模型和状态无关时序模型用以指定一些时序关系。其中,时序分析将使用状态相关时序模型如果元件的状态已知且包括在一种状态相关的时序模型中。如果状态相关时序模型并不包括元件的条件,则使用状态无关时序模型的时序。例如,考虑保持时间约束只由一个SE引脚为逻辑

0

0

0的条件指定,而没有为逻辑

1

1

1的独立时序模型的情况。在该场景下,如果SE引脚置为

1

1

1,此时便使用状态无关时序模型。如果此时状态无关时序模型并没有指定,就意味着没有任何有效保持时间约束。

可以为时序库中的任何属性进行指定状态相关模型。因此可存在功率、漏电功率、过渡时间、上升和下降延迟、时序约束等状态相关的模型。下面给出了一个状态相关的漏电功率模型:

leakage_power()

when : "A1 !A2";

value : 259.8;

leakage_power()

when : "A1 A2";

value : 282.7;

3.6 黑盒接口时序模型(interface timing model for a black box)

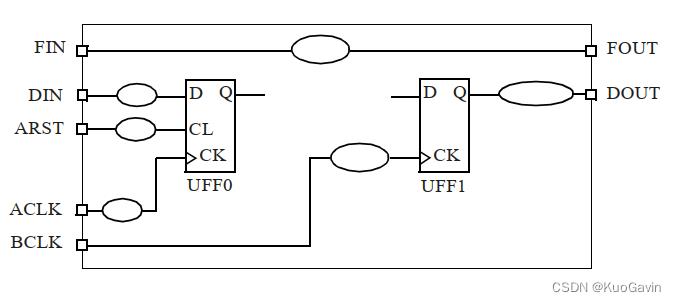

该部分描述的是黑盒(任意模块或块)的 I O IO IO接口的时序弧。一个时序模型捕获黑盒的 I O IO IO接口的时序。黑盒接口模型可以同时具有组合逻辑时序弧和时序逻辑时序弧。一般而言,这些时序弧也可以是状态相关的。

如上图所示,时序弧可以归为如下几类:

- 输入到输出的组合逻辑时序弧(input to output combinational arc):对应于从输入到输出的直接组合逻辑路径,比如输入引脚 F I N FIN FIN到输出引脚 F O U T FOUT FOUT;

- 输入时序时序弧(input sequential arc):对应于连接到触发器D引脚( D − p i n D-pin D−pin)的输入端口的建立时间或保持时间。通常,在将模块的输入端口连接到触发器的D引脚之前,可以存在一些组合逻辑。这样的一个例子是在输入端口 D I N DIN DIN上相对于时钟端口 A C L K ACLK ACLK的建立时间检查;

- 异步输入时序弧(asynchronous input arc):与触发器的异步输入引脚的恢复时间或移除时间约束类似。例子是输入引脚 A R S T ARST ARST连接至触发器 U F F 0 UFF0 UFF0的异步置零引脚 C L CL CL;

- 输出时序时序弧(output sequential arc):与触发器时钟引脚到 Q Q Q引脚的输出传播时延时序类似。一般而言,在模块输出和触发器输出之间可存在组合逻辑。例子就是从时钟引脚 B C L K BCLK BCLK到触发器 U F F 1 UFF1 UFF1的输出端口 D O U T DOUT DOUT之间。

除了以上的时序弧,对于黑盒的外部时钟引脚可做脉冲宽度(pulse width)检查。同时可能定义黑盒的内部节点并定义这些节点间的衍生时钟(generated clocks),指定这些节点间的时序弧。总而言之,一个黑盒模型可具有如下时序弧:

- 纯组合逻辑路径的输入到输出时序弧(Input to output timing arcs);

- 从同步输入端口到相关时钟端口的建立时间和保持时间时序弧(Setup and hold timing arcs);

- 从异步输入端口到相关时钟端口的恢复时间和撤销时间时序弧(Recovery and removal timing arcs);

- 从时钟端口到输出端口的输出传播延迟(Output propagation delay);

如上所述的接口时序模型并非旨在捕获黑盒的内部时序,而只是捕获其接口上的时序。

3.7 高级时序建模(advanced timing modeling)

非线性延迟模型(NLDM)这类的时序模型是基于输出负载电容和输入过渡时间来表示通过时序弧的延迟的。实际上,单元输出的负载不仅包括电容还应当包括互连电阻(interconnect resistance)。由于NLDM方法假设输出负载为纯电容,因此互连电阻成为了一个问题。即使互连电阻不为零,但当互连电阻的影响较小时,仍使用了这些NLDM模型。在互连电阻存在的情况下,延迟的计算方法通过在单元的输出端获得等效的有效电容(effective capacitance)来改进NLDM模型。延迟计算工具中使用的“有效”电容法获得的等效电容可保证单元输出延迟与具有RC互连的单元输出延迟相同。有效电容法将在5.2节里的延迟计算部分再详细介绍。

随着特征尺寸的缩小,由于波形变得高度非线性,互连电阻的影响会导致较大的误差,各种建模方法为单元的输出驱动能力提供了更高的精度。通常,这些方法通过用等效电流源对驱动器(driver)的输出级进行建模来获得更高的精度。例如CCS(Composite Current Source)复合电流源或ECSM(Effective Current Source Model)有效电流源模型:CCS时序模型通过使用随时间变化且依赖电压的电流源,为建模单元输出驱动能力提供了更高的精度。通过为不同情况下的接收引脚电容(receiver pin capacitance)和输出充电电流(output charging currents)指定详细时序模型,可以提供时序信息。接下来描述CCS模型的细节。

3.7.1 接收引脚电容(receiver pin capacitance)

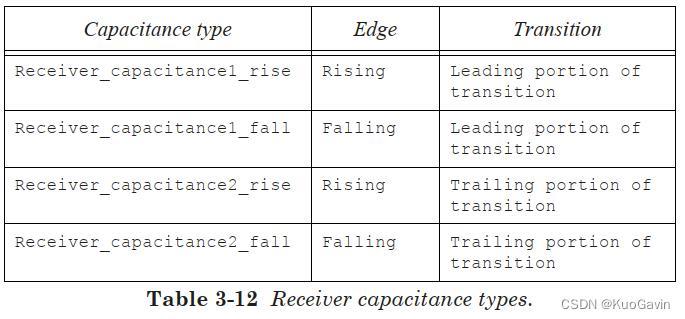

接收引脚电容对应于NLDM模型中指定的输入引脚电容。不像NLDM模型的引脚电容,CCS模型允许在过渡波形的不同部分进行分开指定接受引脚电容。由于互连RC和由元件内部输入设备的米勒效应(Miller effect)所引起的等效非线性输入电容,接收引脚电容值会在过渡波形的不同点处发生变化。该电容值因此在最初/起始部分(leading portion)与其尾部部分(tailing portion)波形的建模是不同的。

接收电容可以在引脚级别(pin level)上指定(如NLDM模型),通过该引脚的所有时序弧都使用该电容值;或者,接收电容可以在时序弧(timing arc level)级别上指定,在这种情况下可以为不同的时序弧指定不同的电容模型。接下来将介绍这两种指定接收引脚电容的方法:

- 在引脚级别指定电容(specifying capacitance at the pin level):

当在引脚级别指定,接收引脚电容的指定一维表格如下:

pin (IN)

. . .

receiver_capacitance1_rise ("Lookup_table_4")

index_1: ("0.1, 0.2, 0.3, 0.4"); /* Input transition */

values("0.001040, 0.001072, 0.001074, 0.001085");

i n d e x _ 1 index\\_1 index_1指定了该接收引脚的输入过渡时间索引值。一维表格中的 v a l u e s values values指定了输入引脚上用于上升沿波形的接收电容。

与上面示例中的receiver_capacitance1_rise表格类似,receiver_capacitance2_rise表格为波形的后续部分指定了输入引脚上用于上升沿波形的接收电容。而下降电容(用于下降沿输入波形的引脚电容)分别由表格receiver_capacitance1_fall和receiver_capacitance2_fall指定。

- 在时序弧级别指定电容(specifying capacitance at the timing arc level):

接收引脚电容值也可以在时序弧级别上,根据输入过渡时间和输出负载以二维表格的形式来指定。以下给出了在时序弧级别指定电容的示例。本示例指定了输入引脚 I N IN IN上波形初始部分的接收引脚上升电容,该电容取决于输入引脚 I N IN IN上的过渡时间和输出引脚 O U T OUT OUT上的负载。

pin (OUT)

. . .

timing ()

related_pin : "IN" ;

. . .

receiver_capacitance1_rise ("Lookup_table_4x4")

index_1("0.1, 0.2, 0.3, 0.4"); /* Input transition */

index_2("0.01, 0.2, 0.4, 0.8"); /* Output capacitance */

values("0.001040 , 0.001072 , 0.001074 , 0.001075", \\

"0.001148 , 0.001150 , 0.001152 , 0.001153", \\

"0.001174 , 0.001172 , 0.001172 , 0.001172", \\

"0.001174 , 0.001171 , 0.001177 , 0.001174");

. . .

. . .

上面的示例指定了receiver_capacitance1_rise的模型,库中也包含有关receiver_capacitance2_rise、receiver_capacitance1_fall和receiver_capacitance2_fall的类似定义。

下表总结了四种不同类型的接收电容类型。如上所述,可以在引脚级别将它们指定为一维表格,或在时序弧级别将它们指定为二维表格。

3.7.2 输出电流(output current)

在CCS模型中,非线性时序表现为输出电流。输出电流信息被指定为一个查找表,该表的查找取决于输入过渡时间和输出负载。

输出电流会根据输入过渡时间和输出负载电容的不同组合被指定,对于每一个组合,都将分别指定一个输出电流波形。本质上,此处的波形指的是随时间变化的输出电流值。以下示例使用output_current_fall指定了用于下降输出波形的输出电流:

pin (OUT)

. . .

timing ()

related_pin : "IN" ;

. . .

output_current_fall ()

vector ("LOOKUP_TABLE_1x1x5")

reference_time : 5.06; /* Time of input crossing

threshold */

index_1("0.040"); /* Input transition */

index_2("0.900"); /* Output capacitance */

index_3("5.079e+00, 5.093e+00, 5.152e+00,

5.170e+00, 5.352e+00");/* Time values */

/* Output charging current: */

values("-5.784e-02, -5.980e-02, -5.417e-02,

-4.257e-02, -2.184e-03");

. . .

. . .

. . .

reference_time是指输入波形超过延迟阈值的时间,

i

n

d

e

x

_

1

index\\_1

index_1和

i

n

d

e

x

_

2

index\\_2

index_2是指输入过渡时间和所使用的输出负载电容,而

i

n

d

e

x

_

3

index\\_3

index_3是时间。

i

n

d

e

x

_

1

index\\_1

index_1和

i

n

d

e

x

_

2

index\\_2

index_2(输入过渡时间和输出负载电容)只能有一个值,

i

n

d

e

x

_

3

index\\_3

index_3是指时间值,表值是指相应的输出电流。因此,对于给定的输入过渡时间和输出负载,输出电流波形是时间的函数。同样,还指定了用于输入过渡时间和输出电容的其他组合的查找表。

类似地可以使用output_current_rise去指定上升输出波形的输出电流。

3.7.3 串扰噪声分析(models for crosstalk noise analysis)

本节介绍用于串扰噪声(或毛刺)分析的CCS模型,又被称为CCSN(CCS Noise)模型。CCS噪声模型是结构(structural)模型,并表示为单元内的不同 沟道连接块-CCB(Channel Connected Blocks) 。

什么是CCB? CCB是指单元的源极(source)-漏极(drain)的沟道(channel)连接部分。例如,单级(single stage)单元(例如反相器、与非门和或非门单元)仅包含一个CCB,即整个单元仅通过一个沟道连接区域进行连接,而多级单元(例如与门和或门单元)包含多个CCB。

通常仅为由单元输入驱动的第一个CCB和驱动单元输出的最后一个CCB指定CCSN模型,并且会使用稳态电流、输出电压和传播噪声模型来指定这些CCSN模型。

对于单级组合逻辑单元(例如与非门和或非门单元),将为每个时序弧指定CCS噪声模型。 这些单元只有一个CCB,因此模型将会是从单元的输入引脚到输出引脚的。

以下是一个与非门单元的模型示例:

pin (OUT)

. . .

timing ()

related_pin : "IN1";

. . .

ccsn_first_stage() /* First stage CCB */

is_needed : true;

stage_type : both; /*CCB contains pull-up and pull-down*/

is_inverting : true;

miller_cap_rise : 0.8;

miller_cap_fall : 0.5;

(ccsn_dc)

index_1 ("-0.9, 0, 0.5, 1.35, 1.8"); /* Input voltage */

index_2 ("-0.9, 0, 0.5, 1.35, 1.8"); /* Output voltage*/

values ( \\

"1.56, 0.42, . . ."); /* Current at output pin */

. . .

output_voltage_rise ()

vector (ccsn_ovrf)

index_1 ("0.01"); /* Rail-to-rail input transition */

index_2 ("0.001"); /* Output net capacitance */

index_3 ("0.3, 0.5, 0.8"); /* Time */

values ("0.27, 0.63, 0.81");

. . .

output_voltage_fall ()

vector (ccsn_ovrf)

index_1 ("0.01"); /* Rail-to-rail input transition */

index_2 ("0.001"); /* Output net capacitance */

index_3 ("0.2, 0.4, 0.6"); /* Time */

values ("0.81, 0.63, 0.27");

. . .

propagated_noise_low ()

vector (ccsn_pnlh)

index_1 ("0.5"); /* Input glitch height */

index_2 ("0.6"); /* Input glitch width */

index_3 ("0.05"); /* Output net capacitance */

index_4 ("0.3, 0.4, 0.5, 0.7"); /* Time */

values ("0.19, 0.23, 0.19, 0.11");

propagated_noise_high ()

. . .

现在我们描述CCS噪声模型的属性:ccsn_first_stage字段表示该模型用于与非门单元的第一级CCB。如前所述,与非门单元只有一个CCB。is_needed字段几乎始终为true,但天线单元(antenna cell)等非功能性单元除外。stage_type字段中的both表示该级CCB同时具有上拉(pull-up)和下拉(pull-down)结构。miller_cap_rise和miller_cap_fall分别代表输出上升和下降过渡时的米勒(Miller)电容值。

直流电流(DC Current)

dc_current表格表示了输出引脚输出的直流电流在不同输入和输出引脚电压组合下的情况。index_1和index_2分别指定了输入和输出电压。二维表格中的values值代表了CCB输出引脚输出的DC电流。输入电压和输出电流均在库单元中有指定(通常是Volt和mA)。比如与非与门单元的输入引脚

I

N

1

IN1

IN1到输出引脚

O

U

T

OUT

以上是关于标准单元库(下)的主要内容,如果未能解决你的问题,请参考以下文章