基于FPGA的以太网TCP/IP协议实现过程记录

Posted 皇甫春云

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA的以太网TCP/IP协议实现过程记录相关的知识,希望对你有一定的参考价值。

基于FPGA的以太网的 TCP/IP 协议的学习笔记

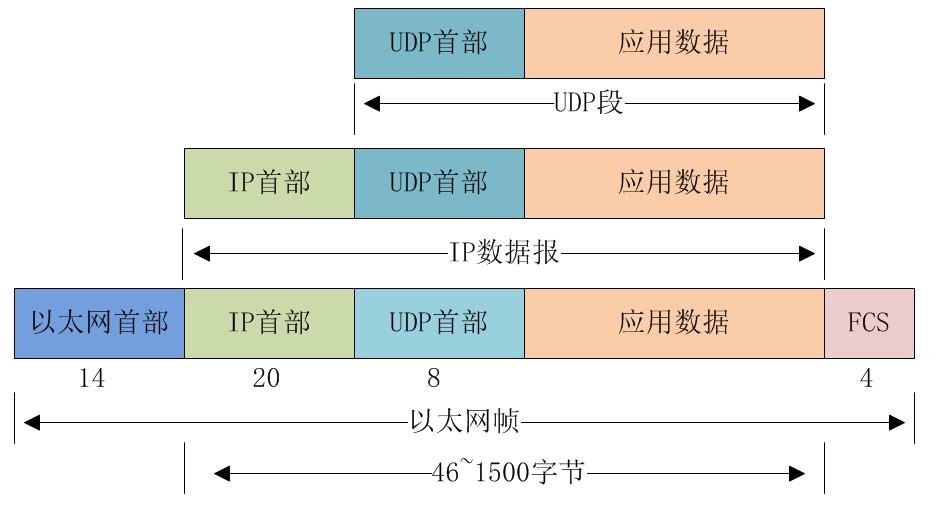

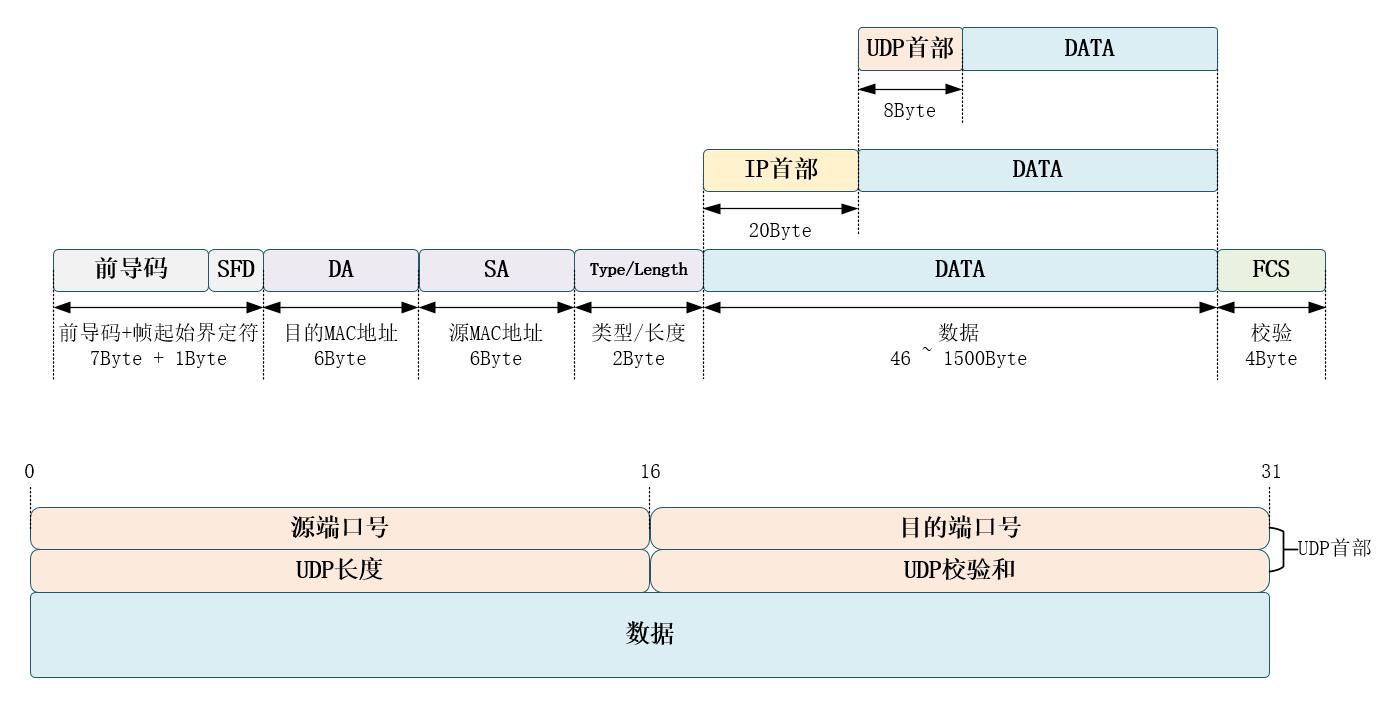

一、完整的以太网数据部分包括以下几部分:

- 前导码

- 帧起始界定符

- 以太网帧头

- IP首部

- UDP首部

- UDP数据(有效数据)

- CRC校验字节

二、针对每一部分的格式如下:

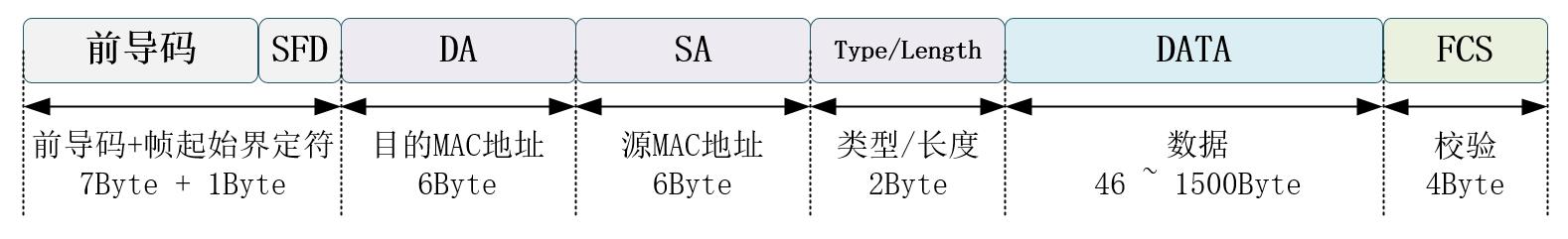

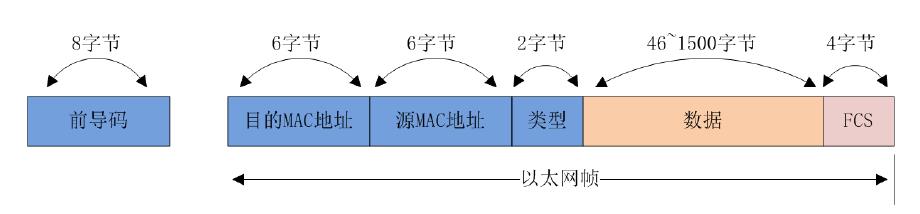

MAC数据包格式:

MAC 数据包 IEEE 对以太网上传输的数据包格式也进行了统一规定,

- 前导码:7 个字节的 0x55,用示波器看起来是一段脉冲信号。

- 帧起始界定符:1字节的0xD5。

- 目的MAC地址:数据的最终去向的地址,俗称网卡的物理地址,出厂时已经设置完毕,共6字节。

- 源MAC地址:数据的来源设备的物理地址,占用6个字节。

- 数据包类型:反映以太网每一包数据的格式,是属于OSI层级中的链路层,

写入0800 则是 IP协议

写入0806 则是 ARP协议

写入0835 则是 RARP协议

note:以太网首部包括 目的MAC地址 + 源MAC地址 +数据包类型

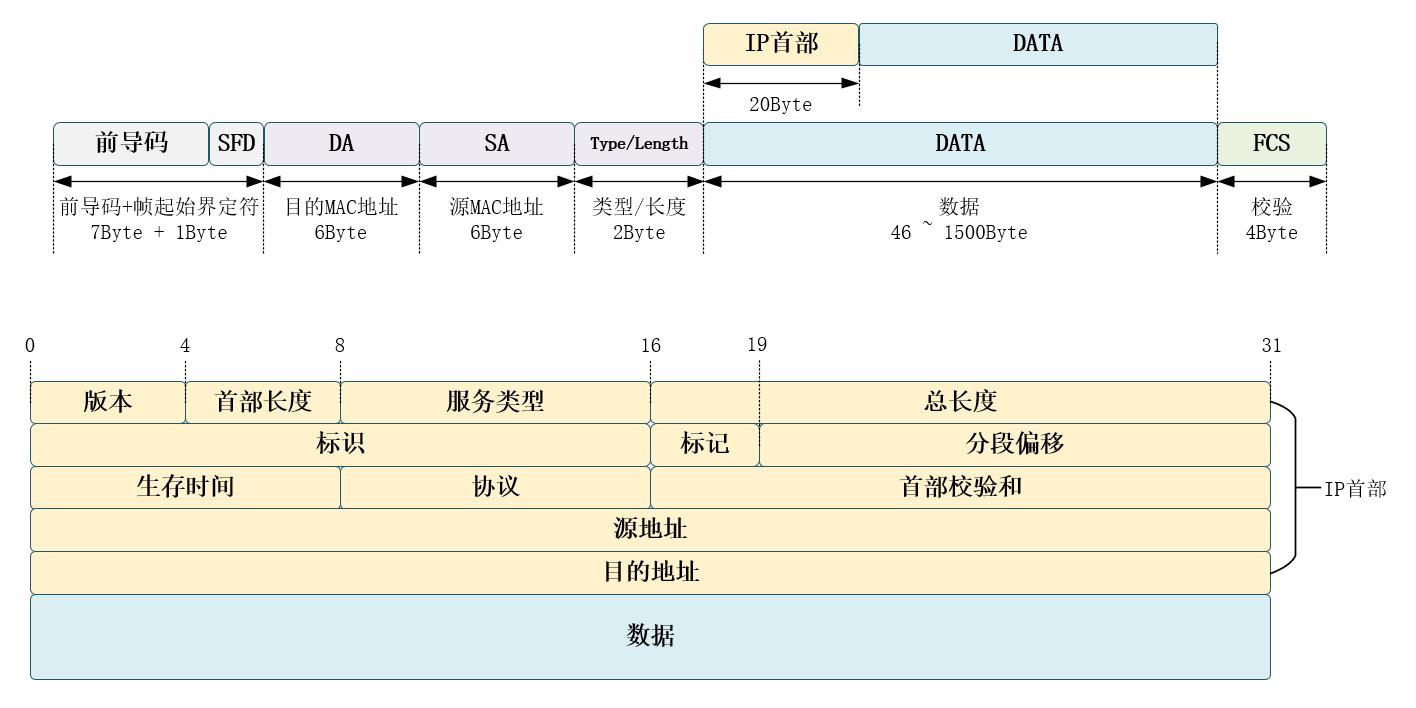

IP首部

首部长度(4 bit):最小值为5,最大值为15,以4Byte为单位,故长度可以是 20Byte ~ 60Byte。

总长度(16 bit):该字段定义整个IP数据报的字节长度,包括协议头部和数据。其最大值为65535字节。以太网协议对能够封装在一个帧中的数据有最小值和最大值的限制(46~1500个字节)。

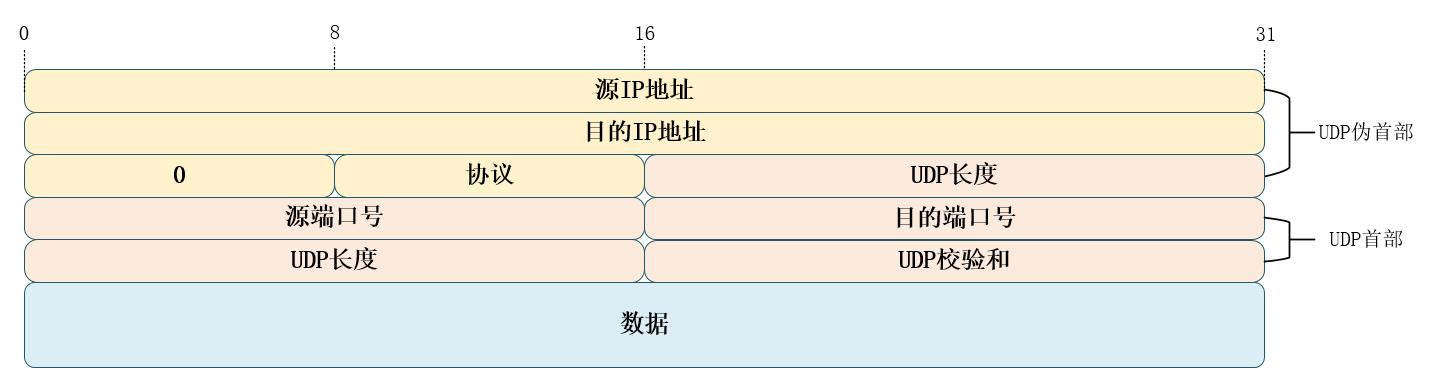

UDP首部

UDP校验和

三、 注意事项:

- IP数据包的长度最少是46字节,包括20个字节的IP和8字节的UDP的首部。

- CRC校验是对IP首部,UDP首部和有效数据校验。

- UDP模块的执行过程是,将有效数据提取出来后,在重新打包发出去,即完成了解码和编码的过程。

- UDP的长度是指包括有效数据部分和整个UDP首部8字节的总长度。

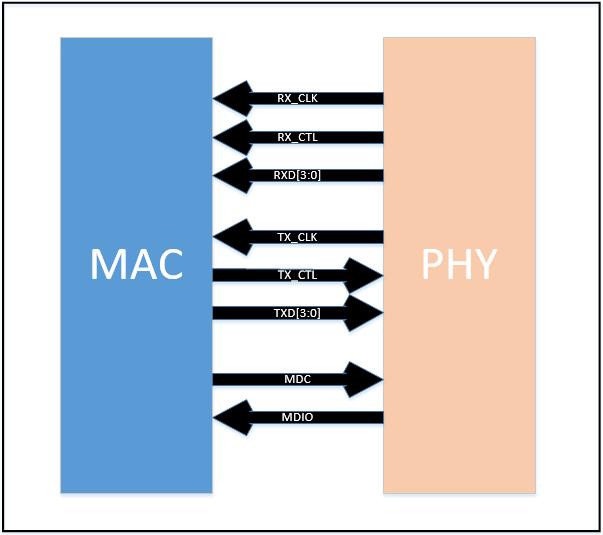

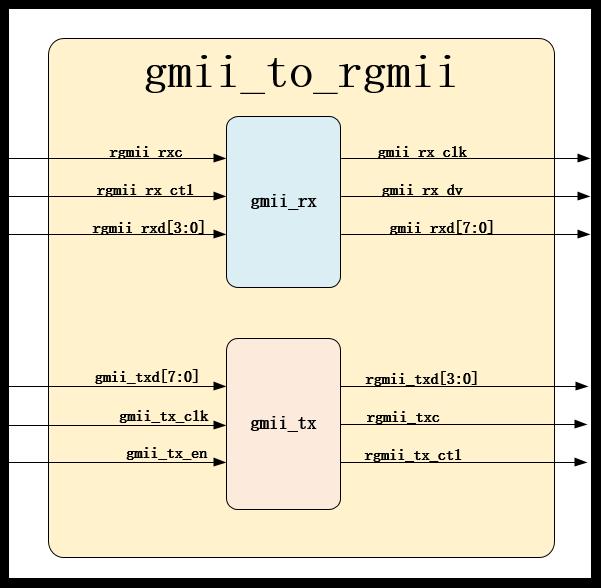

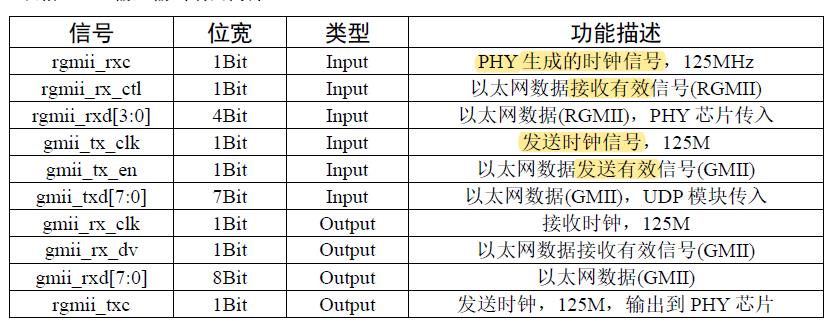

四、实现 MAC 和 PHY 的通信

RGMII接口的定义:

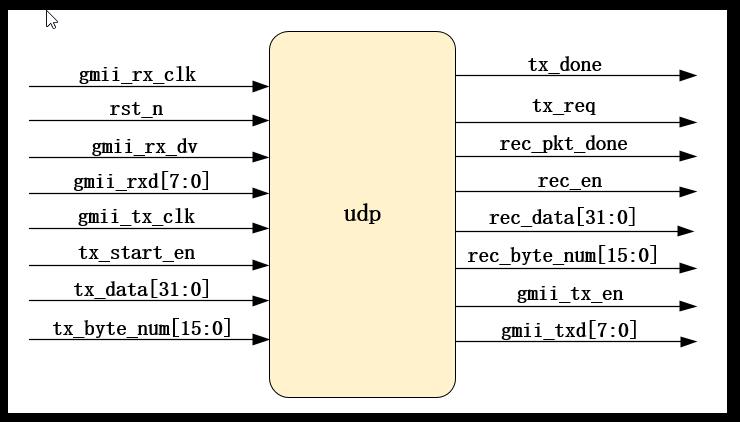

UDP模块的引脚:

当前是完成了UDP的两个模块的接收和发送程序,还需要完成接口转换模块的程序阅读和校验模块的阅读。但是此刻已经完成了核心代码的阅读了。

- UDP_TX

- UDP_RX

- CRC32_D8

- GMII_TO_RGMII

根据当前的阅读情况,可以进行以下两个任务的完成,分别是完成拓展任务,即将GMII的输出改为RMII的输出。为了方便任务的开展,可以按照以下步骤完成:

- 对现在的代码进行仿真分析,确定各个部分的仿真结果和自己的分析过程,没有出入。

- 按照教程,真实的下载到板子上,进行实际的测试,保障功能的正常。

- 完成拓展任务,即修改通信接口由GMII为RGMII类型。

- 根据项目的数据采集部分程序,修改UDP模块,实现启动采集和数据的转发。

五、 参考资料

- 踏浪Pro《FPGA Verilog开发实战指南——基于Xilinx Spartan6》进阶提高篇2021.7.10

- 黑金的 AX7101~千兆以太网传输实验

以上是关于基于FPGA的以太网TCP/IP协议实现过程记录的主要内容,如果未能解决你的问题,请参考以下文章