S5PV210的中断处理机制详解

Posted 正在起飞的蜗牛

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了S5PV210的中断处理机制详解相关的知识,希望对你有一定的参考价值。

1、ARM的中断机制介绍

2、S5PV210芯片的中断处理过程

2.1、中断处理第一阶段

S5PV210芯片的中断处理第一阶段就是异常向量表的跳转,并没有任何特别,看上面的参考博客即可;

2.2、中断处理第二阶段

(1)找到发生的对应中断源:芯片支持不止一个中断,当发生中断时首先要区分出是哪个中断源发生了中断。S5PV210芯片有4个中断状态寄存器,寄存器的每个位表示一个中断的状态,通过读取中断状态寄存器的值就可以知道是哪个中断源发生中断。4个中断状态寄存器理论上支持128个中断,实际有的位是保留的,实际支持不足128个中断源;

(2)调用对应的中断处理程序。在中断的初始化阶段,会为每个中断都绑定中断处理程序,当发生中断后硬件会自动将对应中断的处理程序推送到VICnADDR寄存器中,我们只需要读取,省去了查找的过程;

补充:S5PV210芯片在硬件上设计了中断编号和中断处理程序的查找过程,降低软件程序员的编程难度,并且提高了中断的响应速度,具体中断查找过程请看下面寄存器的介绍;

3、中断处理的流程

3.1、初始化阶段

(1)绑定总的中断处理程序(IRQ_hander)到异常向量表;

(2)初始化中断控制器:包括禁止中断、设置中断优先级、设置中断的模式;

(2)给每个中断源绑定特定的中断处理程序(irq_hander);

(3)使能对应中断;

3.2、处理中断阶段

(1)当中断发生时,首先跳转到异常向量表执行总的中断处理程序(IRQ_hander);

(2)保护中断现场;

(3)区分出是哪个中断源发生了中断,也就是得到中断号;

(4)调用初始化阶段为每个中断源绑定的特定的中断处理程序;

(5)恢复现场;

4、S5PV210芯片中断体系

4.1、向量中断控制器:VIC

| 表项 | 含义 |

|---|---|

| Module | 中断源属于的模块 |

| VIC port no | 中断源在对应VIC的端口号 |

| No | 中断源在整个中断系统中的编号 |

| INT Request | 中断请求的类型,也就是这个中断是什么作用 |

(1)VIC(Vectored Interrupt Controller)控制器有4个,VIC0~VIC3;

(2)控制器的每个位代表一个中断源,理论上S5PV210芯片最多支持128个中断源,实际只支持93个中断源,有些位是空的;

(3)4个VIC控制器的中断编号是连续的,比如:VIC0的中断编号是0-31,以此类推,VIC3的中断编号是96-127;

(4)数据手册中有对4个VIC控制器每个位的说明,详情看上面的图和表格;

4.2、中断使能寄存器:VICINTENABLE

(1)寄存器功能:使能中断;

(2)中断使能寄存器有4个,刚好对应4个VIC,寄存器的每个位对应一个中断源;

(3)读寄存器:0代表中断被禁止,1代表中断已经使能;

(4)写寄存器:写0没有任何作用,写1表示使能中断;

补充:寄存器的命名是有规律的,比如:VICINTENABLE寄存器,VIC代表寄存器属于向量中断控制器,INT是中断的英文(interrupt)缩写,ENABLE的英文意思就是允许的意思;

4.3、中断禁止寄存器:VICnINTENCLEAR

(1)中断禁止寄存器和中断使能寄存器是相对应的,一个负责禁止中断一个负责使能中断;

(2)需要注意中断禁止寄存器是只写的;

(3)中断禁止和使能有两种设计思路:一种是S5PV210这种将禁止和使能分别用两个寄存器去负责;另一种是将禁止和使能用同一个bit位去负责,比如写1表示禁止,写0表示使能;

4.4、中断模式选择寄存器:VICnINTSELECT

(1)中断分为普通中断(IRQ)和快速中断(FIQ),快速中断的响应速度更快,这是在硬件上就有保证;

(2)一般同时只把一个中断设置成FIQ;

(3)快速中断响应更快的原因,参考博客;《ARM中FIQ(快速中断)比IRQ(普通中断)响应快的原因》;

4.5、中断状态寄存器:VICIRQSTATUS和VICFIQSTATUS

(1)中断状态寄存器是只读的,每个位对应一个中断源的状态,读出来是0表示对应中断源未触发,读出来是1表示中断源触发;

(2)IRQ模式和FIQ模式各有4个中断状态寄存器,对应于前面介绍的4个VIC;

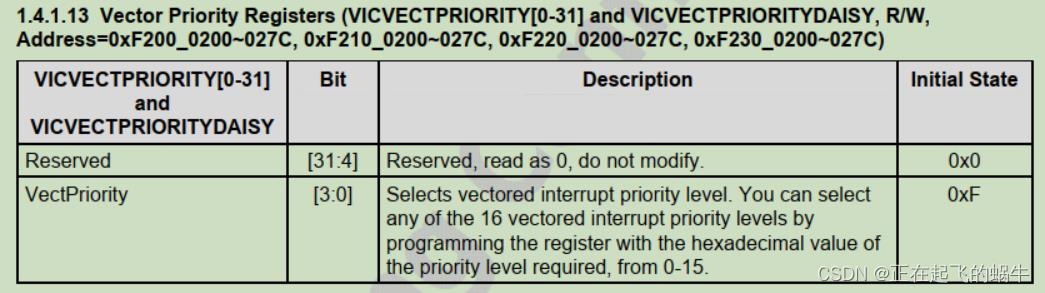

4.6、中断优先级设置寄存器:VIC[0-3]VECTPRIORITY[0-31]

(1)每个中断源都对应一个优先级设置寄存器,所以优先级寄存器总共有128个,每个VIC对应32个;

(2)优先级寄存器只有低4位有效,优先级总共分为16个优先级,默认将优先级设置成15;

4.7、中断处理程序绑定寄存器:VIC[0-3]VECTADDR[0-31]

(1)VICVECTADDR寄存器总共有128个,每个中断源对应一个;

(2)在中断的初始化阶段,将每个中断源的处理程序地址写到VICVECTADDR寄存器,当中断发生时就会自动跳转去执行对应的中断处理函数;

4.8、保存当前发生中断的处理程序的寄存器:VIC[0-3]ADDRESS

(1)VICADDRESS寄存器总共有4个,每个寄存器对应32个中断源,比如VICADDRESS0对应0-31编号的中断源,VICADDRESS1对应32-63编号的中断源;

(2)我们知道最多支持128个中断源,将其分为4组,每组32个中断源;

(3)当中断发生时,硬件会自动将发生中断的中断处理程序的地址写到VICADDRESS寄存器中,我们只需要读取即可;

(4)假设我们通过读取中断状态寄存器,知道中断编号为16的中断源发生了中断,编号16是属于VIC0的,中断处理程序地址保存在VIC0VECTADDR16寄存器中,硬件会自动将VIC0VECTADDR16寄存器的值写到VIC0ADDRESS寄存器中;

5、S5PV210芯片具体的中断处理流程

(1)在异常向量表中绑定总的中断处理程序;

(2)初始化中断控制器,通过读写相关寄存器,设置中断的优先级、模式、禁止/使能;

(3)绑定每个中断的处理程序:每个中断都对应一个中断处理程序绑定寄存器;

(3)发生中断时,依次读取4个中断状态寄存器,判断是哪个中断状态寄存器发生中断;

(4)根据发生中断的中断状态寄存器,从对应的VICADDRESS寄存器中读取到中断处理程序的地址,执行中断处理程序;

6、外部中断

以上是关于S5PV210的中断处理机制详解的主要内容,如果未能解决你的问题,请参考以下文章