成形滤波器基于FPGA的成形滤波器设计

Posted fpga&matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了成形滤波器基于FPGA的成形滤波器设计相关的知识,希望对你有一定的参考价值。

1.软件版本

ISE14.7

2.本算法理论知识

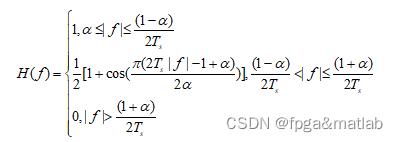

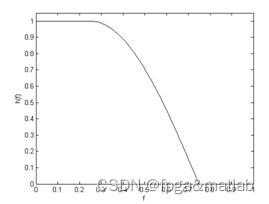

系统的指标为:滤波器的成形系数我们取50%,系统的采样率为4倍采样。在通常的设计中,成形滤波器的实现可用有限冲激响应(FIR)滤波器或无限冲激响应(IIR)滤波器。FIR滤波器可以在幅度特性随意设计的同时保证准确严格的线性相位,是本次方案的选择。采用的公式如下所示:

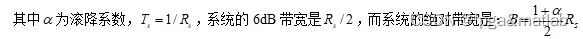

该传输函数的时域响应为:

式中,为码元周期,是奈奎斯特频率,称为滚降因子,它决定着H(f)的形状,的取值对系统性能有着重要影响。在[0,1]间取值,当较大时,时域波形的衰减快,并且振荡起伏小,这对于减小码间干扰和定时误差的影响有利,但系统占用频带变宽,频带利用率减小了,同时带内噪声对信号的影响也会增大;当较小时,系统频带利用率得到提高,噪声的影响被减弱了,但波形振荡起伏大,对码间干扰和定时误差的影响增大,系统误码率变大。

考虑到接收波形在再生判决中还要再抽样一次以得到无失真的抽样值,而理想的瞬时抽样不可能实现,也就是抽样时刻不可能完全没有误差,抽样脉冲宽度也不可能等于0,因此,为了减小抽样定时脉冲误差所带来的影响,滚降系数a不能太小,通常选择。在本文中,成形滤波器选择滚降系数a=0.5。

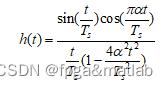

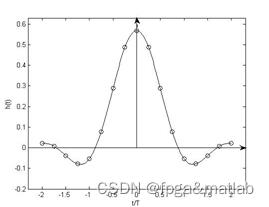

在FIR滤波器的设计之前,我们首先要要确定FIR滤波器的系数,通常这个步骤我们在MATLAB中计算。通过MATLAB仿真,我们得到其时域波形图和频率响应图如下所示:

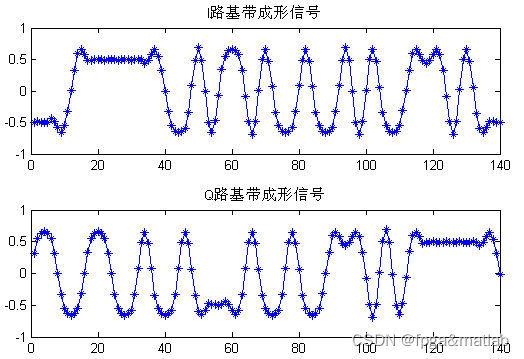

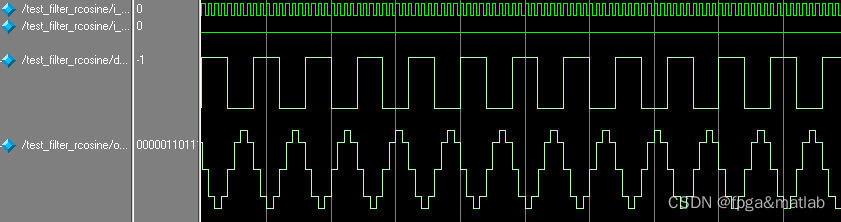

图 通过FIR滤波器的两路基带信号

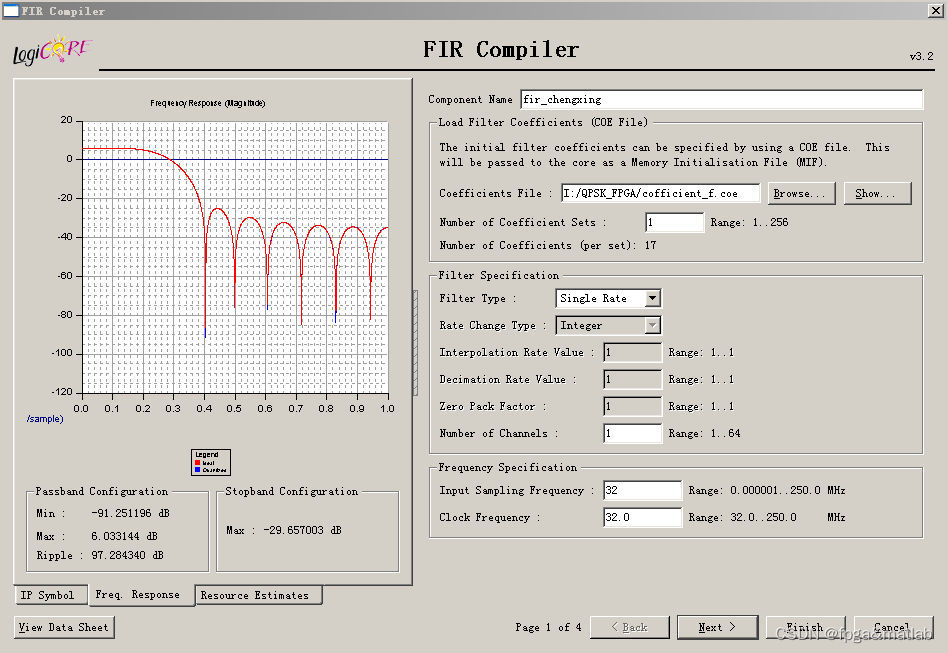

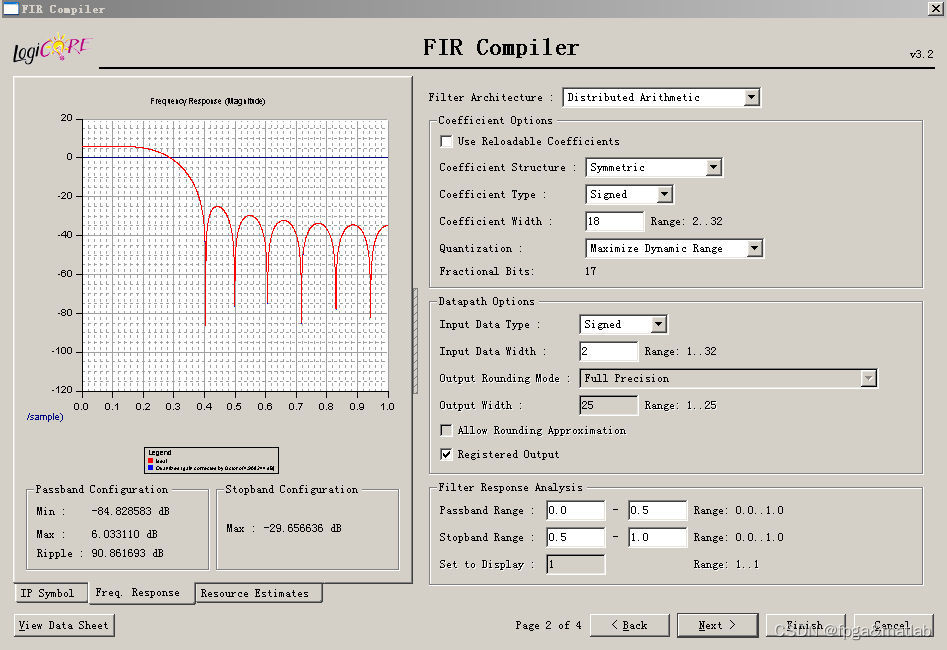

以上就是FIR成形滤波器的MATLAB仿真过程,通过MATLAB仿真,我们可以得到成形滤波器的系数为:0.02122066,0.00773409,-0.03751318,-0.07842133,-0.05305165,0.07842133,0.28931623,0.48724768,0.56830989,0.48724768,0.28931623,0.07842133,-0.05305165,-0.07842133,-0.03751318,0.00773409,0.02122066;在得到系数之后,我们将要在FPGA中通过IP核来实现FIR滤波器。本系统数据速率为8Mbit/s,系统采用的是四倍采样,所以系统时钟为32M,图3-6所示为在Xilinx公司的ISE集成开发环境中,直接免费提供了FIR滤波器的IP核资源,只要将Matlab产生的系数文件导入至IP核中,在进行简单的参数配置,即可实现预期的滤波器功能。图3-7为成型滤波器仿真结果。

3.部分源码

图1 FIR滤波器IP核设置界面1

图2 FIR滤波器IP核设置界面2

4.仿真分析

my

以上是关于成形滤波器基于FPGA的成形滤波器设计的主要内容,如果未能解决你的问题,请参考以下文章