计算机组成原理 — CPU — 流水线与执行周期

Posted 范桂飓

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机组成原理 — CPU — 流水线与执行周期相关的知识,希望对你有一定的参考价值。

目录

文章目录

CPU 流水线

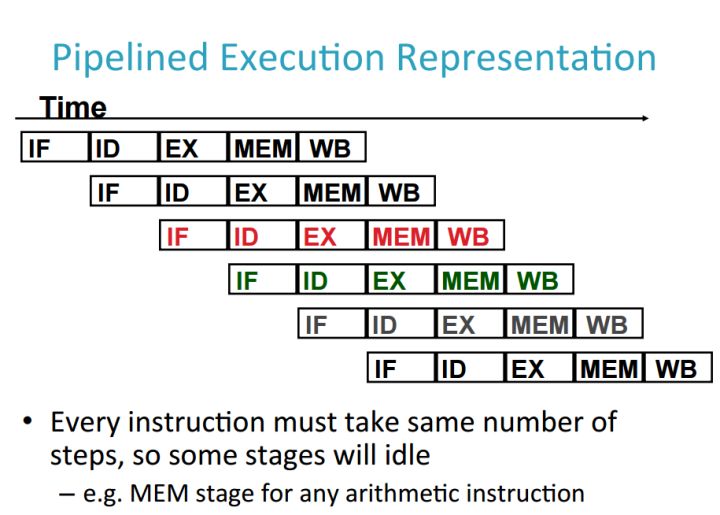

不同的 CPU 指令集架构在执行指令的过程会有所差别,以经典的 RISC(精简指令集架构)为例,存在以下步骤:

- 取指令

- 分析指令

- 执行指令

- 访问主存

- 写回寄存器

不同的步骤可能由 CPU 内部的不同部件(e.g. 指令部件、执行部件)来完成。在这样的前提下,如果 CPU 单纯的顺序执行这些步骤的话,势必会在某一时刻令一些部件空闲。

可想而知,如果 CPU 控制单元调度恰当,让不同部件可以并行工作的话,是可以提高各个部件的工作效率和计算机运算速度的,这就是流水线调度方式。

CPU 流水线(Pipeline),亦称管线,是现代计算机处理器中必不可少的部分,是指将计算机指令处理过程拆分为多个步骤,并通过多个硬件处理单元并行执行来加快指令执行速度。其具体执行过程类似工厂中的流水线,并因此得名。

流水线主要分为 2 类:

- 指令执行流水线

- 运算操作流水线(如:浮点加法运算)

超标量处理器是可以实现指令级别并行的 CPU,它通过向处理器上的其他执行单元派发指令在一个时钟周期内同时执行多条指令。超标量设计意味着处理器会在一个时钟周期发出多条指令,该技术往往都与指令流水线一起使用,流水线会将执行拆分成多个步骤,而处理器的不同部分会分别负责这些步骤的处理,例如:因为指令的获取和解码由不同的执行单元处理,所以它们可以并行执行。

除了超标量和流水线技术之外,后来还引入了乱序执行以及分支预测等更加复杂的技术,其中乱序执行也被称作动态执行,因为 CPU 执行指令时需要先将数据加载到寄存器中。

流水线的优点:

- 提高 CPU 主频:流水线将组合逻辑分割成多个小块,因为每段的关键路径变短了,所以能提高系统主频。

- 提高系统吞吐量:因为流水线让任务以类似并行方式处理,提高硬件模块的利用率,所以能提高吞吐量(Throughput)。

流水线的缺点:

- 由于流水线让许多指令被同时执行,假如分支预测错误的话整个流水线上所有的指令全部要被取消,流水线要被重新充满,就需要从存储器或者 CPU 缓存中调用指令,导致延迟时间,在这段时间里 CPU 是没有任何工作的。NetBurst 架构管线一开始有 20 级、而后增加至 31 级,放大其缺点。其后继者 Intel Core 微处理器架构就减少管线级数。

时钟周期、机器周期、指令周期和总线周期

-

时钟脉冲:指脉冲信号,是一个由 CPU 控制单元按一定电压幅度、一定时间间隔连续发出的电子脉冲信号,是计算机的基本工作脉冲,控制着计算机的工作节奏。时钟频率越高,时钟周期就越短,工作速度也就越快。

-

时钟频率(Clock Speed):指同步电路中时钟脉冲的基础频率,是单位时间(1s)内所产生的时钟脉冲的个数。时钟频率是描述周期性循环信号在单位时间内所出现的次数,标准计量单位是 Hz(赫兹)。

-

CPU 主频:即 CPU 内部工作的时钟频率,是评定 CPU 性能的重要指标,一般来说主频数值越大越好。需要注意的是,主频仅是 CPU 性能表现的一个方面,而不代表 CPU 的整体性能,CPU 的运算速度还考虑流水线的各方面的性能指标(缓存、指令集、CPU 的位数等)。

-

外频:是 CPU 外部的工作频率,是由主板提供的基准时钟频率。CPU 主频和外频的关系:主频=外频×倍频。

-

FSB 频:是连接 CPU 和主板芯片组中的北桥芯片的前端总线(Front Side Bus)上的数据传输频率。

-

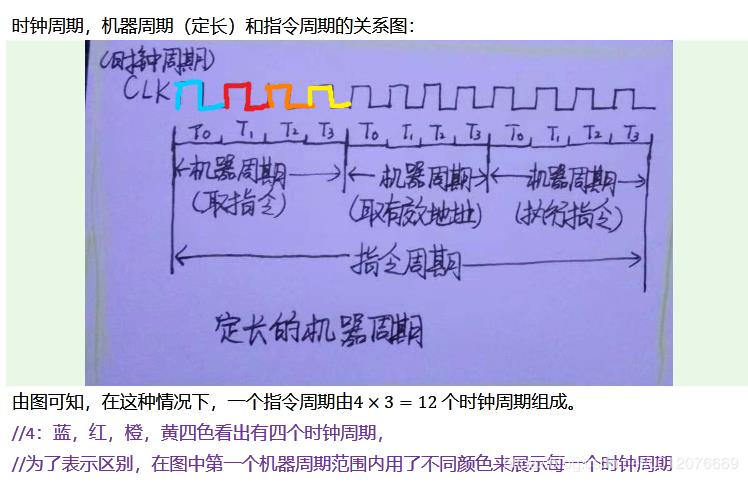

时钟周期:也称为振荡周期、P 周期或节拍脉冲,定义为时钟频率的倒数,即 (1/时钟频率)s,比如:8086/8088 系统的时钟频率为 4.77MHz,那么每个时钟周期约为 200ns。时钟周期在 CPU 的描述里也叫节拍,是 CPU 中最基本的、最小的时间单位,在一个时钟周期内,CPU 仅完成一个最基本的动作。时钟周期表示了 S/DRAM 所能运行的最高频率,更小的时钟周期就意味着更高的工作频率。

-

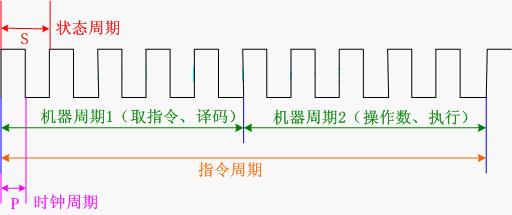

状态周期:也称为 S 周期,把时钟脉冲的周期定义为节拍(用 P 表示)。时钟脉冲经过二分频后定义为状态,即一个状态包含两个节拍,称为状态周期(用 S 表示)。

-

机器周期:在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段,每一阶段完成一项工作。例如:取指令、分析指令、执行指令、存储器读、存储器写等,此类每项工作称为一个基本操作。完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个状态周期组成。机器周期一般由 12 个时钟周期组成,也是由 6 个状态周期组成。

-

指令周期:指令周期是取出一条指令并执行这条指令的时间。一般由若干个机器周期组成,是从取指令、分析指令到执行完所需的全部时间。指令周期类型有非访内指令的指令周期、取数指令的指令周期、存数指令的指令周期、空操作指令和转移指令的指令周期。

-

总线周期:指 CPU 完成一次访问主存储器或 I/O 端口所需要的时间,一个总线周期由几个时钟周期组成。由于主存储器和 I/O 端口是挂接在总线上的,CPU 对主存储器和 I/O 接口的访问,是通过总线实现的。通常把CPU通过总线对微处理器外部(存储器或I/O接口)进行一次访问所需时间称为一个总线周期。

以上是关于计算机组成原理 — CPU — 流水线与执行周期的主要内容,如果未能解决你的问题,请参考以下文章

(计算机组成原理)第五章中央处理器-第二节:指令执行过程(取指周期间址周期执行周期和中断周期)