导纳分析基于FPGA的导纳分析仪的verilog设计

Posted fpga&matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了导纳分析基于FPGA的导纳分析仪的verilog设计相关的知识,希望对你有一定的参考价值。

1.软件版本

ISE14.7+ Modelsim SE-64 10.1c

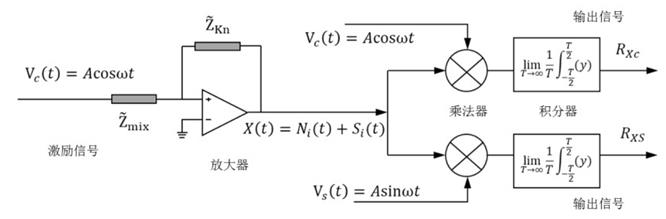

2.本算法理论知识

3.核心代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 14:51:45 08/26/2020

// Design Name:

// Module Name: mysys

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module mysys(

input i_clk,

input i_rst,

input signed[11:0]i_Vin,//将外部的DAC输入接这里

output signed[11:0]o_sin1,

output signed[11:0]o_sin2,

output signed[11:0]o_sin3,

output signed[11:0]o_sin4,

output signed[11:0]o_Vout,//接到DA输出混叠正弦信号

//乘法输出

output signed[23:0]o_rsin1,

output signed[23:0]o_rcos1,

output signed[23:0]o_rsin2,

output signed[23:0]o_rcos2,

output signed[23:0]o_rsin3,

output signed[23:0]o_rcos3,

output signed[23:0]o_rsin4,

output signed[23:0]o_rcos4,

//积分输出

output signed[15:0]o_Rxs1,

output signed[15:0]o_Rxc1,

output signed[15:0]o_Rxs2,

output signed[15:0]o_Rxc2,

output signed[15:0]o_Rxs3,

output signed[15:0]o_Rxc3,

output signed[15:0]o_Rxs4,

output signed[15:0]o_Rxc4

);

//频率配置参数

parameter address1 = 32'd400000000;//400000000/2^32*100e6;

parameter address2 = 32'd200000000;//200000000/2^32*100e6;

parameter address3 = 32'd100000000;//100000000/2^32*100e6;

parameter address4 = 32'd50000000;//50000000/2^32*100e6;

//DA输出,接到你外部的网络中

sin_4out sin_4out_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_address1(address1),

.i_address2(address2),

.i_address3(address3),

.i_address4(address4),

.o_sin1 (o_sin1),

.o_sin2 (o_sin2),

.o_sin3 (o_sin3),

.o_sin4 (o_sin4),

.Vout (o_Vout)//接到DA输出混叠正弦信号

);

//然后是AD输入

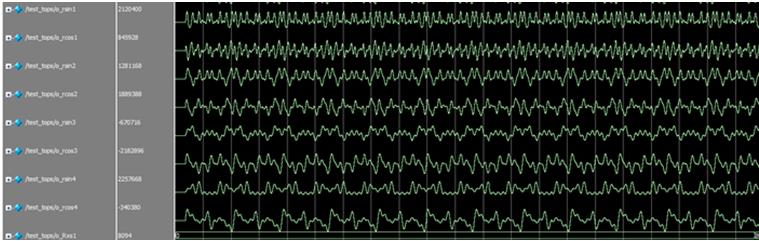

//ADC输入采样Vin后,对信号进行检波处理,乘法器将Vin与8路参考数字信号(4个频率点的正弦及余弦,FPGA内部产生)相乘并积分(积分时间可调)得到其数值。

check_tops check_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_address1(address1),

.i_address2(address2),

.i_address3(address3),

.i_address4(address4),

.i_Vin (i_Vin),

.o_rsin1 (o_rsin1),

.o_rcos1 (o_rcos1),

.o_rsin2 (o_rsin2),

.o_rcos2 (o_rcos2),

.o_rsin3 (o_rsin3),

.o_rcos3 (o_rcos3),

.o_rsin4 (o_rsin4),

.o_rcos4 (o_rcos4),

.o_Rxs1 (o_Rxs1),

.o_Rxc1 (o_Rxc1),

.o_Rxs2 (o_Rxs2),

.o_Rxc2 (o_Rxc2),

.o_Rxs3 (o_Rxs3),

.o_Rxc3 (o_Rxc3),

.o_Rxs4 (o_Rxs4),

.o_Rxc4 (o_Rxc4)

);

//8个数据进行串口设计

endmodule

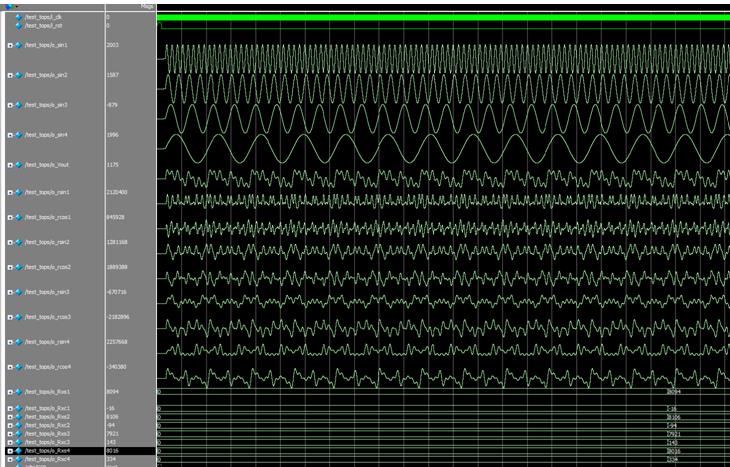

4.操作步骤与仿真结论

5.参考文献

A37-07

6.完整源码获得方式

方式1:微信或者QQ联系博主

方式2:订阅MATLAB/FPGA教程,免费获得教程案例以及任意2份完整源码

以上是关于导纳分析基于FPGA的导纳分析仪的verilog设计的主要内容,如果未能解决你的问题,请参考以下文章