漫谈快速控制原型设计(RCP)

Posted 姚家湾

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了漫谈快速控制原型设计(RCP)相关的知识,希望对你有一定的参考价值。

快速控制原型 (RCP) 是一种旨在加快控制策略开发过程的工作流程。该工作流允许您快速执行实验迭代,以识别和解决潜在问题。

通俗地讲,所谓快速原型设计是指在最终产品还没有开发之前,能够基于设计思想,数学,物理学模型,在一台通用的设备上证实算法的正确性,并且能够在实验室完成测试。

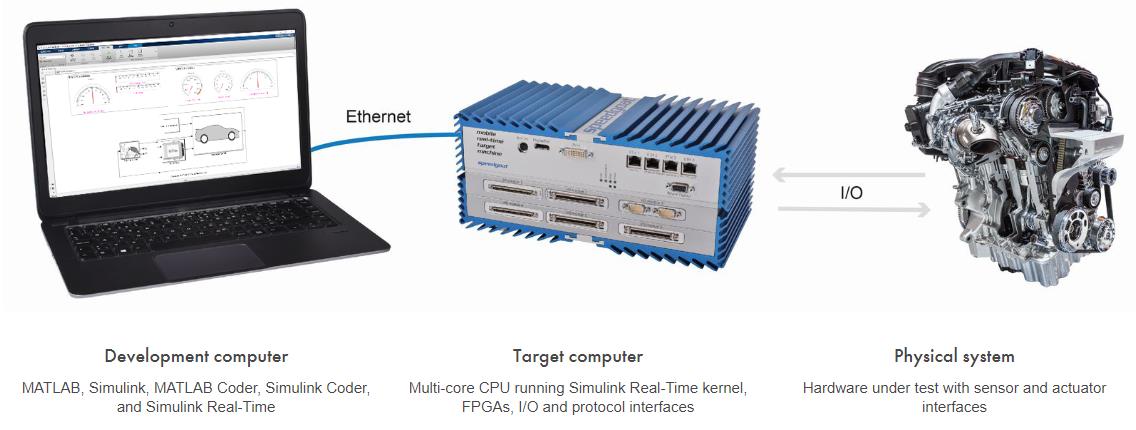

俗话说“工欲善其事 必先利其器”。实现快速原型设计需要一整套完整的工具来实现。著名的matlab/simulink 软件就是实现快速控制原型设计的主要工具之一。但是要完成物理现场的实时验证和在线仿真,需要在真实的物理设备上运行,并且通过各种IO接口与其它物理设备相连接,例如传感器,执行机构等等。

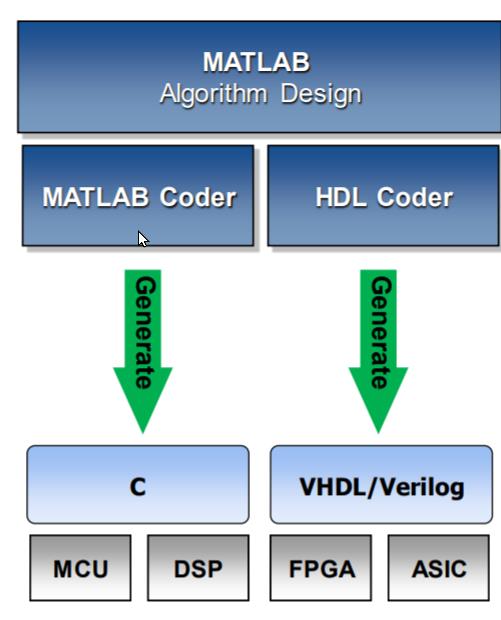

为了满足这样的需求,matlab已经具有将模型转化为代码的工具。它们可以将matlab 中的算法直接转化为C/C++ ,PLC 的ST语言,以及FPGA 的verilog/HDL 代码。然后快速原型机上的编译器或者FPGA 开发工具的支持下,转化成为可以在快速原型机上运行的代码。

本文我们就聊聊快速控制原型机。

快速原型设计硬件平台

市面上的大量开发板板级计算设备都是快速原型设计平台,比较出名的包括了ardunio,树莓PI。 它们都是大众欢迎的廉价快速原型设计的硬件平台。但是这样的平台主要面向DIY用户或者学生。并且以软件开发为主。它们的算力,实时性都无法满足高速实时控制的需求。

高性能原型设计硬件平台由一台高性能CPU和一个或者多个FPGA 芯片构成。以speedgoat 公司(Speedgoat于2007年初由MathWorks前员工成立,总部位于瑞士伯尔尼)的产品为了主要使用Intel 的X86 处理器作为主CPU,外加基于PCIe总线的高性能FPGA 插卡构建。高端产品完全就是一台工控PC机。从atom,i3 到至强处理器。speedgoat 的硬件平台与matlab 无缝衔接。因此我们可以通过研究它们了解高性能快速原型控制平台的特点。

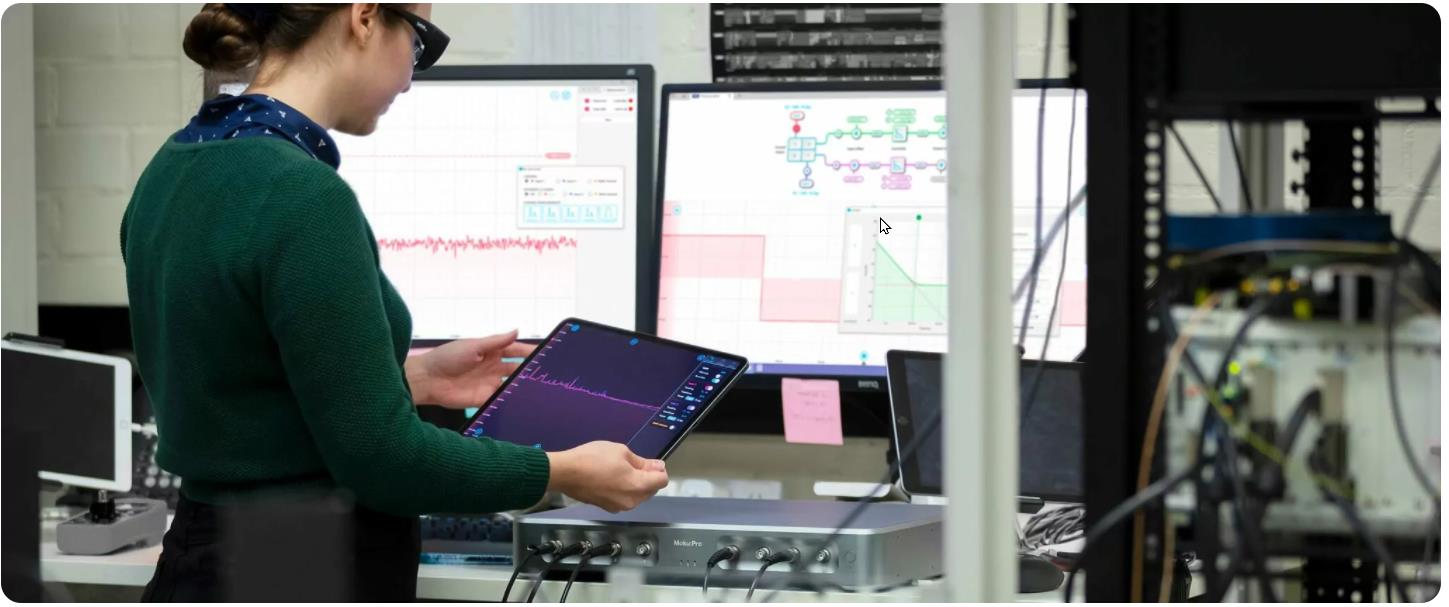

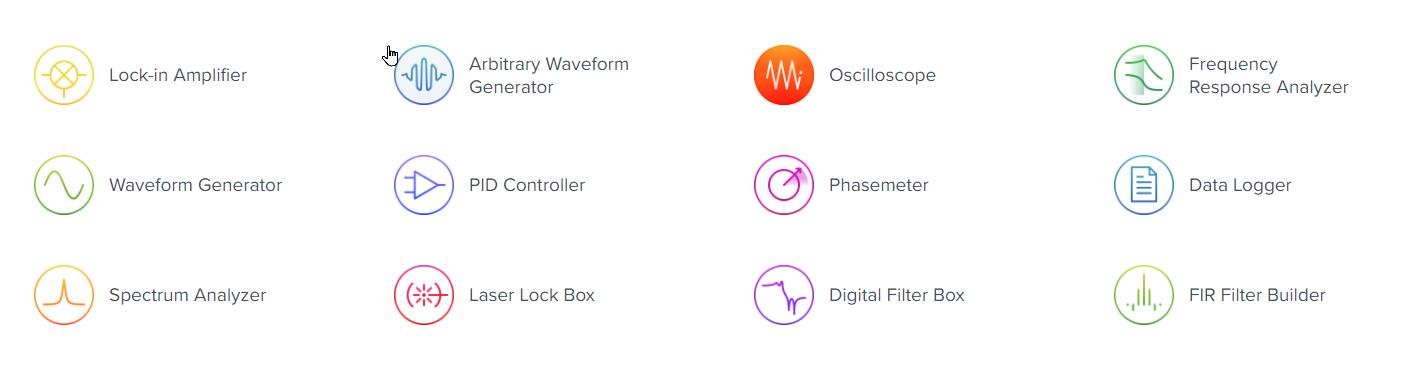

speedgoat 公司与matlab的融合非常深。普通公司没有这样的条件,于是我关注了另一家liquid Instrument 公司,他们的产品基于Xilinx公司的ZYNQ。

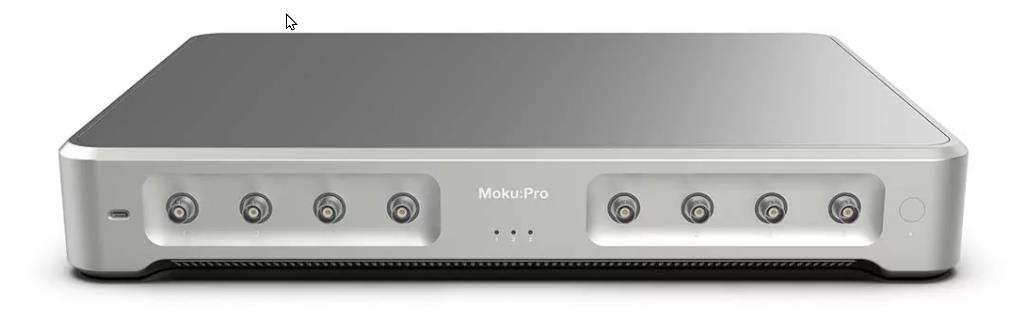

澳大利亚Liquid Instruments成立于2014年, 由澳大利亚国立大学量子科学系教授、美国物理学会研究员Daniel Shaddock建立,Shaddock教授主要研究包括激光干涉、引力波探测、空间精密光学测量等领域。目前已经完成A轮融资。被称为“孵化中的独角兽”。 其新一代产品“Moku:Pro ”兼具性能和仪器多功能性,提供高度整合的测试测量与控制一体化解决方案,为软件定义精密测试测量仪器带来了突破性的创新。AFR 高度评价 Moku:Pro 为“高精测量仪器行业的魔法盒”,有可能彻底改变全球价值 150 亿美元的测试测量行业。

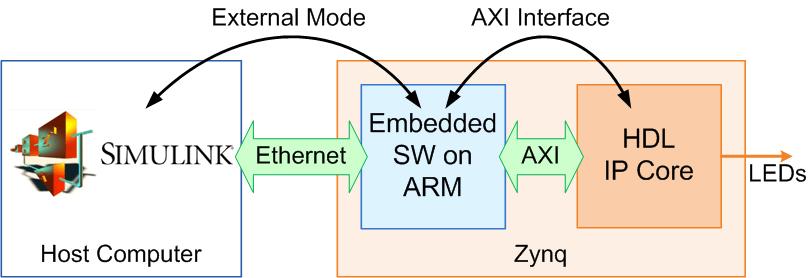

Zynq ®平台的HDL Coder™支持包支持生成可使用 Xilinx Vivado ® Design Suite 或 Xilinx ISE Design Suite 集成到 FPGA 设计中的 IP 内核。

当与用于 Xilinx Zynq 平台的Embedded Coder ®支持包结合使用时,该解决方案可用于硬件/软件工作流程,涵盖 Xilinx Zynq 器件和平台上的仿真、原型设计、验证和实施。这使得将基于模型的设计集成到您的工作流程中变得更加容易,从而实现快速的设计迭代周期,并帮助您及早检测和纠正设计和规范错误。

基于Matlab的快速原型设计平台

不断地听到基于模型设计(model based design)的概念和想法。对于非IT专业的技术专家而言,他们最擅长的基于数学和物理的概念来设计控制系统。而不希望将精力耗费在具体的软硬件设计和调试中。人们向往“少代码”和“无代码”的时代早日到来。matlab 是最普及的基于模型设计的工具。并且在与硬件融合方面取得了长足进步。

不过,开发一个基于matlab 的原型开发平台是一件具有挑战性的工作。

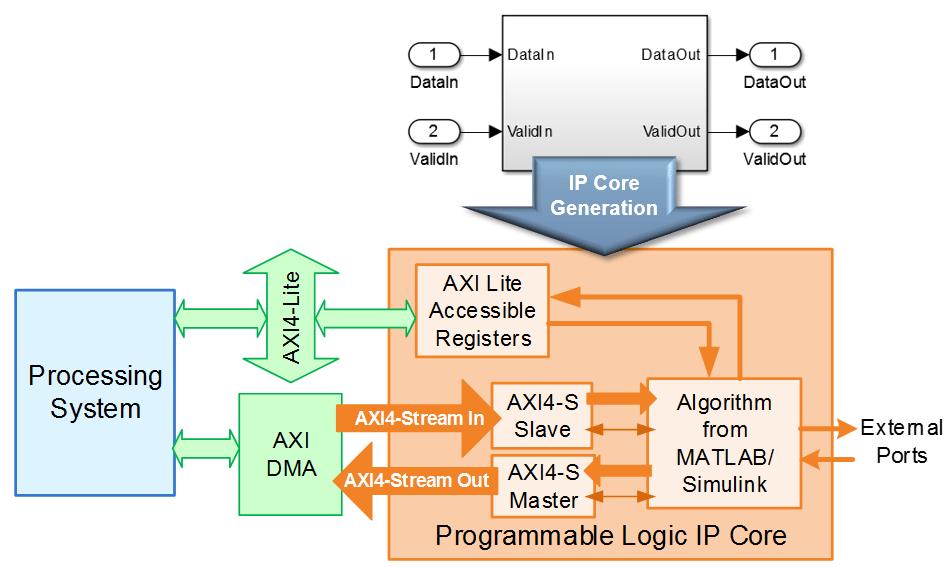

简单地从Matlab 的介绍可以看出,Matlab 支持快速原型设计的功能已经非常完善,能够将matlab 的设计产生C/C++ 代码,或者产生FPGA 的HDL 代码的IP core。目前支持XIlinx,Intel和Microsemi 三家公司的FPGA 产品。不过事情远没有想象那么简单。

1 Matlab 产生的IP 核需要结合到目标机FPGA 的设计中,完成综合与实现。这些都需要FPGA 厂商开发软件的配合。而FPGA 设计软件是非常复杂和费时间的。

2 嵌入式系统的软件如何与matlab的IP核交换数据

3 IO接口如何与IP 核的配合?

4 如何完成IP核的动态局部重构?

ZYNQ 平台的架构

动态局部分区接口

局部重构分区

用户能够根据使用和教学的需要,动态地将IP 核导入到FPGA 的动态局部分区中。在liquid Instruments 介绍,他们在FPGA 中定义了5 个分区。其中4 个用于不同仪器的IP核。第5 个分区用于系统基础功能。通过导入不同的IP核,配合相应的软件可以实现多种仪器。这也是liquid instrument 受到欢迎的原因。

第三方实现方案

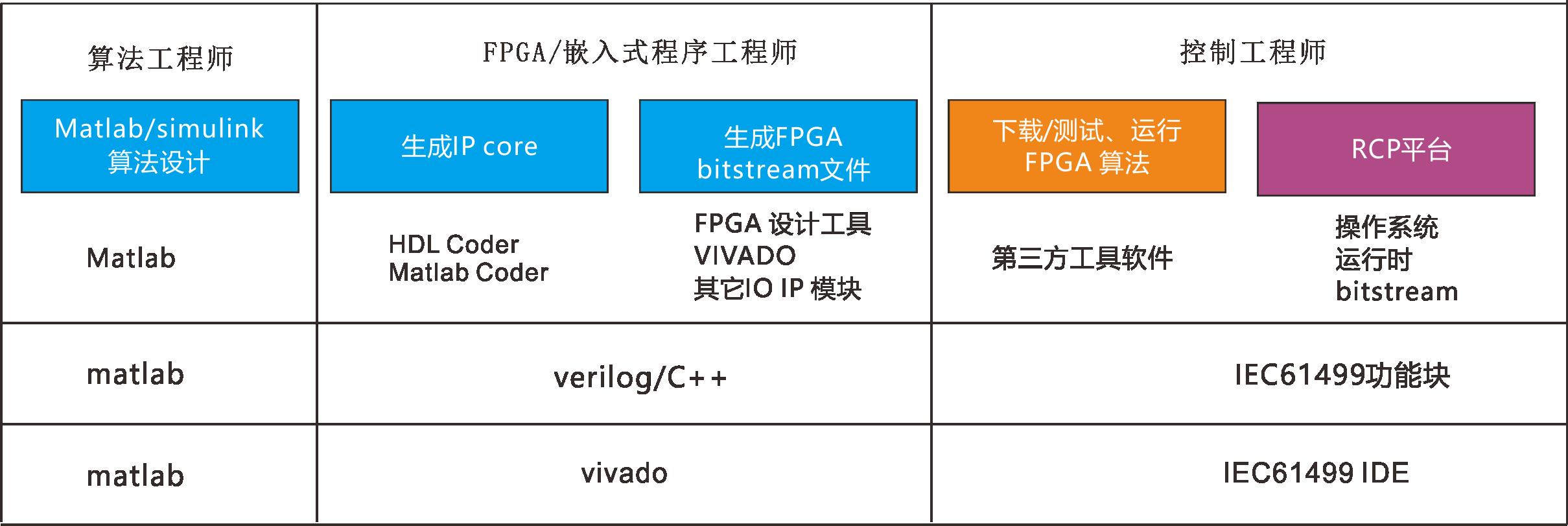

完全按照speedgoat 的方式开发快速原型设计平台是困难的。而且如果由非计算机和FPAG 技术背景的工业控制领域的工程师来实现matlab/simulink 算法到快速原型平台的转换也是十分困难的。笔者认为要相对分工。

1由专业技术团队将matlab/simulink 的算法转换成为FPGA 的IP core 。并进行验证和测试。

2 由嵌入式软件工程师将IP核分装到程序库,或者IEC61499gong功能块中

3 控制工程师通过程序库或者IEC61499 功能块 构建应用程序。

云编译技术

使用vivado 完成FPGA 的综合,实现非常复杂,并且对本地电脑的性能要求很高。对于学生和非FPAG 专业人员而言是比较困难的。因此,简化操作流程,降低使用的难度至关重要。Liquid INstruments 公司采取了云编译的方式实现在普通电脑,甚至ipad 上完成FPGA 的综合和部署。本人觉得是一个好主意。

所谓“云编译(cloud compile)”,就是将vivado 部署在云端。由云端提供高性能的服务器运行vivado 。用户能够分时使用云端编译。网络上有一些介绍。

另一方面,HDL coder 产生IP核,云端编译主要是将IP核综合之后,插入到设备的某一个局部重构分区中,这只是vivado 的一部分工作。使用者完全没有必要使用vivado 提供的那样复杂核难以理解的使用界面(GUI)。而采纳更为简洁的GUI。例如liquid instruments 的界面为:

这就需要研发一个简洁的开发环境,可以使用nodeJS,或者go这样高效率的程序设计语言来实现。用户基于浏览器使用这个软件。该软件的主要功能包括:

1 上传matlab HDL Coder 产生的IP 核的HDL 文件。

2 通过vivado 的tcl 命令,能够实现对vivado 编译的批处理。

3 选择不同的IP核构建相应的bitstream和嵌入式软件。

4 将嵌入式软件和bitstream部署到设备运行。

Tcl(工具命令语言)是用于以编程方式控制 Vivado® 的标准语言。实际上,在图形用户界面中执行的任何操作都有相应的 Tcl 命令,显示在 Vivado 控制台中。

结束语

网络上不断有人向我提起开发能够直接运行matlab 生成的算法的问题,作为一个闲人,对这个问题做了一些了解。发现这并非易事。对研发这类产品的技术路线提出了一些看法。仅供参考。有兴趣的读者可以共同讨论。

以上是关于漫谈快速控制原型设计(RCP)的主要内容,如果未能解决你的问题,请参考以下文章