ZYNQ 应用笔记PS/PL接口

Posted 姚家湾

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ZYNQ 应用笔记PS/PL接口相关的知识,希望对你有一定的参考价值。

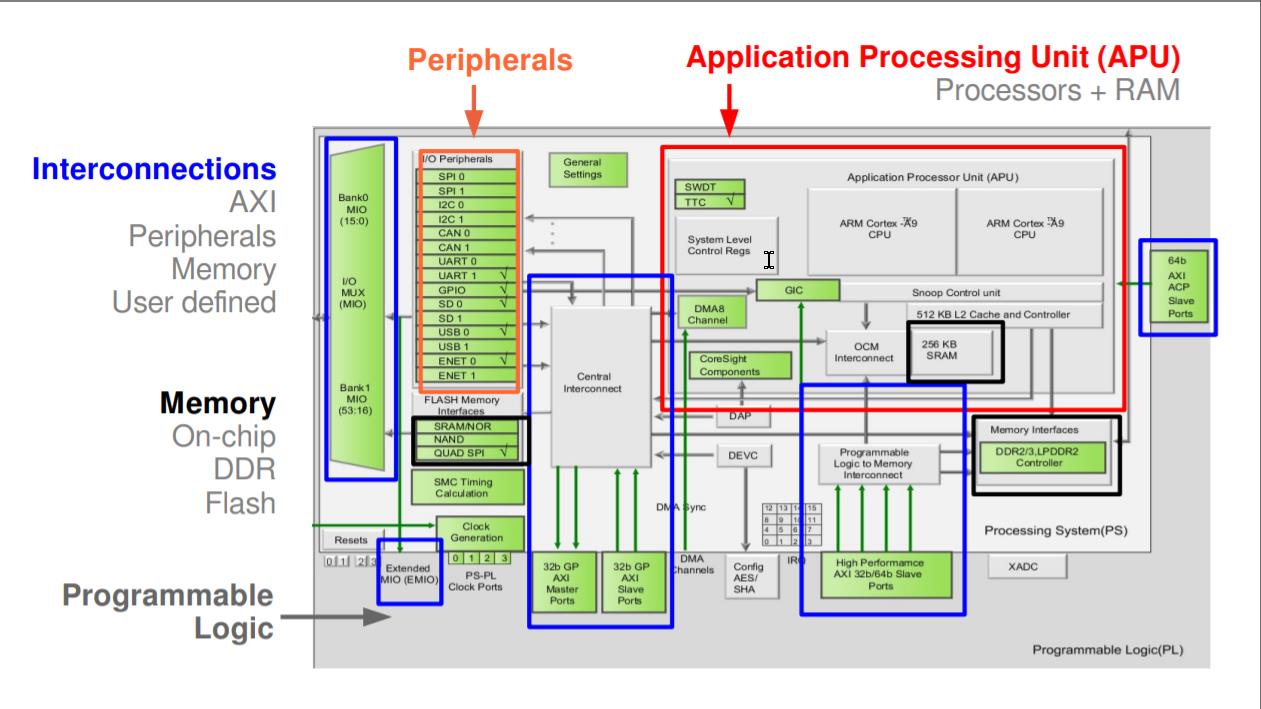

相比传统的SOC 芯片,Xilinx 公司ZYNQ 的最大优势在于,除了内嵌的硬核ARM 处理器自带的IO接口之外,能够利用FPGA 自由地构建符合应用需求的IO外设和基于verilog/HDL的算法。这给嵌入式系统设计带来的巨大的灵活性。

ZYNQ 分成所谓的Processing System (PS) 和 Programmable Logic (PL)两个部分。PS就是所谓的硬核,而PL是FPGA。

在本博文中,我们对PL 构建IO 外设有一个基本的了解,下一篇博文讨论动态部分配置逻辑。

ZYNQ 架构

MIO

, PS 和外部接口之间的通信主要是通过复用的输入 / 输出(Multiplexed Input/ Output,MIO)实现的,它提供了可以做灵活配置的 54 个引脚,这表明外部设备和 引脚之间的映射是可以按需定义。MIO 类似于普通SOC 芯片的IO引脚。

也可以通过扩展 MIO (Extended MIO,EMIO)来实现,EMIO 并不是 PS 和外部连接之间的直接通路,而是通过共用了 PL 的 I/O 资源来实现。

MIO 连接的IO外设包括

- SPI(x2)

- I2C(x2)

- CAN(x2)

- UART(x2)

- GPIO(32x4)

- SD(x2)

- USB(x2)

- GigE(x2)

由于ZYNQ 具有PL ,可以开发更多基于PL 逻辑的IP。所以,看上去ZYNQ 的IO外设类型并不多,其实要比传统SOC 丰富的多。用户可以自行设计需要的IO控制器。

AXI接口

该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)协议中的一部分,2003年在AMBA3.0 第一次包含AXI的第一版,2010年的AMBA4.0 包含的AXI4.它是一种面向高性能、高带宽、低延迟的片内总线。在ZYNQ 中,AXI 主要用于PS和PL之间的总线。

AXI4 接口包括三种类型的接口:

AXI4 用于高性能存储器映射方式的需要

AXI4-Lite 用于轻量级存储器映射通信,比如访问控制和状态寄存器。

AXI4-Stream 用于高速数据流数据。

下面以AXI GPIO 核为例,它是基于AXI-lite 的一个GPIO 的软核。可以在vivado 中导入和配置。。

AXI 外设的IP

在vivado 开发工具中,Xilinx 提供了一些基于AXI 的IO 外设IP 。它们包括:

AXI 高速外设

AXI 1G/2.5G Ethernet Subsystem

AXI EthernetLite

USB2

AXI 低速外设

AXI CAN

AXI GPIO

AXI Quad SPI

AXI Timer

AXI UART 16550

CANFD

I2CBus Master Controller

可以在设计中直接调用这些IP。

实例1-LED

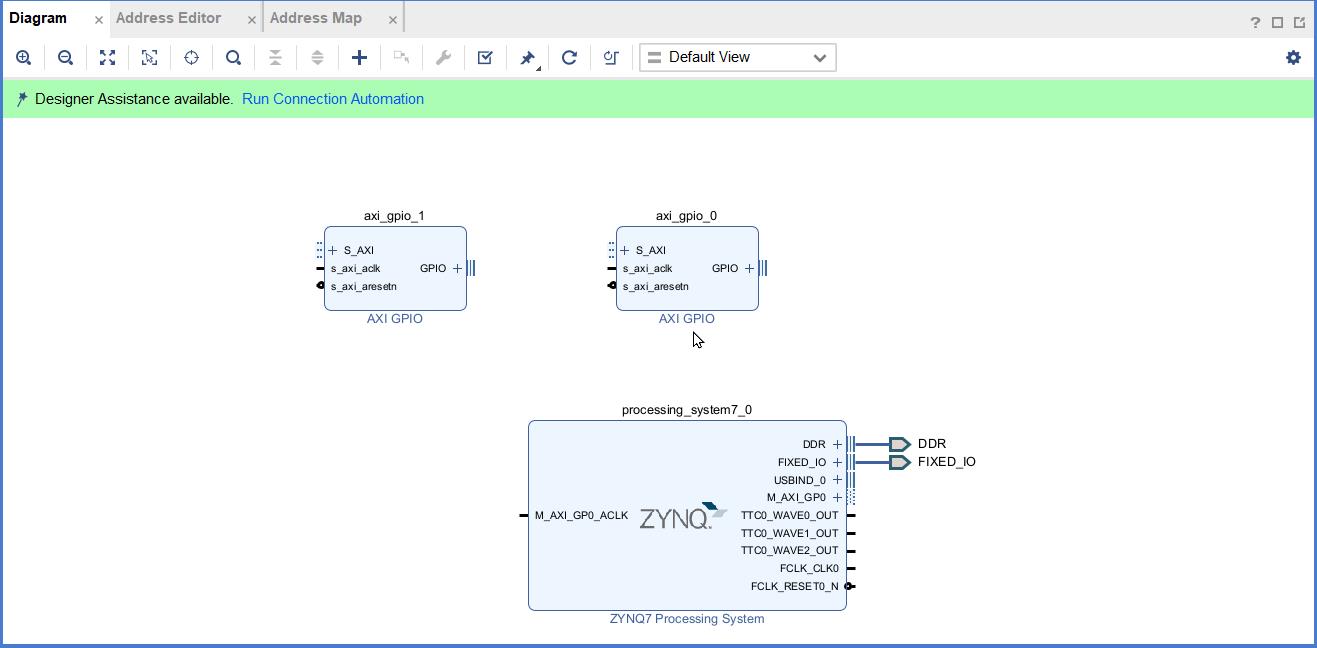

1 新建一个vivado 项目 project1

左边栏->IP Itegrator->Create Block Design

- 放置 ZYNQ Processing Sysytem

- 放置 AXI GPIO 名称为axi_gpio_0

- 放置 AXI GPIO 名称为axi_gpio_1

双击AXI GPIO 块,配置GPIO 的管脚。

点击自动连接

vivado 会自动添加两个块(AXI priph,res_pa7_0_50M),并且连线。

点击Tools->Validate.设计就基本完成了。

实例2 创建带AXI slave接口的IP—PS控制PL侧的LED

在这个实例中,我们讨论如何构建自己的IP。

参考CSDN 一博文

Vivado创建带AXI slave接口的IP—PS控制PL侧的LED

分为两步:

1 构建LED_IP

2 引用LED_IP

构建

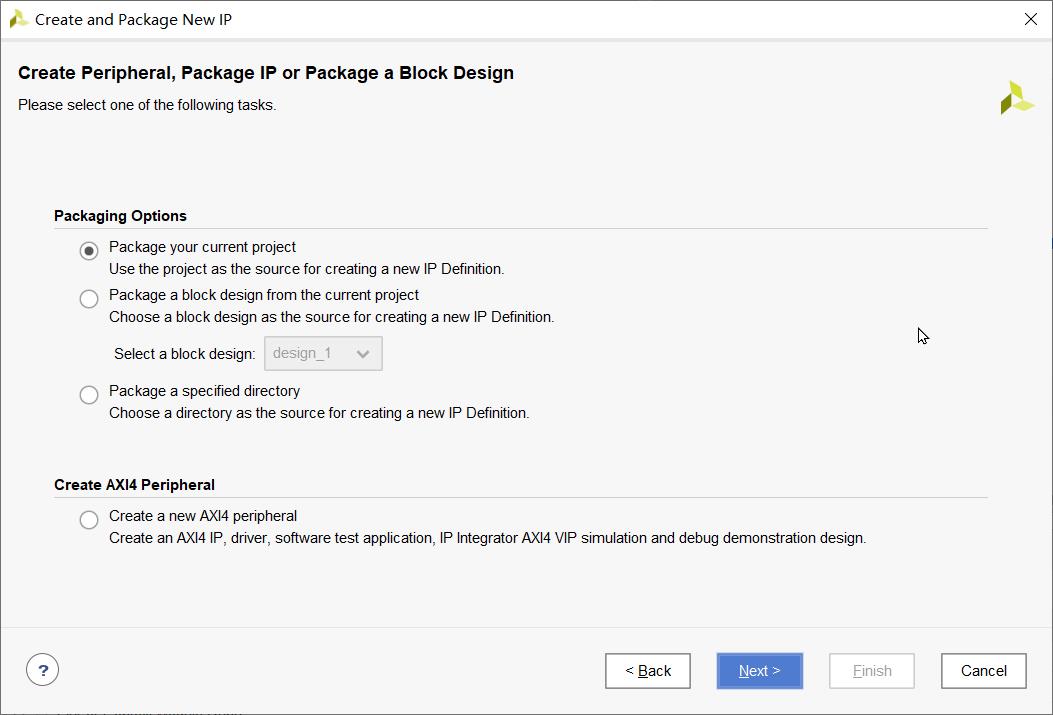

新建一个项目,然后选择Tools -> Create and Package NEW IP

选择Create AXI4 Peripheral->Next

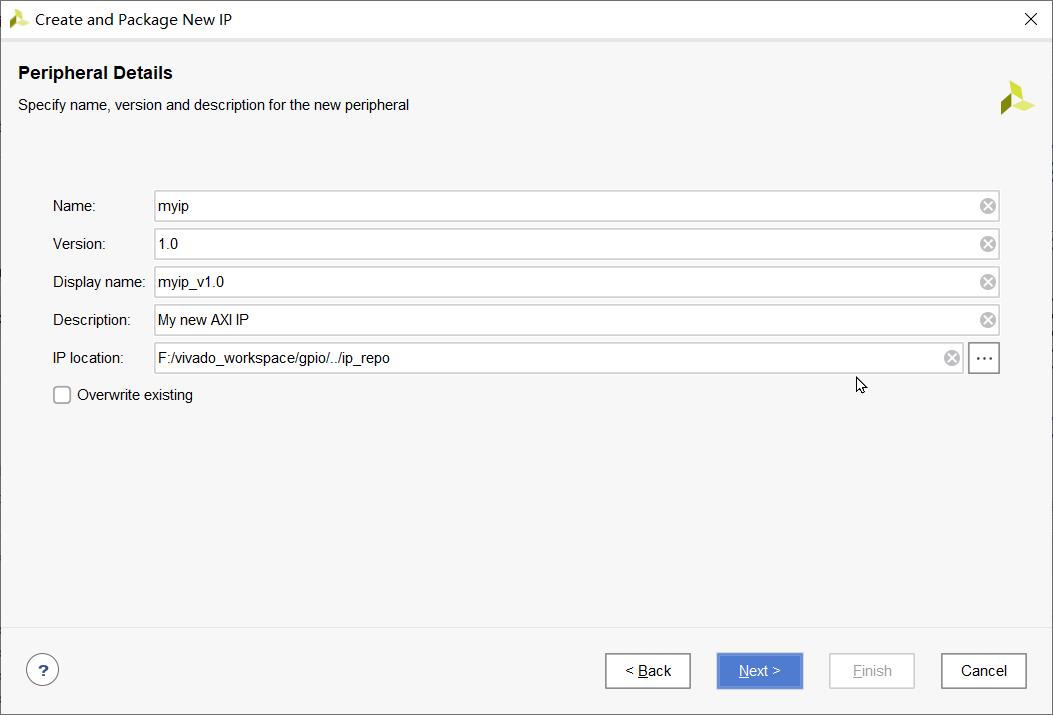

在这里,我们设计一个LED_IP ,点击Next

在这里我们选择的下一步是编辑IP(Edit IP)

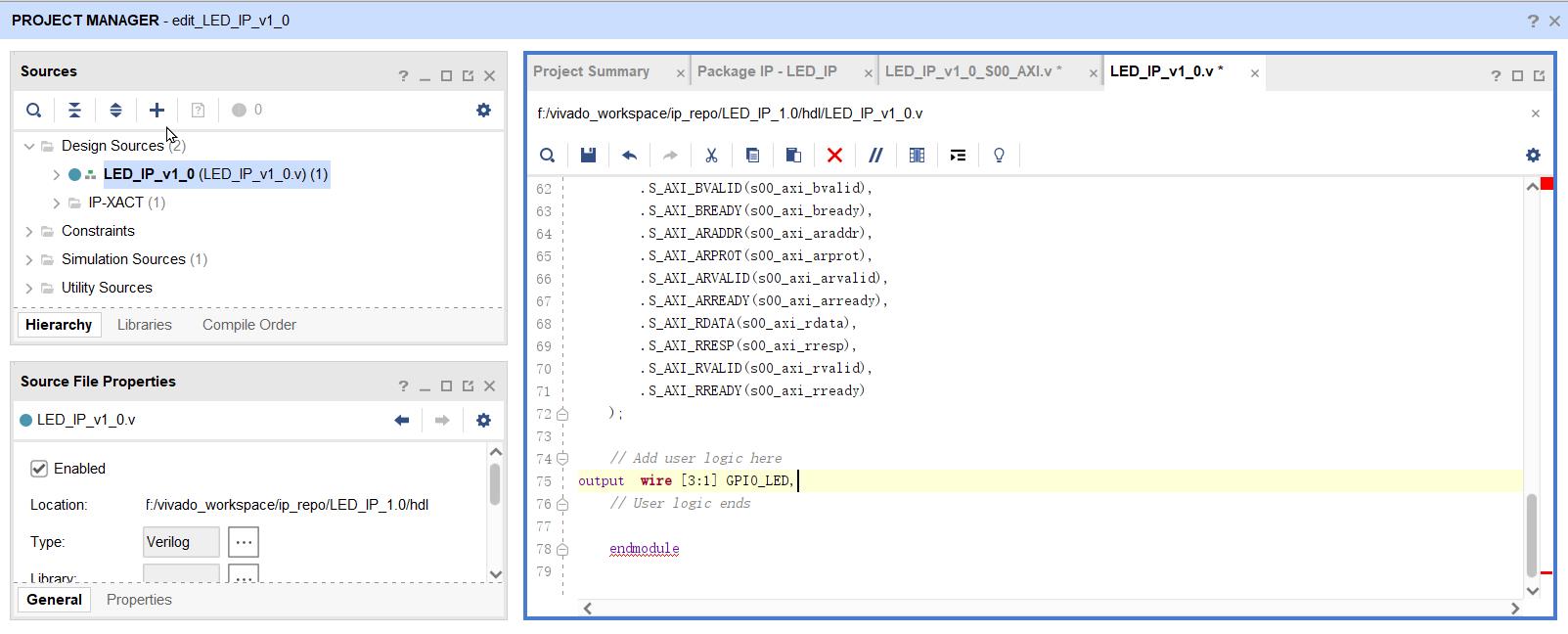

下一步,按照上面提到的参考博文的提示,编辑LED_IP 下的两个verilog 文件的内容。

LED_IP_v1_0_S00.v

LED_IP_v1.0.v

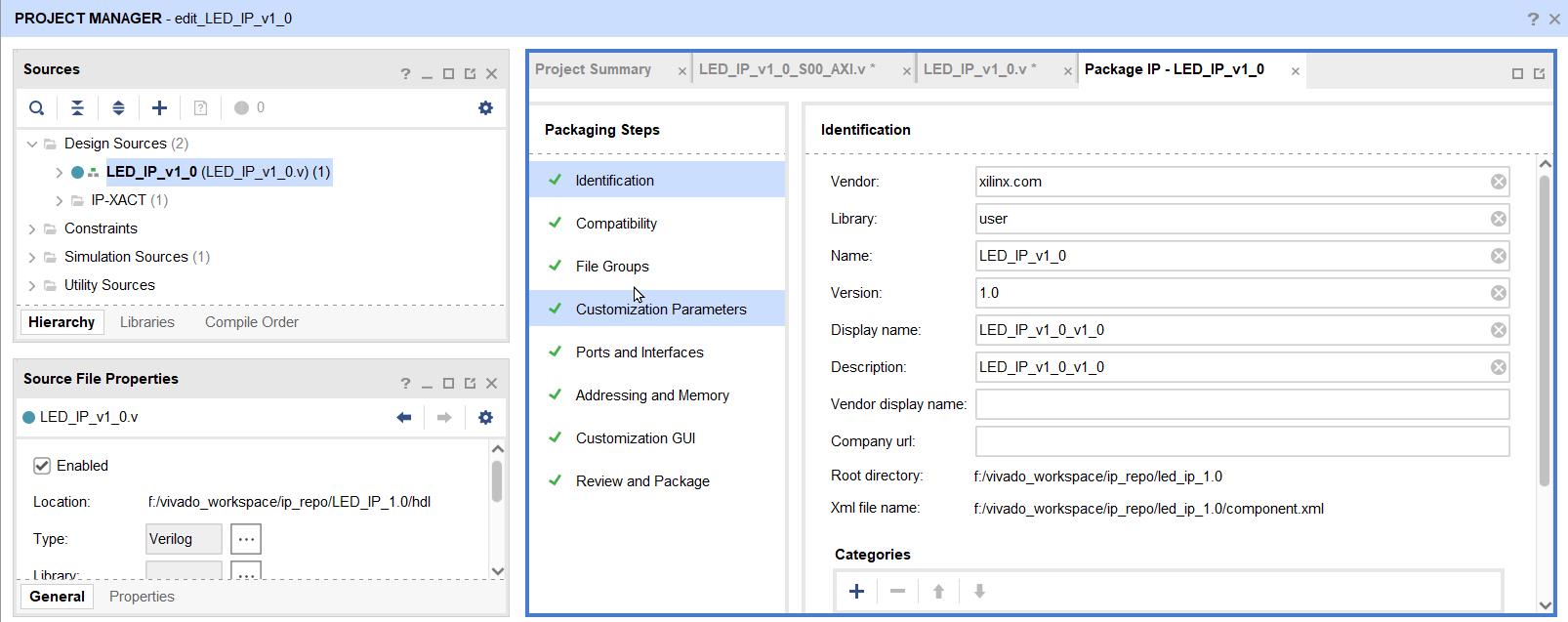

重新封装IP

选择 Tools -> Creat and Pakage New IP,单击Next -> 选择Package your current project,单击Next,路径选择原来IP所在的位置,OverWrite原来的文件 -> Finish.见到下图。

到此为止,LED_IP 的IP 就算设计完成了,可以在后续的设计中应用这个IP。如果要测试这个IP ,需要新建一个项目。导入这个IP

结束语

简单地了解一些ZYNQ 的各项功能,并没有详细地介绍细节。希望从总体上对于ZYNQ 有一个了解。

本人学习ZYNQ PL 逻辑设计的主要目的是为了探讨在工业领域的可编程控制器中如何利用FPGA 功能来构建确定性,高实时性计算。能否使用硬件设计语言verilog/HDL来实现PLC 的梯形图和IEC61499 功能块。更进一步地,如何使用matlab/Simulink 来设计高速数字处理算法和AI 算法。使IEC61499 能够应用于实验室和工业现场的数字化测量,硬件在环测试以及控制。只是初步地向前迈进了一步就发现。

这是一个相对困难的课题。涉及的内容太多了。至少需要搞清楚下面几个基本的问题。

1 使用已有的IP核来构建基于AXI 接口的IO接口电路

2 设计自己的IP

3 设计动态部分配置的PL逻辑

4 将matlab 的算法导入到一个可动态部分配置的块中。

在此基础上,要进一步研究

- 将PLC 梯形图转换成verilog语言

- 利用FPGA 构建一个硬件PLC 运行时

- 利用FPGA 构建IEC61499 硬件功能块

这些都是令人兴奋的课题,感觉失去这样一个有趣课题,是非常可惜的。有兴趣的读者,我们可以一起探讨。

以上是关于ZYNQ 应用笔记PS/PL接口的主要内容,如果未能解决你的问题,请参考以下文章