计算机组成与设计---硬件/软件接口---大容量和高速度:开发存储器层次结构

Posted FANCY PANDA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机组成与设计---硬件/软件接口---大容量和高速度:开发存储器层次结构相关的知识,希望对你有一定的参考价值。

5.1存储器技术

静态存储器 (SRAM)

- 存取数据时间0.5ns – 2.5ns,

- 价格: $2000 – $5000 per GB

动态存储器 (DRAM)

- 存取数据时间50ns – 70ns,

- 价格: $20 – $75 per GB

磁盘:

- 存取数据时间 5ms – 20ms,

- 价格:$0.20 – $2 per GB

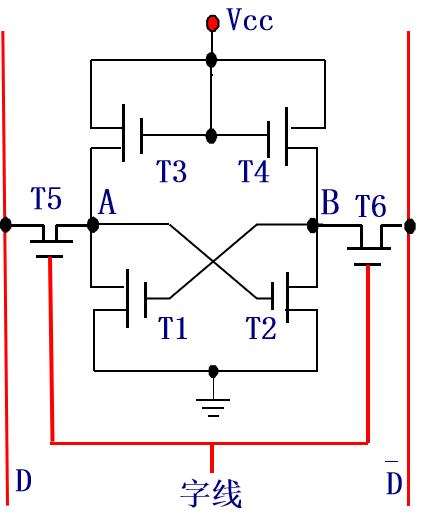

5.1.1 SRAM技术

基本存储元

- 由6只MOS管组成

- 具有两个稳态

- 1—— T1止, A高,T2通,B低,T1止。

- 0——T2止,B高,T1通,A低,T2止。

- 在加电情况下,数据才能保存/读/写,掉电后信息全部丢失。

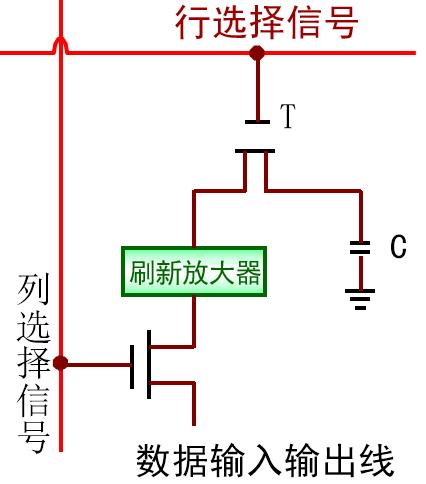

5.1.2 DRAM技术

单管动态存储元

- 电容器C有电荷,为逻辑“l”,无电荷时,为逻辑“0”

- 由于电容器存在漏电,导致电荷流失,信息也就丢失

- 解决的办法是刷新,即每隔一定时间(一般2ms)就要刷新一次

5.1.3 磁表面存储器

硬盘控制器HDC(适配卡)、连接电缆

硬盘驱动器

- 盘片:多个盘片构成盘片组,每个盘片两个记录面

- 磁头

-

- 固定磁头:每磁道一个磁头,速度快,集成度低

-

- 活动磁头:每个盘面一个磁头,需径向寻道

主轴电机:盘片旋转驱动机构

- 磁头定位机构:寻道和磁头归位

- 步进电机定位和音圈电机定位

- 读写电路和控制逻辑

5.1.4存储系统分级结构

三级存储系统

- Cache——主存层次

- 主存——外存层次

局部性原理:在任意时刻,程序访问的只是地址空间相对较小的一部分内容

- 时间局部性

- 空间局部性

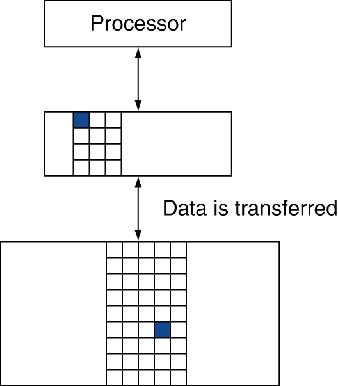

存储器层次结构

- 块(也称行): 存储信息的最小单元,可以是多个字

- 如果处理器需要的数据存放在高层存储器的某个块中

-

- 命中: 在高层存储器中找到目标数据

-

- 命中率: 命中次数/全部访问次数

- 如果数据不在高层存储器

-

- 缺失:从低层存储器拷贝包含所需数据的块

-

- 缺失代价:将相应块从低层存储器替换到高层存储器所需要的时间

-

- 缺失率: 缺失次数/全部访问次数= 1 – 命中率

然后再从高层存储器访问数据

- 缺失率: 缺失次数/全部访问次数= 1 – 命中率

利用局部性原理

- 可以把存储器组织成层次结构

- 所有的数据都存储在磁盘上

- 把最近被访问的(或即将被)的数据从磁盘拷贝到容量较小的DRAM存储器

-

- 主存储器

- 把最近经常被(即将被)访问的数据拷贝到更小的SRAM存储器(cache)

-

- Cache隶属于CPU

5.2 cache的基本原理

Cache—memory:在存储层次中最靠近CPU

主存与Cache的地址映射

- 全相联映射

- 直接映射

- 组相联映射

5.2.1 cache缺失处理

- Cache命中时,CPU继续使用该数据,就像什么都有发生过

- Cache缺失时

-

- 引起CPU流水线阻塞

-

- 从下一个存储层次读取数据块

-

- 如果指令cache缺失

-

- 重新取指,此时该指令在cache中

-

- 如果数据cache缺失

-

- 完成数据操作,此时数据在cahche中

5.2.2写操作处理

写直达

- 数据写命中,可以只更新Cache中的块

-

- 但这样会导致Cache和主存不一致

- 写直达:将数据同时写入主存

- 但这样会使写时间更长

- e.g., 没有缺失情况,基本的CPI = 1, 10% 的指令是store指令,每次写到内存需要100个时钟周期,

·有效的 CPI = 1 + 0.1×100 = 11 - 解决方法:写缓冲

-

- 数据被放入写缓冲等待写存储器操作完成,之后释放写缓冲

-

- CPU立即继续执行其他指令

-

- 仅当缓冲区满时产生写阻塞

写回法

- 另一种方式:当数据写命中,仅仅更新cache中的块

-

- 记录每一块是否被“修改”过

- 仅当一个修改过的块被替换时

-

- 才写回到较低层的存储结构中(主存)

-

- 当缺失替换一个被修改的块时,可先写入写缓冲区,同时从主存读出所需要的数据块,允许先读缓冲区中将替换的块,然后再将数据写回主存。

写分配

- cache写缺失时

- 写直达的策略

-

- 缺失时写分配:重新从内存取数据块

-

- 相似的写策略:写不分配,不从内存取块

-

- 既然程序在读一个块之前通常要写整个块 (e.g., 初始化)

- 写回法的策略

-

- 通常要把这个块从内存取回到cache

5.3可信存储器层次

5.3.1 失效的定义

1)服务实现:交付的服务与需求相符

2)服务中断:交付的服务与需求不符

失效导致状态1到状态2的转换,而由状态2转换到状态1的过程称为恢复

失效可以是永久性的,也可以是间歇性的

间歇性失效更加复杂一些,因为当一个系统因间歇性失效在两个状态间摇摆时,诊断将会非常困难。而永久性失效的诊断要容易许多。

这种定义将引出两个术语:可靠性和可用性

可靠性是一个系统或模块能够持续提供用户需求的服务的度量,即从开始使用到失效的时间间隔

平均无故障时间(mean time to failure,MTTF):是一个可靠性度量方法

年失效率(annual failure rate,AFR):它是指在给定MTTF 情况下,在一年内预期的器件失效比例

提高系统的MTTF:

1)故障避免技术(fault avoidance):通过合理构建系统来避免故障的出现

2)故障容忍技术(fault tolerance):采用冗余措施,当发生故障时,通过冗余措施保证系充仍然正常工作

3)故障预报技术(fault forecasting):对故障进行预测,从而允许在器件失效前进行替换

5.4虚拟存储器

虚拟存储系统:建立在内存——外存层次上的,需要辅助硬软件的支持,将内存与外存空间统一编址形成一个庞大的存储空间,用户可在这个虚拟的庞大空间里编程,而不必考虑实际内存的大小

虚拟地址(逻辑地址):用户编程时使用的地址,在程序真正执行时,在辅助软硬件支持下,虚拟地址将映射为内存的物理地址。

实际地址(物理地址):内存的实际的地址编号

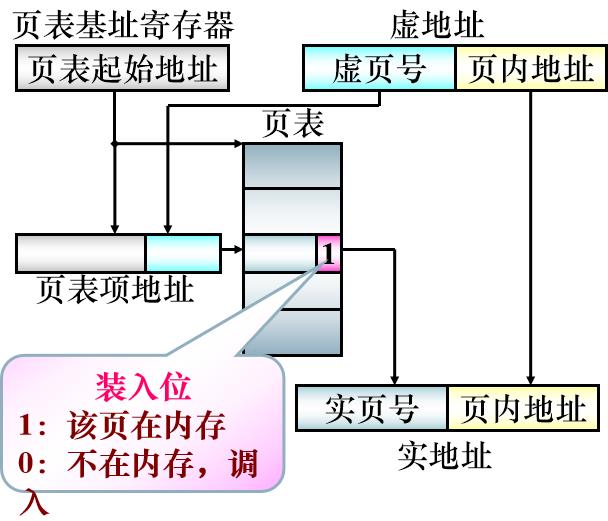

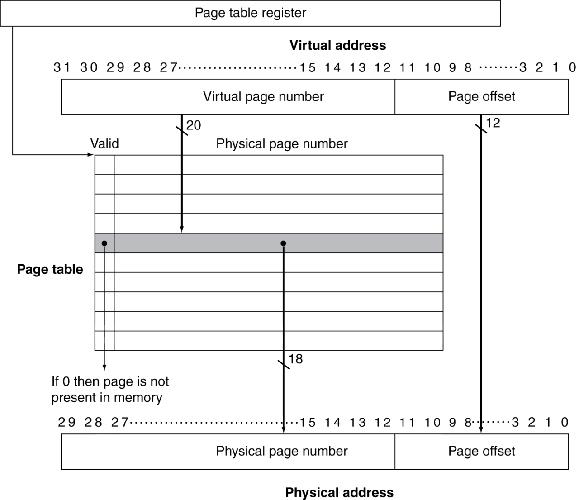

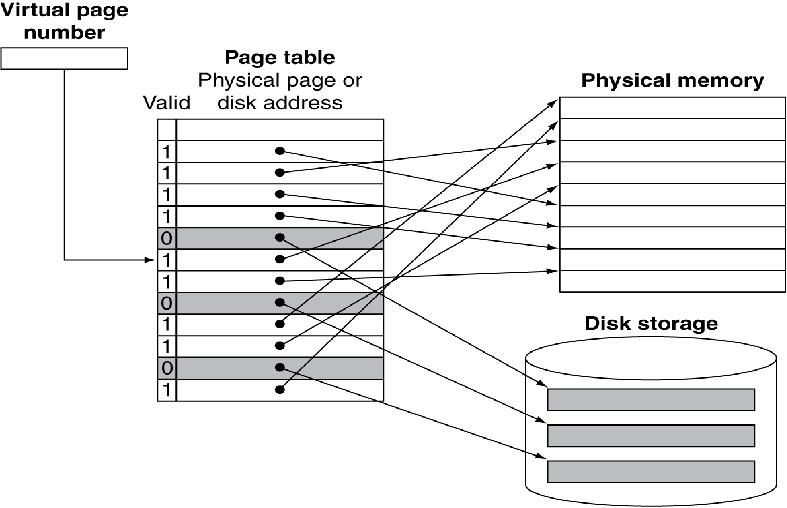

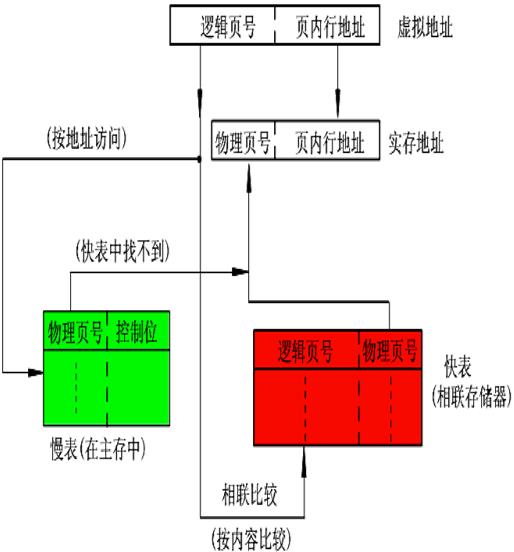

5.4.1页的存放和查找

内存空间和虚存空间都划分成若干个大小相等 的页

设置地址变换机构——页表

- 页表由多个页表项构成。

- 每个页表项包含实页号、装入位等

5.4.2缺页故障

缺页时,页必须从磁盘被取回来

-

花费数百万个时钟周期

-

由OS处理

尽量减小缺页率 -

全相联替换算法

-

更先进灵活的替换算法

页表 -

存储位置信息

-

- 页表项的数组,可以通过虚页号检索

-

- CPU中页表寄存器存放页表在内存的首地址

-

如果页在存储器中

-

- 页表项PTE存储物理页号

-

- 加上其他的状态位(引用位ref,修改dirty,…)

-

如果页不在内存

-

- PTE可以到磁盘交换空间查找

使用页表进行地址转换

页表将虚页映射到主存或磁盘

5.4.3关于写

为减少缺页故障率,最好选择LRU替换算法

- 访问页面时,PTE中的引用位(也称使用位)置位

- OS定期将引用位清零

- 当引用位=0时,表明该页最近没被使用

磁盘写操作需要花费数百万个时钟周期 - 可以写页,但不是独立的位置

- 写直达是不可行的

- 使用写回机制

- 当页中任何字被写时,都将PTE中的重写位(Dirty bit)置位

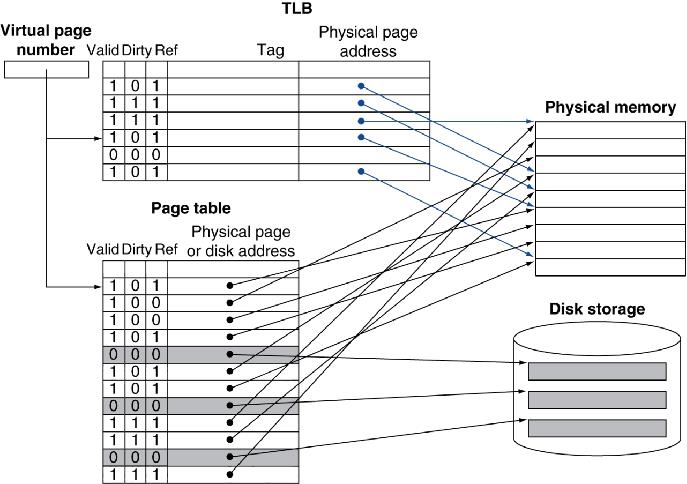

5.5.4加快地址转换:TLB.

地址转换可能需要额外的内存访问

- 一次访问页表项,获取物理地址

- 另一次访问存储器读取数据

但页表访问具有很好的局部性 - 因此可以使用CPU内部的页表项(快速Cache)

- 称之为旁路转换缓冲 (TLB),即快表。

- TLB典型值: 16–512项, 0.5–1 时钟周期的命中时间, 10–100 时钟周期的缺失代价, 0.01%–1% 缺失率

- 缺失可以被硬件或软件处理

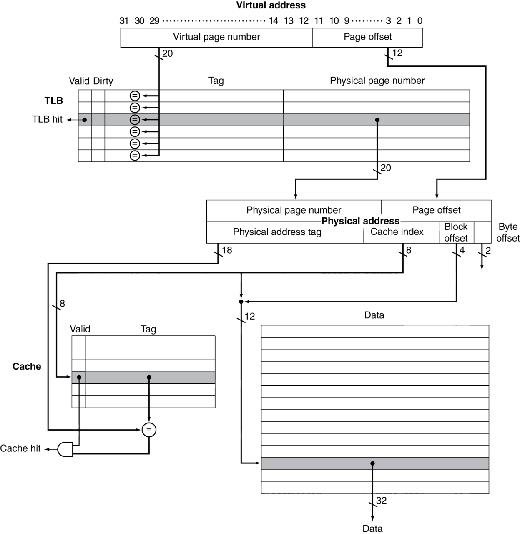

5.4.5集成虚拟存储器、TLB.和cache

如果 cache 标记使用了物理地址

- 需在cache查找前转换

替换方法:使用虚地址标记

- 别名将增加复杂性

-

- 不同的虚拟地址共享主存的同一页

5.4.6虚拟存储器中的保护

- 多个进程可以共享他们的虚地址空间

-

- 但需要保护不被破坏

-

- 需要操作系统协助

- 硬件支持操作系统保护

-

- 特权管理模式 (也称核模式,管态)

-

- 特权指令

-

- 页表和其他状态信息只能在管理模式访问

-

- 系统调用异常处理程序 (e.g., syscall in MIPS)

存储器的层次结构

- 结构中所有的存储层次具有相同访问原则

-

- 基于cache的概念

- 在层次结构的每一级别

-

- 块位置

-

- 查找块

-

- 访问缺失的替换算法

-

- 写策略

块位置

由相联性决定

- 直接映射 (1路组相联)

-

- 只有一种选择

- n路组相联

-

- 在一组中有n个选择

- 全相联

-

- 任意位置

高相联度能降低缺失率

- 增加了复杂度、开销和访问时间

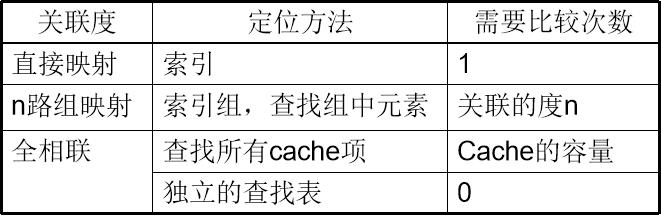

查找块

- 硬件caches

-

- 通过减少比较次数来降低开销

- 虚拟存储器

-

- 独立查找表使得全相联成为可能

-

- 有益于降低缺失率

访问缺失的替换算法

- 在缺失时选择要替换的项

-

- 最近最少使用算法 Least recently used (LRU)

-

- 复杂度高,硬件开销大,适用于高关联度

- 随机法

-

- 性能接近LRU

- 虚拟存储器

-

- 需要硬件支持的近似LRU算法

写策略

-

写直达

-

- 同时更新顶层和底层的块

-

- 替换方法简单,但需要写缓冲区

-

写回法

-

- 仅更新顶层的块

-

- 当块被替换时更新低一层的块

-

- 需要保存更多的状态

-

虚拟存储器

-

- 由于磁盘的写延迟较长,仅写回法适用

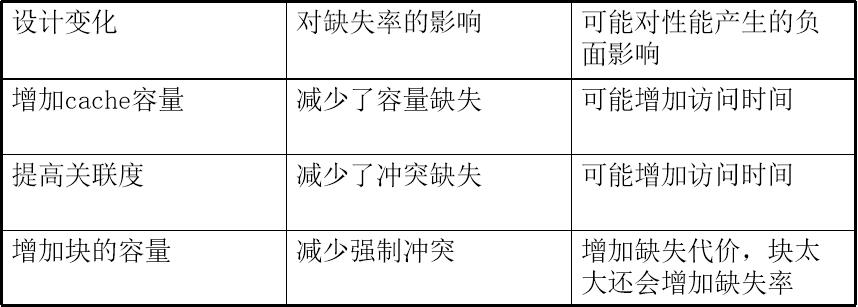

缺失类型

- 强制缺失 (也称冷启动缺失)

-

- 第一次访问块产生的缺失

- 容量缺失

-

- 由于cache的容量有限

-

- 一个刚替换出的块随后又被访问而调入

- 冲突缺失 (也叫碰撞缺失)

-

- 在非全相联的cache中发生

-

- 由于竞争组中的一个项而产生

-

- 在相同容量的全相联cache中将不会发生

- 在相同容量的全相联cache中将不会发生

5.4.7处理TLB缺失和缺页

TLB 缺失

- 如果页在主存储器

-

- 将页表的转换信息装载到PTE,然后重新访问

-

- 可以由硬件处理

-

- 可以从较为繁杂的页表中得到复杂的信息

-

- 或者用软件处理

-

- 产生一个特殊的异常,用优化的处理程序来处理。

- 如果页不在内存储器(缺页)

-

- 操作系统处理程序从磁盘上读取该页并更新页表

-

- 然后重新启动被中断的指令

TLB 缺失处理

- TLB 缺失指要访问的页

-

- 在页表中,但不在TLB的页表项中

-

- 不在页表中

- 在目标寄存器被重写前,必须知道TLB缺失

-

- 产生异常

- 处理程序从主存页表中拷贝信息填到TLB中

-

- 然后重启指令

-

- 如果访问的页不在主存,将发生页缺失

页式虚拟存储器

- 页表的改进——快表

快速小容量的存储器

保存当前最常用的页表项

是慢表的副本 - 页表虚拟存储的特点

页大小相等,地址变换简单

存在页零头

页的划分不具有逻辑性,程序处理复杂

缺页处理

- 用缺失页的虚地址查页表,找到页表项

- 在磁盘上定位页

- 选择要替换的页

-

- 如果被重写过,先写回磁盘

- 把页读到内存并更新页表

- 使进程又成为可运行状态

-

- 从故障指令处重新开始

计算机组成与设计—硬件/软件接口—计算机概要与技术

计算机组成与设计—硬件/软件接口—指令: 计算机的语言

计算机组成与设计—硬件/软件接口—计算机的算术运算

计算机组成与设计—硬件/软件接口—处理器

存储器之主存–Cache–辅存大全

以上是关于计算机组成与设计---硬件/软件接口---大容量和高速度:开发存储器层次结构的主要内容,如果未能解决你的问题,请参考以下文章