数字电路制作一个加减计数器

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路制作一个加减计数器相关的知识,希望对你有一定的参考价值。

我想用数字电路制作一个可以设定上限的加减计数器,电路图中要用到74LS192芯片,请哪位牛人能发一个详细电路图到我的邮箱star19860710@163.com

必有重写,先谢过了

要有两个触发脉冲器,一个加触发脉冲,一个减触发脉冲。功能能实现,可设定上下限。下限是0,到达下限是自动关闭减触发脉冲器,上线设定100以内,到达上限是关闭加触脉冲发器

----思路是这样的,用555做时钟信号发生器,通过选择开关(加或减计数)把CP脉冲加到计数器,计数器置数时,先将置数开关合上,再通过BCD拨码开关置数,置数完成后将置数开关复位.计数器的输出要通过七段译码器送到数码管显示,这样你可以看到现在的计数状态,同时还要将计数器的输出信号送到比较器与所设的上限数值进行比较,将比较的结果再通过继电器输出,同时还将结果送到脉冲信号发生器,可控制计数脉冲的启停.最大设定值是99,最小0.

----你可以先自己查下芯片资料,然后设计一下试试,到时候再交流一下,我把图纸传给你.你最好动手做一下,这样能提高你的动手能力. 参考技术A 计数器和计算器是完全不同的两个概念;

简单说:

数字电路中的计数器是对脉冲信号进行计数,或从某一个设定值开始进行加(减)一计数,

并且是以二进制形式表示;

而一般的便携式计算器,功能就比计数器强大得多了,可以做加减乘除等等运算,通常是以十进制形式显示(也可以显示为其他制式),显然这些都需要人工参与操作的;

数字电路实验(05)二进制计数器设计

数字电路实验(05)二进制计数器设计

一.实验要求

1.1.实验目的

- 认识二进制同步计数器的定义、工作状态及信号波形;

- 熟悉基于JK触发器实现二进制同步计数器的构成规则。

1.2.实验器材

- VCC

- Ground

- 脉冲电压源

- 上升沿触发JK触发器

- 2输入与门

- 四输入七段数码管

- 四通道示波器

1.3.实验原理

计数模值M和触发器级数k的关系:M=2k。

加法计数器的构成规律:

J0=K0=1

Ji=Ki=Q0•Q1•…. •Qi-1 i=1、2……(k-1)

减法计数器的构成规律:

J0=K0=1

Ji=Ki=Q0’•Q1’•…. •Qi-1’ i=1、2……(k-1)

1.4.实验内容、要求及过程

实验要求:

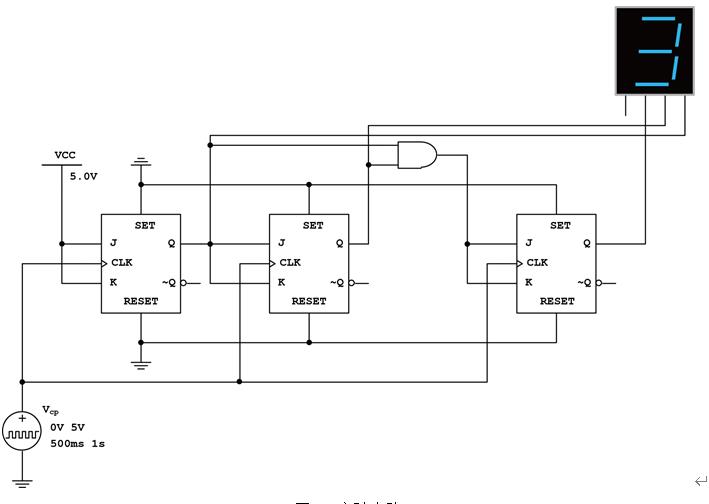

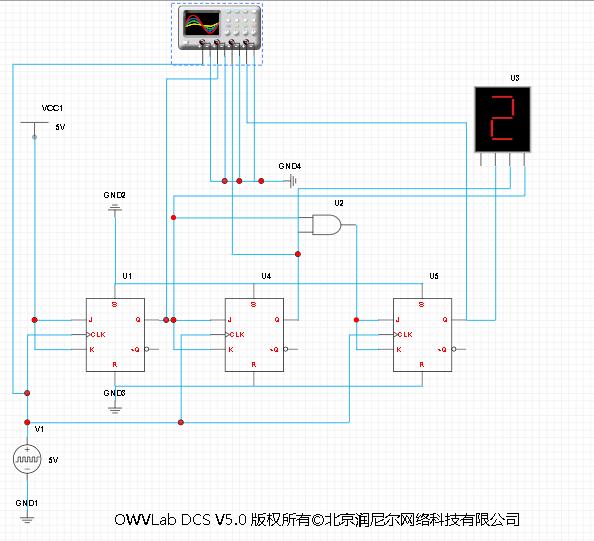

构建图1电路。时钟clk为0~5V,周期1s,高电平时长500ms。

用四通道示波器观察时钟clk及各级触发器输出的Q0、Q1、Q2信号。根据观察,在图2中画出Q0、Q1、Q2的波形(与clk信号的边沿对应好,从Q2Q1Q0=000的状态开始),并观察数码管的显示情况。

二.实验图

三.实验报告内容

- 由JK触发器构成的二进制计数器有着哪些特点?

计数模值M,触发器级数k:M=2^k

- 搭建电路完成实验,补充完整图2,说明数码管的显示情况;

数码管从0至7循环显示,仿真后观看数码管即可,点击示波器看到图2波形

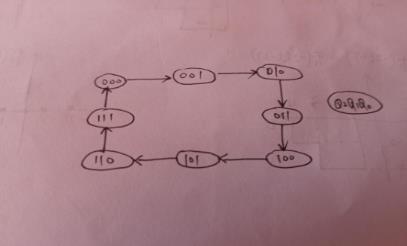

- 画出图1电路的状态转移图;

- 如果要构成二进制减法计数器(模8),在图1电路的基础上要做哪些改动?

二进制减法计数器(模8):J1=K1=Q0’,J2=K2=Q0’Q1’

以上是关于数字电路制作一个加减计数器的主要内容,如果未能解决你的问题,请参考以下文章