Verilog循环语句

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog循环语句相关的知识,希望对你有一定的参考价值。

参考技术A在Verilog HDL中存在着四种类型的循环语句,用来控制执行语句的执行次数。其语法和用途与C语言很类似

forever语句的格式如下:

forever循环语句常用于产生周期性的波形,用来作为仿真测试信号。它与always语句不同处在于不能独立写在程序中,而必须写在initial块中。forever循环的应用示例如下:

repeat语句的格式如下:

在repeat语句中,其表达式通常为常量表达式。如果循环计数表达式的值不确定,即为x或z时,那么循环次数按0处理。

下面的例子中使用repeat循环语句及加法和移位操作来实现一个乘法器。

while语句的格式如下:

while循环执行过程赋值语句直到制定的条件为假。如果条件表达式在开始不为真(包括假、x以及z),那么过程语句将永远不会被执行。

下面举一个while语句的例子,该例子用while循环语句对rega这个8位二进制数中值为1的位进行计数。

更完整点的写法:

for语句的一般形式为:

它的执行过程如下:

for语句最简单的应用形式是很易理解的,其形式如下:

for循环语句实际上相当于采用while循环语句建立以下的循环结构:

这样对于需要8条语句才能完成的一个循环控制,for循环语句只需两条即可。

下面分别举两个使用for循环语句的例子。例1用for语句来初始化memory。例2则用for循环语句来实现前面用repeat语句实现的乘法器。

[例1]:

[例2]:

在for语句中,循环变量增值表达式可以不必是一般的常规加法或减法表达式。下面是对rega这个8位二进制数中值为1的位进行计数的另一种方法。见下例:

其他参考资料: 关于Verilog 中的for语句的探讨

Verilog-2001更新了generate循环,使用方法参考:

RTL基本知识:缺失分号的后果

在使用Verilog进行设计过程中,经常会遇到某些条件判断语句中的分支没有执行,有些for循环仅执行一次的情况,特别是在过程性赋值语句中。其中很大一部分是因为错误使用了“;”导致的。因为Verilog源自C语言,根据其语言特性,“;”在Verilog中本身是一条单独的空语句,只是岂不进行任何具体操作而已,但是这样的特点造成了“;”可以出现在设计的很多地方,顺利的通过编译甚至仿真,引起不容易察觉的错误。本文将针对这种情况探讨其中原因,并以示例说明。

1 条件判断

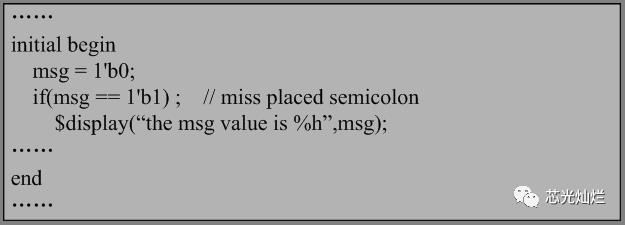

在条件判断语句中,如果将“;”放置在条件判断语句之后,那么有可能导致不期望的结果,如下例期望条件为真时输出对应的消息:

上例仿真后,虽然msg条件不成立,但是其后的显示语句还是被执行了,与预期要求不符。主要原因是条件判断后紧跟的“;”,那么当该条件成立时,执行的是条件判断后的“;”对应的空语句。而$display此时已经不是条件判断语句为真时对应的语句,所以导致显示结果在条件为假时显示,与期望结果不一致。

2 循环控制

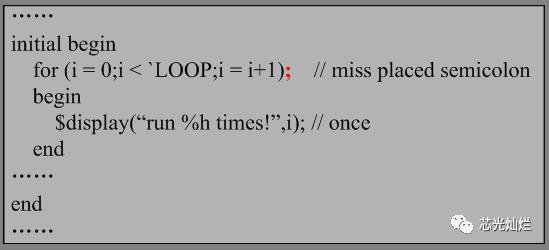

在循环控制语句中,如果将“;”放置在循环控制条件判断语句后,那么可能会导致不期望的结果,如下例期望条件成立时多次输出对应的消息:

上例仿真后,发现显示的消息仅出现了一次,与期望出现多次不相符。主要原因是for循环后紧跟";",提前结束了for循环,即每当for循环执行一次其后的“;”都会执行一次,不会按照期望的执行后续的“begin-end”中的语句。从而导致了仿真时期望的消息仅仅输出一次的现象。

3 解决方法

Verilog中的";"特点主要源自C语言,因为C语言中认为这样的“;”语法是正确的,是一条空语句。为了避免类似情况在其他语句中出现,可以通过以下方法防范:

如果确需执行类型空语句,使用“begin-end”结构,即将空语句置于“begin-end”中;

必须理解Verilog中相关语句的语法,不要错误使用相关的操作符;

以上是关于Verilog循环语句的主要内容,如果未能解决你的问题,请参考以下文章