CPU基本结构和运行原理

Posted JavaEdge.

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CPU基本结构和运行原理相关的知识,希望对你有一定的参考价值。

1 CPU的基本结构

1.1 CPU是一个计算系统的核心

Control Unit,负责控制。如指令计数器,指令跳转。

Logic Unit,负责计算。如加减,比较大小等。

1.2 南北桥芯片将CPU与外设连接

北桥:CPU和内存、显卡等部件进行数据交换的唯一桥梁,即CPU想和其他任何部分通信,须经过北桥。北桥芯片中通常集成的还有内存控制器等,控制与内存的通信。现在的主板上已经看不到北桥,它的功能已被集成到CPU当中。

南桥:主要负责I/O设备之间的通信,CPU要想访问外设必须经过南桥芯片。

总线:传输数据用,分为地址总线、数据总线。以内存为例,地址总线传输要访问的内存地址,数据总线传输读写的数据。有些总线地址和数据是分离的,有些是同一根总线分时利用。

FSB总线:前端总线(Front Side Bus),CPU和北桥之间的桥梁,CPU和北桥传递的所有数据必须经过FSB总线,FSB总线的频率直接影响到CPU访问内存的速度。

ISA总线:最早出现的标准总线,传输速度低,早期的低速外设会采用ISA总线进行连接,如声卡。

PCI总线:一种高性能局部总线,构成了CPU和外设之间的高速通道。显卡一般都是用的PCI插槽,PCI总线传输速度快,能很好让显卡和CPU进行数据交换。

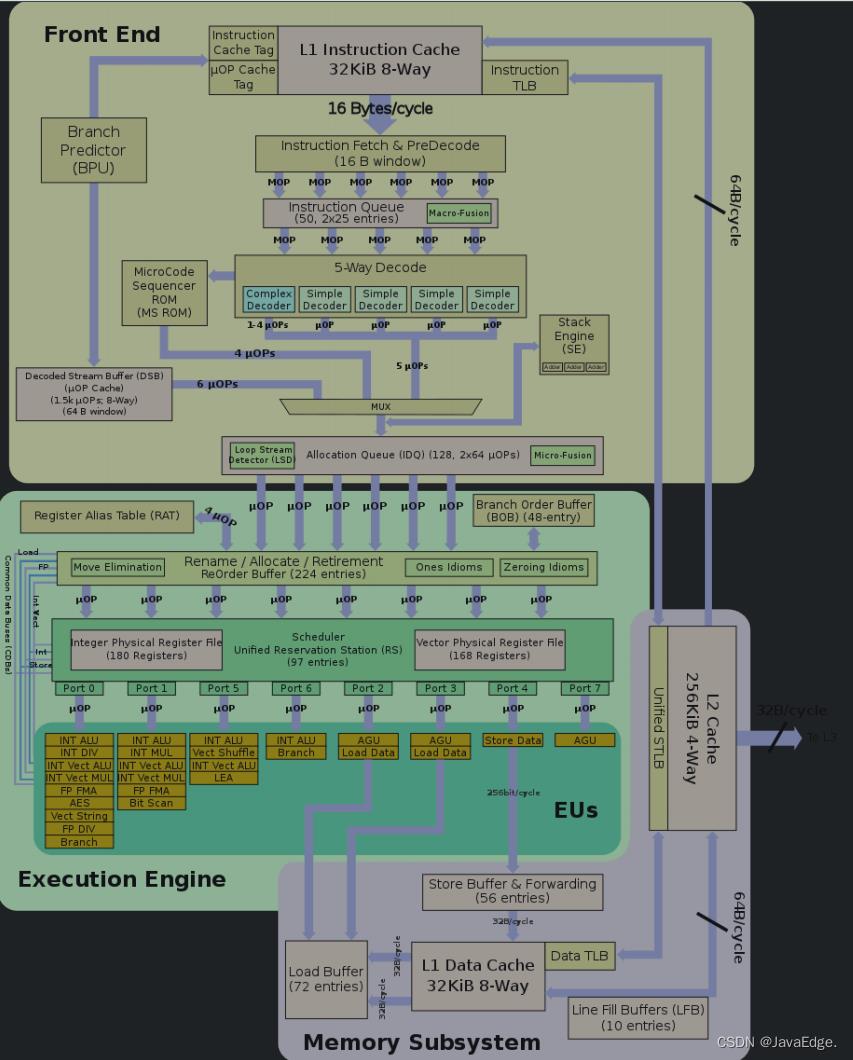

1.3 CPU的执行流程

典型CPU包含以下5个执行流程:

- 取指,从内存中取出指令

- 译码,识别指令的类型,计算指令长度,从指令中解析参数

- 执行,将数据送给计算单元或者控制单元进行具体计算和跳转

- 访存,有些指令可能需要从内存加载数据

- 写回,有些指令对寄存器或者内存状态有影响,将结果写入这些受影响的寄存器或者内存。

2 电路基础

2.1 组合电路基本原理

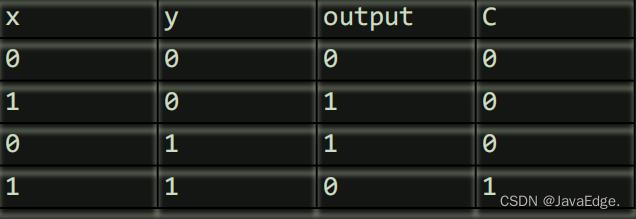

加法器真值表:

output = x xor y

C = x and y

只有当两个输入都为高电平时,输出才为高电平

至少有一个输入为高电平时,输出为高电平 输出与输入相反

2.2 时序电路基本原理

D触发器可保存数据,为了保证触发器的输出Q是正确的值,一定要让D信号稳定后,才在时钟的上升沿打入触发器。

单核主频有极限,多核成为主流:

3 汇编语言和寄存器

X86常用寄存器

16个通用寄存器:RAX, RBX, RCX, RDX, RSI, RDI, RSP, RBP,R8, R9, R10, R11, R12, R13, R14, R15。

程序计数器:RIP

状态寄存器:EFLAGS

段寄存器:CS, DS, ES, FS, GS

RAX:调用程序时,用于存储返回值。

RCX:在字符串处理指令中,常用做计数器。

RSI:在字符串处理指令中,做为源操作数。

RDI: 在字符串处理指令中,常做为目标操作数。

RSP:指向当前栈帧的栈顶。

RBP:指向当前栈帧的栈基址。

RDI, RSI, R8, R9可以在调用函数时传递参数。

RIP记录当前指令地址,每次取指阶段完成以后就会指向下一条指令的地址,如果有办法修改这个寄存器的值,就可控制程序的执行。

EFLAGS记录溢出,方向,为零等状态。可用于整个CPU的状态标记。

段寄存器在现代CPU中几乎不起作用了。在8086时代是做为段基址寄存器。

3.1 汇编语言是一种低级语言

也可使用gcc -s将C语言先翻译成汇编文件。

机器码是CPU真正能看懂并逐条执行的指令,而汇编语句是给人看的。

由于汇编语句与机器码几乎一一对应,所以我们也常常对机器码和汇编这两个词不加区分。

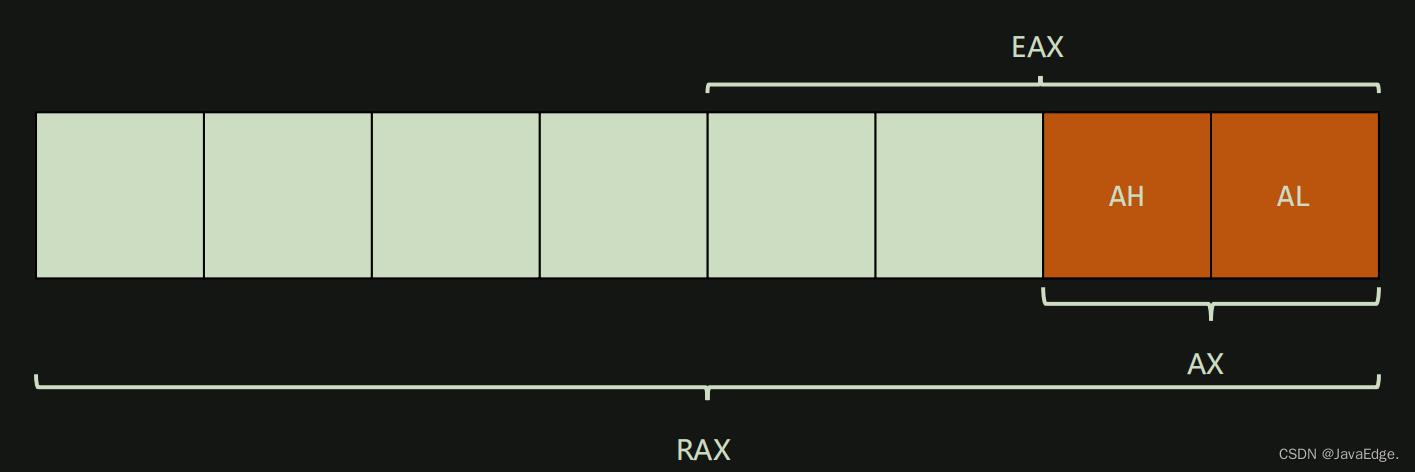

3.2 注意汇编代码中的寄存器宽度

AL和AH是1字节,也就是8位寄存器,AX是16位,EAX是32位,RAX是64位。其它通用寄存器也符合这个命名规则。

4 中断的基本原理

4.1 中断的产生

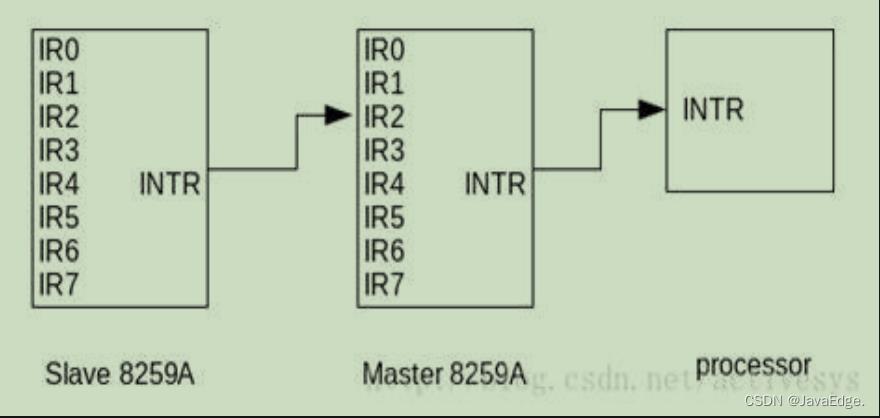

如下图所示,两片8259A级联可以处理共15种中断,其中包括时钟,键盘,软盘,硬盘,DMA等等。

当链盘被敲击时,就会通过8259A向CPU发出中断请求,CPU根据中断号判断是什么类型的中断。

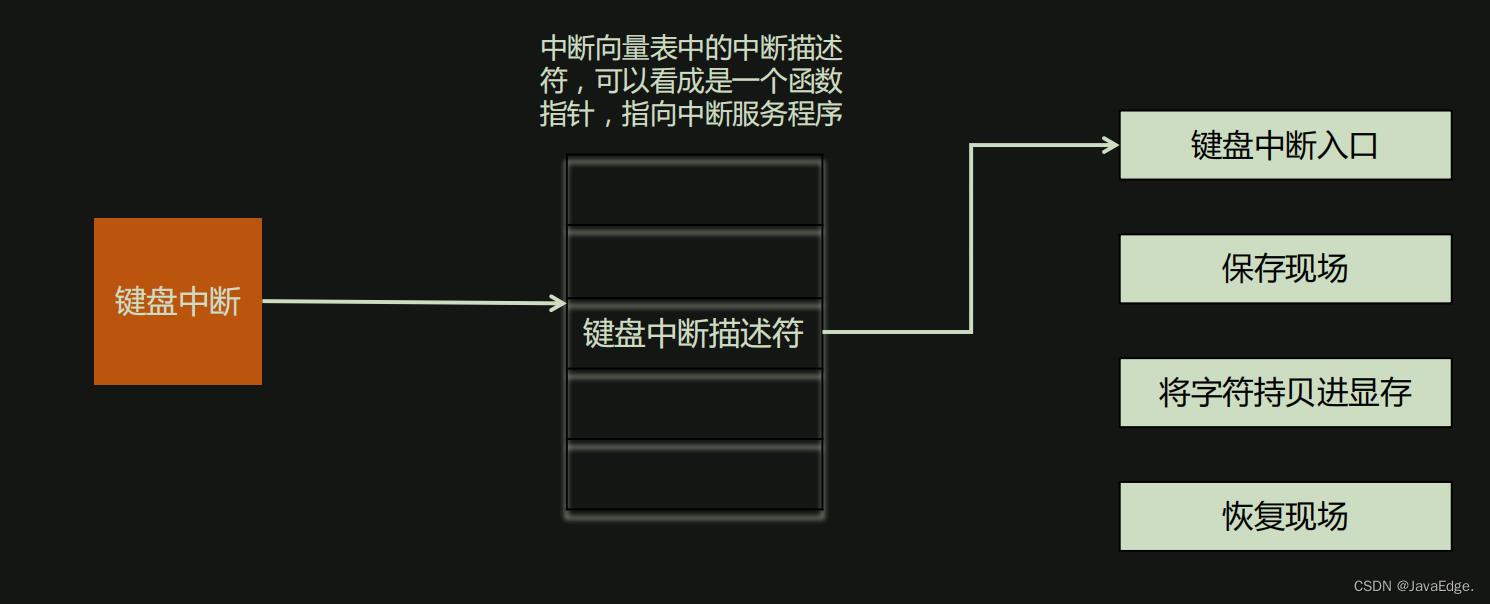

4.2 中断服务程序

以上是关于CPU基本结构和运行原理的主要内容,如果未能解决你的问题,请参考以下文章