如何关闭jtag保留swd-STM32-F0/F1/F2专区

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了如何关闭jtag保留swd-STM32-F0/F1/F2专区相关的知识,希望对你有一定的参考价值。

参考技术A 你用SWD就好,不用的管脚自行安排。无所谓关闭JTAG了。具体操作:

保留SWD调试口,其它JTAG口可以释放出来作为GPIO.

对于STM32F1系列,有个专门的释放操作。涉及到SWJ_CFG[1:0] 位 在AFIO_MAPR 寄存器进行配置,关闭相应管脚的debug调试功能后,可另外配置为GPIO或模拟输入。

对于其它系列,直接通过GPIOx_MODER配合GPIO复用功能配置寄存器进行设置,即选择复用功能脚还是普通GPIO脚或者做模拟输入等。不同系列可能稍有差异,具体参考各系列参考手册debug port部分】

jtag管脚复用---lattice LCMXO3

当IO资源不够的时候,会考虑复用专用IO,JTAG是较为常见的复用。

复用JTAG IO要做的工作

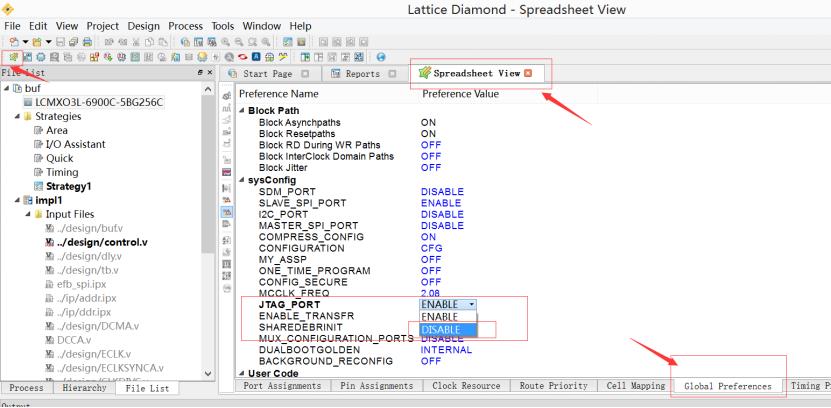

1.软件要关闭JTAG_PORT,即JTAG_PORT设置为DISABLE,这一步是前提,只有JTAG_PORT设置为DISABLE,才有复用一说,如下图

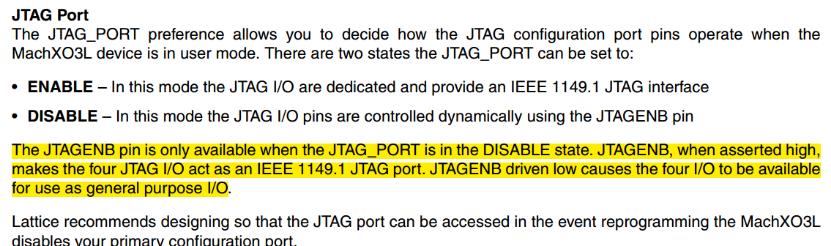

2.硬件要将JTAGENB拉低,拉高的话是作为专用下载程序的脚使用(这个在硬件上默认拉高拉低无所谓),如下图。

3.通过CPU控制JTAGENB的电平,传到lattice芯片内部。JTAGENB=1时,JTAG的脚作为烧写程序使用,JTAGENB=0时,作为普通IO使用,如下图。

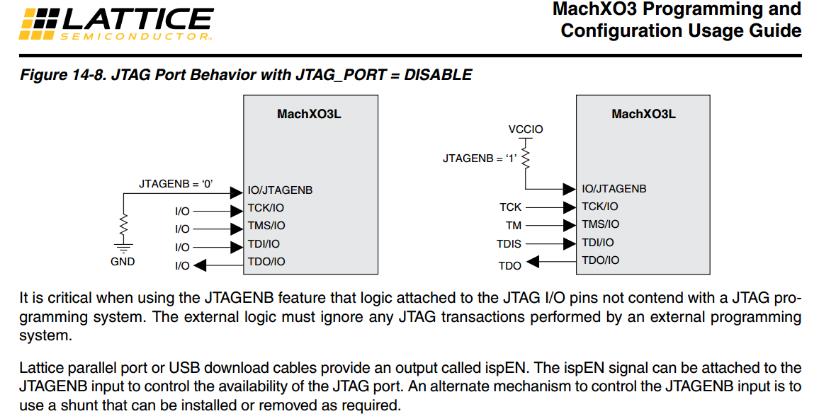

要思考的问题:什么时候烧写程序结束呢?为什么要思考这个问题呢?因为你需要告知CPU JTAGENB什么时候才能够为低电平,让JTAG脚进入普通IO状态。假如你不知道JTAGENB应该为低电平的时间点,当还在进行烧写程序的时候,你告知CPU让JTAGENB为低电平,从而使JTAG进入普通IO的状态,那么此时是不是程序还没有下载完毕,这样用户功能是不是不正常?所有得找到一个合适的时间点,让JTAGENB拉低。

最笨的方法吗就是,看你的下载程序有多大,然后TCK按照25MHZ计算烧写程序所需的时间T,CPU做一个延时,延时时间大于T的时候让JTAGENB拉低,使得JTAG进入普通IO的状态,以防万一延时时间可以给多一点,2T较为合适。

还有一个办法是比较明智的,检查DONE信号,如下图。当DONE信号上升沿到来时说明加载完毕了,此时就可以将JTAGENB拉低。这个办法显然比上述一种好用,一来可以节省时间,二来可以省去繁琐的计算。劣势在哪里呢?管脚不本来就不够用了,你还用了我一个DONE作为专用脚,不用DONE作为检测信号的时候,可以将其用作普通IO.

以上是关于如何关闭jtag保留swd-STM32-F0/F1/F2专区的主要内容,如果未能解决你的问题,请参考以下文章