fpga实操训练(数码管)

Posted 嵌入式-老费

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了fpga实操训练(数码管)相关的知识,希望对你有一定的参考价值。

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

数码管虽然形式上和led不一样,但是基本原理其实是一样的。一个数码管其实是有很多段组成的,这些段的组合,会构建出不同的图形,而这些图形描绘成最终的数字。

1、数码管的显示

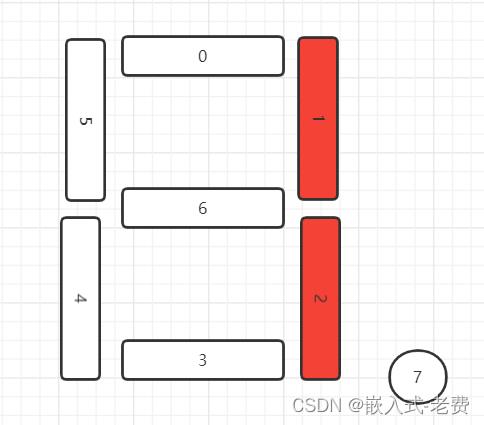

比如上面这个数码管,本身是由8个部分组成,0-6是一个逆时针的led管组成,7是圆点。如果点亮数码管显示出数字1的话,那么点亮1和2就可以构成数字1。这个时候,输出的数据0000_0110。当然如果是输入0点亮数码管的话,那么输出的数据则应该是1111_1001。这个时候,大家辛苦整理下,就可以知道全部0-9的数字应该怎么显示了,

always@(posedge clk or negedge rst)

if(!rst)

seg_data <= 8'b1100_0000;

else

case (num)

4'd0:

seg_data <= 8'b1100_0000;

4'd1:

seg_data <= 8'b1111_1001;

4'd2:

seg_data <= 8'b1010_0100;

4'd3:

seg_data <= 8'b1011_0000;

4'd4:

seg_data <= 8'b1001_1001;

4'd5:

seg_data <= 8'b1001_0010;

4'd6:

seg_data <= 8'b1000_0010;

4'd7:

seg_data <= 8'b1111_1000;

4'd8:

seg_data <= 8'b1000_0000;

4'd9:

seg_data <= 8'b1001_0000;

default:

seg_data <= 8'b1100_0000;

endcase2、数码管的选择

数码管的部分算是讲完了,那下面就是数码管的选择问题。为了减少pin的使用,数码管的数据段是共享的。试想一个,如果数码管的数据段不共享,那么6个数码管就要6*8,即48个信号引脚,这是非常占用资源的。但是如果数据段共享,而可以只用6个sel信号就能把他们区分开来。这个时候只需要总共6+8=14个信号引脚。14相对于48,还是能节约不少资源的。

always @(posedge clk or negedge rst)

if(!rst)

seg_sel <= 6'b011111;

else if(count == 32'd4999_9999)

seg_sel <= seg_sel[0],seg_sel[5:1];3、数码管的测试

为了学习数码管,我们设计了一个循环显示阿拉伯数字的小电路程序,大家可以参考下。

module seg_test(clk, rst, seg_sel, seg_data);

input clk;

input rst;

output seg_sel;

output seg_data;

wire clk;

wire rst;

reg[5:0] seg_sel;

reg[7:0] seg_data;

reg[31:0] count;

reg[3:0] num;

wire out_clk;

demo_test demo_test0(

.clk(clk),

.out_clk(outclk)

);

always @(posedge clk or negedge rst)

if(!rst)

seg_sel <= 6'b011111;

else if(count == 32'd4999_9999)

seg_sel <= seg_sel[0],seg_sel[5:1];

always@(posedge clk or negedge rst)

if(!rst)

count <= 32'b0;

else if(count != 32'd4999_9999)

count <= count + 1;

else

count <= 32'b0;

always@(posedge clk or negedge rst)

if(!rst)

num <= 4'd0;

else if(count == 32'd4999_9999) begin

if(num != 4'd9)

num <= num + 1;

else

num <= 4'd0;

end

always@(posedge clk or negedge rst)

if(!rst)

seg_data <= 8'b1100_0000;

else

case (num)

4'd0:

seg_data <= 8'b1100_0000;

4'd1:

seg_data <= 8'b1111_1001;

4'd2:

seg_data <= 8'b1010_0100;

4'd3:

seg_data <= 8'b1011_0000;

4'd4:

seg_data <= 8'b1001_1001;

4'd5:

seg_data <= 8'b1001_0010;

4'd6:

seg_data <= 8'b1000_0010;

4'd7:

seg_data <= 8'b1111_1000;

4'd8:

seg_data <= 8'b1000_0000;

4'd9:

seg_data <= 8'b1001_0000;

default:

seg_data <= 8'b1100_0000;

endcase

endmodule

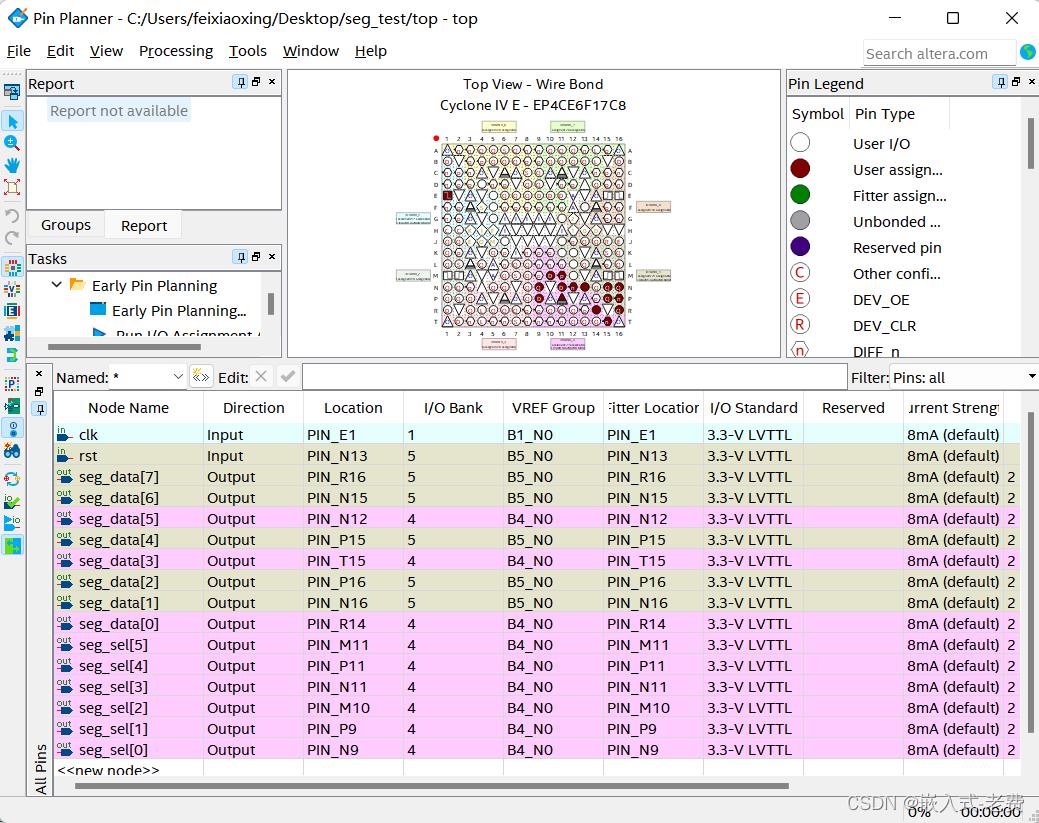

4、pin脚的bind

有了电路还是远远不够的,还需要对这些引脚进行信号绑定。

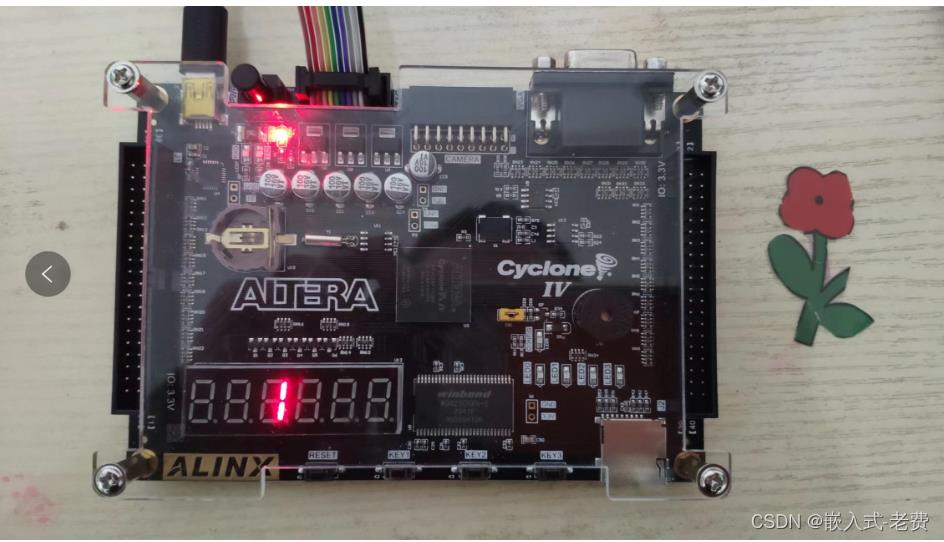

5、验证和测试

有了veirlog文件和pin脚绑定,剩下来的就是编译和烧入了。一切如果没有问题的话,你就会看到这样的实验效果,

以上是关于fpga实操训练(数码管)的主要内容,如果未能解决你的问题,请参考以下文章