软件设计师考试重点1 计算机组成与体系结构

Posted 编程圈子

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了软件设计师考试重点1 计算机组成与体系结构相关的知识,希望对你有一定的参考价值。

软件设计师考试重点1 计算机组成与体系结构

一、 数据的表示

1. 进制转换

- R进制转十进制使用按权展开法。

- 十进制转R进制使用短除法。

2. 原码/反码/补码/移码

- 正数的原码、反码、补码是相同的。

- 负数:

– 原码:原始数据;

– 反码:原码除符号位求反;

– 补码:在反码基础上加1;

– 移码:在补码的基础上,符号位取反。

3. 数值表示范围

| 码制 | 定点整数 | 定点小数 |

|---|---|---|

| 原码 | − ( 2 n − 1 − 1 ) -(2^n-1-1) −(2n−1−1) 至 + ( 2 n − 1 − 1 ) +(2^n-1-1) +(2n−1−1) | − ( 1 − 2 − ( n − 1 ) ) -(1-2^-(n-1)) −(1−2−(n−1)) 至 + ( 1 − 2 − ( n − 1 ) ) +(1-2^-(n-1)) +(1−2−(n−1)) |

| 反码 | − ( 2 n − 1 − 1 ) -(2^n-1-1) −(2n−1−1) 至 + ( 2 n − 1 − 1 ) +(2^n-1-1) +(2n−1−1) | − ( 1 − 2 − ( n − 1 ) ) -(1-2^-(n-1)) −(1−2−(n−1)) 至 + ( 1 − 2 − ( n − 1 ) ) +(1-2^-(n-1)) +(1−2−(n−1)) |

| 补码 | − ( 2 n − 1 ) -(2^n-1) −(2n−1) 至 + ( 2 n − 1 − 1 ) +(2^n-1-1) +(2n−1−1) | − 1 -1 −1 至 + ( 1 − 2 − ( n − 1 ) ) +(1-2^-(n-1)) +(1−2−(n−1)) |

| 移码 | − ( 2 n − 1 ) -(2^n-1) −(2n−1) 至 + ( 2 n − 1 − 1 ) +(2^n-1-1) +(2n−1−1) | − 1 -1 −1 至 + ( 1 − 2 − ( n − 1 ) +(1-2^-(n-1) +(1−2−(n−1) |

4. 浮点数的运算

浮点数表示:

N

=

尾

数

∗

基

数

指

数

N = 尾数* 基数^指数

N=尾数∗基数指数

浮点数的运算顺序:

- 对阶

- 尾数计算

- 结果格式化

运算要点:

- 一般尾数用补码,阶码用移码

- 阶码的位数决定数的表示范围,尾数位数决定数的有效精度

- 对阶时,小数向大数看齐

- 对阶是通过较小数的尾数右移实现的

二、运算器与控制器

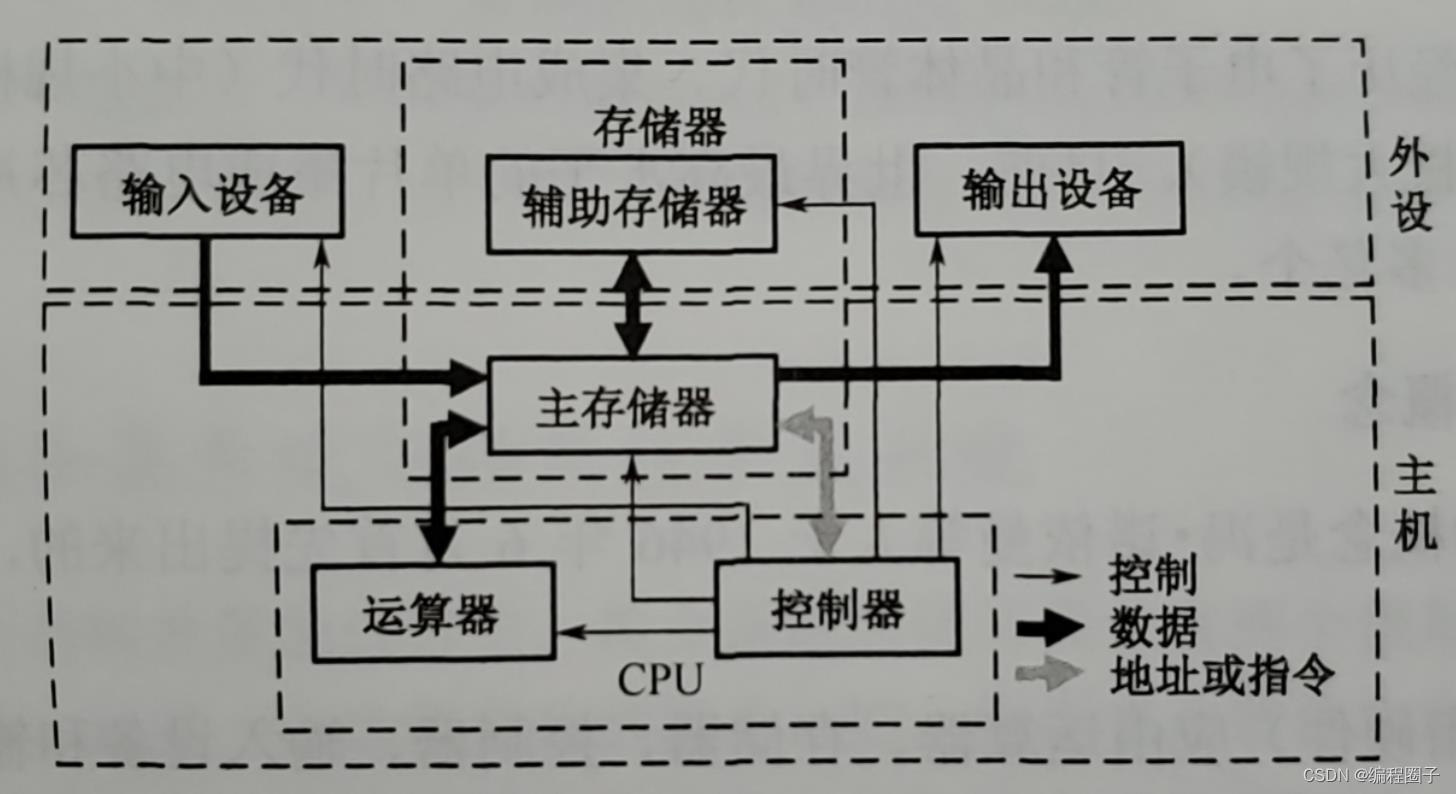

1. 计算机结构

2. 计算机五大组成部分:

- 运算器

- 控制器

- 存储器:分主存(内存储器)、辅助存储器

- 输入设备

- 输出设备

3. CPU组成部分:

- 运算器

- 控制器

- 寄存器组

4. 控制器组成部分:

- 程序计数器 PC:存储下一条要执行指令的地址

- 指令寄存器 IR

- 地址寄存器 PR 记录CPU当前访问的地址

- 指令译码器

- 时序部件:时钟

5. 运算器组成部分:

- 算术逻辑单元ALU:数据计算和逻辑运算

- 累加寄存器 AC:为ALU提供一个工作区,用暂存数据

- 数据缓冲寄存器 DR:写内存时,暂存指令和数据

- 状态条件寄存器PSW(这个比较特殊,历年考试它算在运算器还是控制器不一定):存状态标志和控制标志。

6. Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流 SISD | 控制部分:1个 处理器:1个 主存模块:1个 | 单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:1个 处理器:多个 主存模块:多个 | 各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:1个 主存模块:多个 | 被证明不可能,至少不实际 | 目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 | 能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

7. 指令的基本概念

一条指令是机器语言的一个语句,是一组有意义的二进制代码,基本结构:

操作码字段-地址码字段

- 操作码:指出要作什么操作,如加、移位、存取数。

- 地址码: 需要包含各操作数的地址及操作结果的存放地址等,从其地址结构的角度可以分为三地址指令、二地址指令、一地址指令和零地址指令。

8. 寻址方式

- 立即寻址方式:操作数直接在指令中

- 直接寻址方式:指令中存放操作数的地址

- 间接寻址方式:指令中放了地址,地址放的是操作数的地址

- 寄存器寻址方式:寄存器存放操作数

- 寄存器间接寻址方式:寄存器内存放的是操作数的地址

9. CISC与RISC

| 指令系统类型 | 指令 | 寻址方式 | 实现方式 | 其它 |

|---|---|---|---|---|

| CISC 复杂指令集 | 数据多,使用频率差别大,可变成格式 | 支持多种寻址方式 | 微程序控制技术(微码) | 研制周期长 |

| RISC 精简指令集 | 数量少,使用频率接近,定长格式,大部分为单周期指令,操作寄存器,只有Load/Store操作内存 | 支持方式少 | 增加了通用寄存器;硬布线逻辑控制为主,适合采用流水线 | 优化编译,有效支持高级语言 |

—以下非考试重点—

常见的CISC指令集:x86指令集

x86的指令集可分为以下4种:

- 通用指令

- x87 FPU指令,浮点数运算的指令

- SIMD指令,就是SSE指令

- 系统指令,写OS内核时使用的特殊指令

一些指令示例:

| 指令 | 操作说明 |

|---|---|

| MOV | 将源操作数传送到目标操作数 |

| ADD | 将源操作数与目标操作数相加 最后结果给到目标操作数 |

| SUB | 将源操作数与目标操作数相减 最后结果给到目标操作数 |

| AND | 将源操作数与目标操作数进行与运算 最后结果给到目标操作数 |

| OR | 将源操作数与目标操作数进行或运算 最后结果给到目标操作数 |

| XOR | 将源操作数与目标操作数进行异或运算 最后结果给到目标操作数 |

| NOT | 将源操作数与目标操作数进行异非运算 最后结果给到目标操作数 |

| MOVS | 数据传送 与MOV不同处在于它可以将内存的数据传送到内存 |

| STOS | 将 AL AX EAX 的值存到EDI指定的内存地址 |

| REP | 循环 |

| PUSH | 押入 通用寄存器 内存地址 立即数 |

| POP | 释放。通用寄存器 内存地址 |

| JMP | 修改EIP(存放下一条指令的地址) |

| CALL | 修改EIP |

| RET | CALL的返回 |

常见的RISC指令集: ARM指令集

ARM指令集可以分为六大类:

- 跳转指令

- 数据处理指令

- 程序状态寄存器(PSR)处理指令

- 加载/存储指令

- 协处理器指令

- 异常产生指令

| 指令 | 说明 |

|---|---|

| ADC | 带进位的32位数加法 |

| ADD | 32位数相加 |

| AND | 32位数的逻辑与 |

| B | 在32M空间内的相对跳转指令 |

| BEQ | 相等则跳转(Branch if EQual) |

| BNE | 不相等则跳转(Branch if Not Equal) |

| BGE | 大于或等于跳转(Branch if Greater than or Equa) |

| BGT | 大于跳转(Branch if Greater Than) |

| BIC | 32位数的逻辑位清零 |

| BKPT | 断点指令 |

| BL | 带链接的相对跳转指令 |

| BLE | 小于或等于跳转(Branch if Less than or Equal) |

| BLEQ | 带链接等于跳转(Branch with Link if EQual) |

| BLLT | 带链接小于跳转(Branch with Link if Less Than) |

| BLT | 小于跳转(Branch if Less Than) |

| BLX | 带链接的切换跳转 |

| BX | 切换跳转 |

| CDP CDP2 | 协处理器数据处理操作 |

| CLZ | 零计数 |

| CMN | 比较两个数的相反数 |

| CMP | 32位数比较 |

| EOR | 32位逻辑异或 |

| LDC LDC2 | 从协处理器取一个或多个32位值 |

| LDM | 从内存送多个32位字到ARM寄存器 |

| LDR | 从虚拟地址取一个单个的32位值 |

| MCR MCR2 MCRR | 从寄存器送数据到协处理器 |

| MLA | 32位乘累加 |

| MOV | 传送一个32位数到寄存器 |

| MRC MRC2 MRRC | 从协处理器传送数据到寄存器 |

| MRS | 把状态寄存器的值送到通用寄存器 |

| MSR | 把通用寄存器的值传送到状态寄存器 |

| MUL | 32位乘 |

| MVN | 把一个32位数的逻辑“非”送到寄存器 |

| ORR | 32位逻辑或 |

| PLD | 预装载提示指令 |

| QADD | 有符号32位饱和加 |

| QDADD | 有符号双32位饱和加 |

| QSUB | 有符号32位饱和减 |

| QDSUB | 有符号双32位饱和减 |

| RSB | 逆向32位减法 |

| RSC | 带进位的逆向32法减法 |

| SBC | 带进位的32位减法 |

| SMLAxy | 有符号乘累加(16位*16位)+32位=32位 |

| SMLAL | 64位有符号乘累加((32位*32位)+64位=64位) |

| SMALxy | 64位有符号乘累加((32位*32位)+64位=64位) |

| SMLAWy | 号乘累加((32位*16位)>>16位)+32位=32位 |

| SMULL | 64位有符号乘累加(32位*32位)=64位 |

| SMULxy | 有符号乘(16位*16位=32位) |

| SMULWy | 有符号乘(32位*16位>>16位=32位) |

| STC STC2 | 从协处理器中把一个或多个32位值存到内存 |

| STM | 把多个32位的寄存器值存放到内存 |

| STR | 把寄存器的值存到一个内存的虚地址内间 |

| SUB | 32位减法 |

| SWI | 软中断 |

| SWP | 把一个字或者一个字节和一个寄存器值交换 |

| TEQ | 等值测试 |

| TST | 位测试 |

| UMLAL | 64位无符号乘累加((32位*32位)+64位=64位) |

| UMULL | 64位无符号乘累加(32位*32位)=64位 |

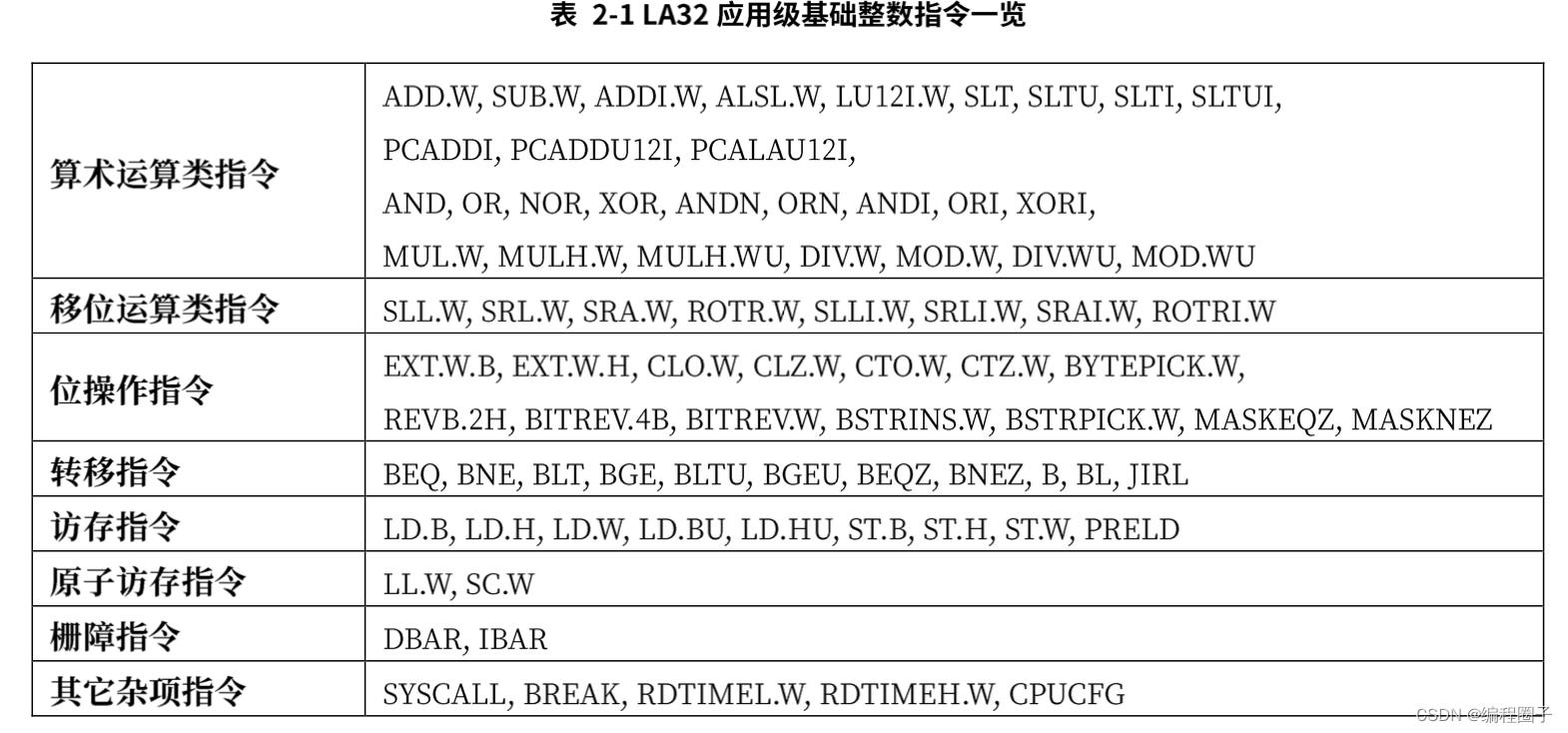

国产的RISC指令集: 龙芯 指令集

手册虽然可以免费下载,但手册里有一条:

不能公开散发,我~~~~~

截个图意思一下:

新兴的RISC指令集:RISC-V

指令示例:

| 指令 | 描述 | 例子 |

|---|---|---|

| add | 加法 | |

| sub | 减法 | |

| and | 逻辑加法 | |

| or | 逻辑或 | |

| xor | 逻辑异或 |

—以上非考试重点—

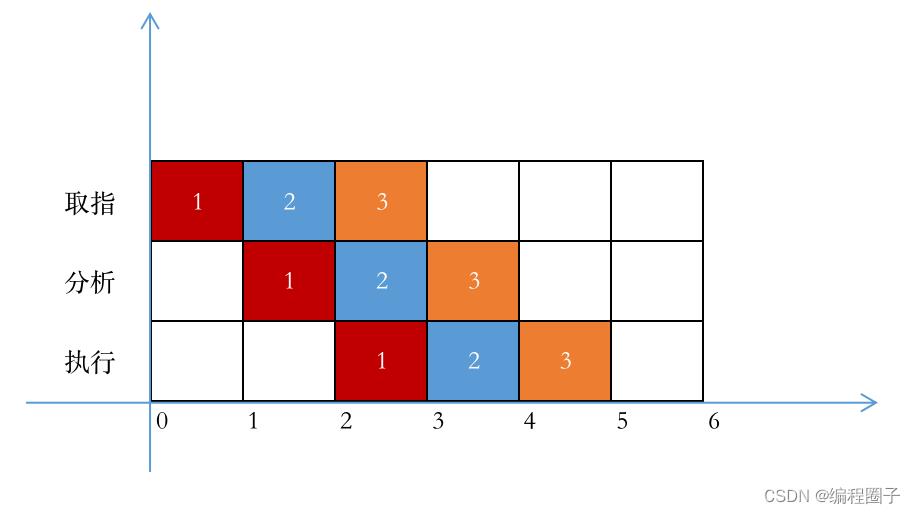

五、流水线技术

1. 流水线概念

流水线是指程序执行多条指令重叠进行操作的一种准并行处理实现技术。

使用流水线执行指令:

2. 流水线计算

- 流水线周期为执行时间最长的一段

- 流水线计算公式:1条指令执行时间+(指令条数-1)*流水线周期

-

- 理论公式: ( t 1 + t 2 + . . . . t k ) + ( n − 1 ) ∗ Δ t (t_1+t_2+....t_k)+(n-1)*\\Delta t (t1+t2+....tk)+(n−1)∗Δt

-

- 实践公式: k ∗ Δ t + ( n − 1 ) ∗ Δ t k*\\Delta t +(n-1)* \\Delta t k∗Δt+(n−1)∗Δt

3. 超标量流水线

在标准状态下,一个处理器含一条指令流水线,超标量就是一个处理器中有多条指令流水线,单位是度。

4. 流水线吞吐率计算

流水线的吞吐率是指在单位时间内流水线所完成的任务数量或输出的结果数量,基本公式:

T

P

=

指

令

条

数

流

水

线

执

行

时

间

TP=\\frac指令条数 流水线执行时间

TP=流水线执行时间指令条数

流水线最大吞吐率:

T

P

m

a

x

=

lim

n

→

∞

n

(

k

+

n

−

1

)

∗

Δ

t

=

1

Δ

t

TP_max = \\lim_n \\to \\infty \\fracn(k+n-1)*\\Delta t = \\frac1\\Delta t

TPmax=n→∞lim(k+n−1)∗Δtn=Δt1

六、存储系统

1. Cache

局部性原理与命中率

- 在计算机的存储体系中,是访问速度最快的层次(若有寄存器,则寄存器最快)。

- 使用Cache 改善系统性能的依据是程序的局部性原理。

- 如果以 h 代表对Cache的访问命中率,

t

1

t_1

t1表示Cache的周期时间,

t

2

t_2

t2表示主存储器周期时间,以读操作为例,使用“Cahce+主存储器”的系统的平均周期为

t

3

t_3

t3,则:

t 3 = h × t 1 + ( 1 − h ) × t 2 t_3=h \\times t_1 + (1-h) \\times t_2 t3=h×t1+(1−h)×t2

其中,(1-h)又称为失效率(未命中率)。

映像

地址映像是将主存与Cache的存储空间分为若干个大小相同的页(或称为块)。

| 映像 | 冲突率 |

|---|---|

| 直接相联映像 | 硬件电路简单,但冲突 以上是关于软件设计师考试重点1 计算机组成与体系结构的主要内容,如果未能解决你的问题,请参考以下文章 |