硬件安全技术——芯片安全设计技术3

Posted 摆渡沧桑

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了硬件安全技术——芯片安全设计技术3相关的知识,希望对你有一定的参考价值。

芯片安全设计技术3

一、硬件安全解决方案

1. 为什么需要硬件安全

- 安全是系统级的,如果只是软件进行安全防护,那么无法建立强有力的信任根

- Crypto Engine只是解决了密码计算问题,只是单纯的拼凑组合是无法组成安全系统的

- 各种高等级的认证要求底层的核心安全,密码实现需要由硬件来完成参与

2. 传统安全解决方案对比

三种方法:MCU,TEE,SE

方案无好坏之分,只有是否符合系统的应用场景来选择解决方案

3. SoC安全解决方案

- 将传统的SE的功能集成到SoC中,避免了板级走线带来的安全风险

- 避免了外部的数据传输性能的瓶颈,可以作为加速器使用

- 无需额外的芯片,降低了整体成本

- 目前手机AP厂商大多数使用该解决方案

二、Root of Trust(信任根)

1. 信任根(RoT)是建立信任链的来源,也是SoC中安全根基

其涉及安全启动、密钥管理两部分

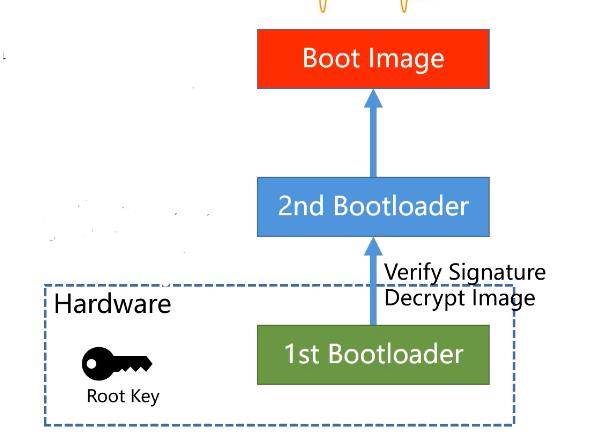

2. 安全启动

- 硬件负责初始化安全启动过程中需要使用的模块,例如随机数发生器、安全传感器、NVM控制器等

- CPU从自身ROM中读取一级启动代码,对外部的二级Bootloader 进行解密和验签,确保二级Bootloader的完整性和认证性

3. 密钥管理

- 保护密钥的机密性,密钥一般存储在NVM中

- 确认密钥的完整性

- 提前考虑各种角色,确保在实际场景中的可用性

- 结合芯片生命周期管控烧写、使用、debug相关权限

三、关键安全模块

1. MPU/MMU

访问地址、权限隔离

2. Crypto Engine

- 提供各种秘钥运算的支持

- 提升秘钥运算的性能和安全性

- 避免软件可以访问关键秘钥,高等级的安全认证密钥硬件化

3. Detector

探测环境的异常变化

当在攻击硬件时,可能需要通过升压,提高频率等措施,而当SoC系统中存在这些监控异常变化时,能够及早的预防这些异常变化,从而保护硬件安全。

4. Storage Protection Unit

保护存储单元内的数据,地址总线和数据总线都需要加密、加扰

5. Bus Protection Unit

保护总线上传输的信息,地址和数据都需要加扰(实时性比较高,一般只做加扰)

6. Secure Processor

- 利用Memory Tagging等技术防止关于Memory的攻击

- 利用Time constant计数防止Timing Attack

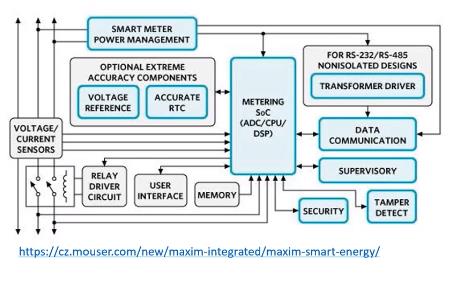

四、安全系统的应用—— 智能电表

- 智能电表是IoT典型安全敏感应用

- 智能电表处于一个开放的不可控的环境下

- 只能电表覆盖量极大,并且与基础民生相关,有着很高的价值

- 智能电表是一个典型的基于MCU的SoC芯片,SoC中有着很多的防护措施保护RoT和运行安全

五、总结

- 安全系统方案多种多样,根据实际业务场景进行选择

- 单一模块无法保证系统安全,系统安全需要从硬件、软件、生产和使用统筹考虑

- RoT需要由硬件来实现从而达到不可篡改的特性

- 随着新兴行业(IoT,5G)的发展,硬件安全的重视程度逐渐提升

以上是关于硬件安全技术——芯片安全设计技术3的主要内容,如果未能解决你的问题,请参考以下文章