DDR3上的DM信号如何连接 电路设计

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DDR3上的DM信号如何连接 电路设计相关的知识,希望对你有一定的参考价值。

DDR3上的DM信号可否直接接地还是有其它连接设计.

DM具有什么作用?

DM is sampled HIGH coincident with that input data during a Write access. DM is sampled

on both edges of DQS. 参考技术B nsahfsadk

参考资料:bd

DDR测试读写分离方法

一、DDR概述

如今,存储器件在计算机、汽车与消费电子产品上可谓无所不在。其中DDR SDRAM(Double Data Rate SDRAM的缩写,即双数据率同步动态随机存取存储器)是最常用的存储器设计技术之一,而随着该技术的发展,其传输速率在日益加快,功耗在日益降低。

传输速度加快使得此类存储器的验证难度呈指数上升。存储系统要准确工作,其信号完整性必须满足某种最低要求。因为信号完整性对系统互通性而言非常关键,或者说只有保持信号完整性才能保证不同厂商生产的器件在一起使用时能够很好地结合。信号完整性问题会引发包括时序冲突、协议背离、时钟抖动以及由其他总线引发的错误等其它问题。本文介绍了DDR信号的测量方法,DDR信号验证中面临的挑战,并针对其调试方法给出了相关建议。文中提到的方法适用于DDR、DDR2、DDR3、DDR4和SDRAM这一类全缓冲的DIMM系统调试。为简单起见,这些内存技术在下文中统称为DDR。

二、测量方法

JEDEC规范定义了 DRAM的引脚或球必须满足的电气与时序方面的要求。一些较新的DDR DRAM采用了精细球栅阵列(FBGA)封装,此封装下的焊接球很难接触。因此,我们建议测量时,探头应尽可能接近DRAM的球状焊点。通常,我们可以在与焊接球相连的过孔上或与其相连的电阻靠近DRAM一侧的焊盘上测量。

目前差分有源电压探头的探头容性负载可低至fF级别,是德科技官网上显示,其差分有源电压探头最高带宽高达30GHz。此类工具对DDR信号的影响非常小,很适合DDR测量。由于DDR信号对噪声非常敏感,因此建议在测量此类信号时采用带宽足够大的示波器,以避免示波器的噪声影响测量。有些示波器具备带宽压缩功能,能调节至恰好适合测量的带宽,以实现最精确和可重复的测量。图1所示为13GHz差分有源探头连接到DDR2 DIMM的过孔上的情形。

图1 13GHz差分有源探头连接到DDR2 DIMM的过孔上

三、信号验证所面临的挑战

同一根数据总线上的DDR数据传输是双向的。这使DDR信号验证变得非常困难,因为我们首先必须分离数据总线上复杂的数据流才能对其进行信号完整性测量。而要想独立分析(由存储控制器和DDR芯片驱动的)信号完整性和时序关系,也必须分离数据流。

在探头和数据总线上存在三种状态,读操作(输出信号)、写操作(输入信号)和高阻(空闲状态)。由于DDR信令比较复杂,因此为了能快速测试、调试和解决信号上的问题,我们希望能简单地进行读/写分离。下面介绍几种分离方法。

3.1 利用Preamble差异分离读/写信号

我们可以利用读/写Preamble差异来触发示波器,实现读/写信号分离。

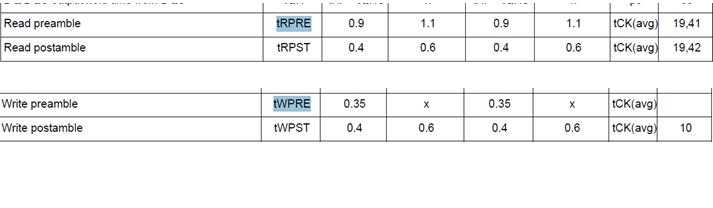

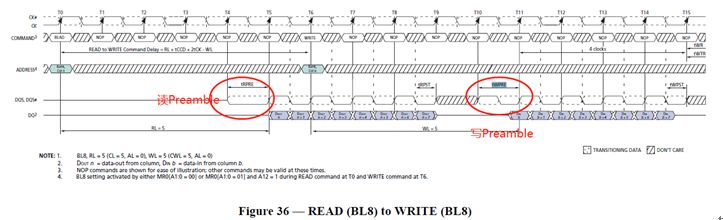

在每次的Burst之前,DQS会从高阻态切换到一段负脉冲,然后才开始正常的读写。这段负脉冲,我们叫做Preamble(Preamble实际上是在读写前,DQS提前通知DRAM芯片或者是Controller的信号)。一般说来,读数据DQS的Preamble宽度要大于写数据。如图2所示根据JEDEC DDR2规范,读前导的宽度为0.9到1.1个时钟周期,而写前导的宽度规定为大于0.35个时钟周期,没有上限。于是,我们在设置触发条件之前,首先要确定读/写前导的宽度。由于读前导和写前导各自有不同的宽度,因此可利用这一点分离读出的数据和写入的数据。如图3所示,对于DDR3、DDR4,读数据的Preamble是负脉冲,写数据的Preamble是正脉冲,分离就更简单。

图2 读写Preamble宽度(摘自DDR2标准)

图2 读写Preamble宽度(摘自DDR2标准)

图3 读写Preamble(摘自DDR3标准)

图4 利用DQS信号的Preamble差异触发来分离读/写信号。

但对于DDR2,这种方法在使用过程中也存在问题。

首先,JEDEC规范中对前导宽度的定义比较松散,而且不同 ASIC/ DRAM厂商在这方面的定义也不尽相同。此外,由于写前导的上限没有定义,因此它也有可能与读前导宽度相同,而如果二者的值过于接近,那么要想分离读信号与写信号就十分困难了。

第二,如果写前导的宽度为0.5个时钟周期,与一个数据比特的宽度相当,那么硬件触发器就无法区分写前导比特与正常数据比特。

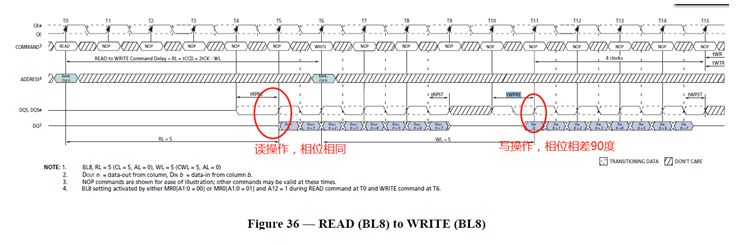

3.2 利用相位差分离读/写信号

如图5所示,读信号与写信号之间有一个重要差异:写数据是DQS和DQ Centre-Align(中间对齐), 读数据DQS和DQ是Edge-Align(边沿对齐),Memory Controller在接收到内存的读数据时,在controller内部把DQS和DQ的相位错开90度,实现中间对齐来采样。

图5 读写相位差异(摘自DDR3)

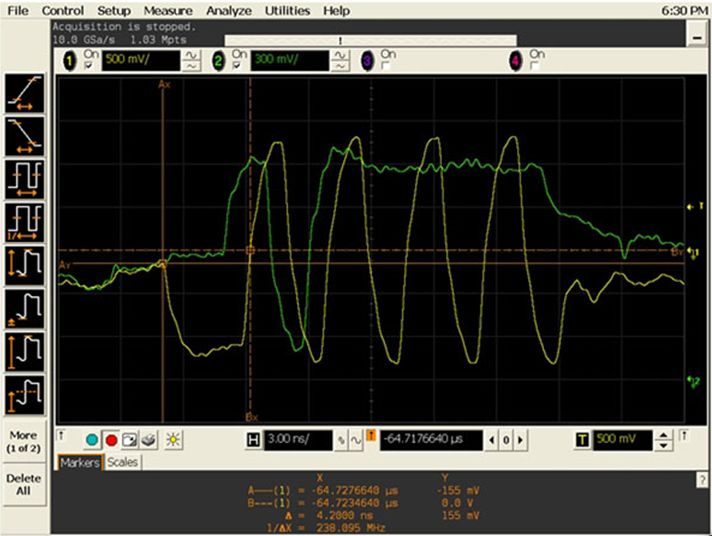

3.3 利用更大的信号幅度触发方法分离读/写信号

通常,读/写信号的信号幅度是不同的,因此我们可以通过在更大的信号幅度上触发示波器来实现两者的分离。一般在DRAM端进行测试时,写数据从Memory Controller出来,到达DRAM颗粒的时候,信号已经被衰减了,而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的幅度要大于写数据。在Memory Controller测试时,也是相同的道理。

3.4 利用斜率差分离读/写信号

读数据的斜率大于写数据。在DRAM端进行测试时,写数据从Memory Controller出来,到达DRAM颗粒的时候,信号已经被衰减了,所以,斜率也小一些;而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的斜率要大于写数据。

3.5 利用脉冲宽度分离读/写信号

DQS是双向信号,读数据从DRAM出来,经过PCB走线到达Memory Controller;而写数据从Memory Controller出来,经过PCB走线到达DRAM。当在DRAM端进行测试时,读信号由于反射在信号边沿可能会存在回勾,信号宽度相对于写数据就有差异,这时就可以根据脉宽宽度对读/写信号进行分离。

图6 利用信号宽度触发来分离读/写信号。

四、本文小结

随着DDR存储技术的不断发展,DDR信号的完整性问题也日益突出。要想在测量中得到最佳结果,需要采用恰当的测量方法,这就要求必须了解JEDEC规范,找到DDR读写的差异,根据差异就可以对读写进行区分了。本文所提到的五种方法一定会给大家带来很大帮助。

以上是关于DDR3上的DM信号如何连接 电路设计的主要内容,如果未能解决你的问题,请参考以下文章