微机原理与汇编语言考点总结

Posted 绀香零八

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了微机原理与汇编语言考点总结相关的知识,希望对你有一定的参考价值。

十分感谢我的组长hxj一直以来耐心解答我不会的大题,作业、编程题都让我白嫖,hxj组长yyds!!!

这个小测是老师从汇编所有留的作业+课本课后习题中重点的习题中抽取出来的,一开始我是很崩溃的,好在弄明白了

⚠本人水平有限,如有错误,欢迎在评论区指正

愿我汇编不挂!!!

参考了打印店的微机原理与汇编语言中2018-2019学年2016级的考试卷子

试卷结构如下:

一、单项选择 【10个,每题2分,总共20分】

二、填空题 【10个,每题1分,总共10分】

三、简答计算题 【6个,总共28分】

四、分析编程题 【6个,总共42分】

其中 一、二 绝大多数题来源于下面小测的填空题

其中 三 绝大多数来源于下面小测的计算题+简答题

其中 四 绝大多数来源于下面小测的分析题+编程题

加油,期末人!

文章目录

填空题

(一)十进制数286D对应的十六进制数为11EH;十六进制数2AH对应的十进制数为42;十六进制数9A7CH对应的二进制数为 (1001 1010 0111 1100)B;二进制数0001 0010 0100 1011B对应的十六进制数为124BH,对应的十进制数为4683。

(二)某CPU的时钟周期是1ns,其时钟频率是 1GHz。

f=1/T=1/(1 * 10^-9)= 10^9Hz

⚠:s(秒)、ms(毫秒)、μs(微秒)、ns(纳秒),

其中:1s=1000ms,1 ms=1000μs,1μs=1000ns

⚠:1KHz=1000Hz,1MHz=1000KHz,1GHz=1000MHz

(三)有数据定义语句BUF DB 12,3AH,10 DUP(3 DUP(1,0),2,8,6),汇编后,为变量BUF分配的存储单元字节数是92。

dup重复括号里的东西 10*(3*(2)+3) = 90个字节+外面俩=92字节

(四)中央处理单元CPU由 运算器 、 控制器 、和 寄存器 三部分组成。

(五)在计算机中,通常 运算器 和 控制器 是核心部件,合称为中央处理单元CPU。

(六)某CPU的字长为8,假设该CPU执行一次加法运算需要1ns,执行两个double 类型的数(假设double类型的变量占8个字节)相加时需要 8ns。

一次8位数累加1ns, 1字节8各位 ,8字节=64位,累加8次

字长:处理器每个时间单位处理的二进制数据位数(例如一次运算、传输的位数),指示处理器的数据处理能力

(七)摩尔定律指出,每 18 个月集成电路的性能将提高一倍,而其价格将降低一半。

(八)汇编指令由 操作码 和 操作数 组成。

(九)指令mov al,3中,源操作数的寻址方式是立即数寻址;指令mov al,cl中,源操作数的寻址方式是 寄存器寻址 ;指令mov al,[3]中,源操作数的寻址方式是 内存寻址 。

(十)JMP指令或带条件转移JC、JZ、JE指令中,转移的本质是改变 IP 寄存器的值。

JC、JZ、JE段内转移, 段内偏移量变

(十一)段间函数调用的本质是改变 CS 寄存器和 IP 寄存器的值。

(十二)某微机具有256M字节的内存空间,其CPU的地址总线至少应有 28 条。

256= 2^8

M = 2^20

256M = 2^28

(十三)CPU芯片可以与它外部的两类芯片进行交互信息,这两类芯片分别是 内存储器芯片 、 I/O接口芯片 ;这些芯片之间通过 总线 互相连接。

(十四)总线根据其上传送的信号可以分成三组,分别是地址总线、控制总线和数据总线。

(十五)一条指令的执行包括三个步骤: 取指 、译码、 执行 。

(十六)8086CPU可以从功能上分为 总线接口 部件和 运算 部件。

(十七)8086CPU内部的AX是一个 16 位寄存器,可以进一步将其分为高8位寄存器 AH 和低8位寄存器 AL 。

(十八)8086微处理器中,代码段中下一条要执行的指令的物理地址由CS代码段起始寄存器和 IP 指针 寄存器指示。

(十九)逻辑地址由段地址和 偏移地址 两部分组成;如果CPU内部的DS=1A38H,执行MOV BL,[3AH]这条指令时,要用到的这个数据在内存中的物理地址是1A3BAH。

段地址加偏移量

DS左移四个二进制位补0

1A380H+偏移量3AH=1A3BAH

(二十)标志寄存器中控制串传送方向的标志位是DF。

(二十一)已知SP=2028H,执行POP AX后,SP寄存器的值是202AH。

(二十二)已知SP=2020H,执行PUSH AX后,SP寄存器的值是201EH。

POP加,PUSH减16-2=14

(二十三)8086 CPU中用于选择访问对象的引脚是M/IO*。

(二十四)8086 CPU中用于选择CPU工作方式的引脚是MN/MX*。

(二十五)8086 CPU用 ALE 引脚信号下降沿在T1结束时将地址信息锁存在地址锁存器中。

(二十六)CMP CX,128BH指令之后是JZ指令,发生转移的条件是CX= 128BH ,此时ZF= 1 。

JZ/JC/JX 都是ZF=1

(二十七)若要检查AX寄存器中的D11位是否为1,但不改变其中的值,应该用 TEST 指令。

(二十八)占用总线进行数据传输,一般需要经过 总线请求和仲裁 、寻址 、 数据传送 和 结束 4个阶段。

(二十九)在利用总线对存储器进行访问时,地址信号先有效还是数据信号先有效? 地址信号 。

T1传地址信号

(三十)8086 CPU无等待的总线周期由4个T状态组成。

(三十一)决定CPU 是否需要插入等待周期Tw的CPU 引脚是 READY ,当CPU采样到其上的值为0时,CPU将插入等待周期Tw ;插入的等待周期在总线周期的哪个T之后? T3 。

和cpu交流的人ready否

(三十二)8086 CPU执行指令“MOV [DI], AL”时,在其引脚上将产生存储器写总线操作;CPU预取指令时,在其引脚上将产生存储器读总线操作;8086 CPU执行指令“OUT DX, AL”时,在其引脚上将产生I/O接口写总线操作。

预取指令读内存

OUT 对IO接口做写操作 CPU把东西往外送 把AL送到IO接口

(三十三)CPU在执行OUT DX,AL指令时,DX寄存器的内容送到地址总线上。

(三十四)CPU在执行OUT DX,AL指令时,AL寄存器的内容送到数据总线上。

(三十五)存储系统中的局部性原理可以从 时间局部 和 空间局部 两个方面来理解。

(三十六)衡量存储器速度的两个指标:存取时间和存取周期,哪个更大? 存取周期 。

存取周期包含微调时间

(三十七)RAM的英文全称是 Random Access Memory 。

随机存取存储器(英语:Random Access Memory,缩写:RAM),也叫主存,是与CPU直接交换数据的内部存储器。

(三十八)ROM的英文全称是 Read-Only Memory 。

只读存储器(Read-Only Memory,ROM)

(三十九)存储器芯片的译码方式有全译码方式和 部分译码方式 。

(四十)在微机系统中,微处理器对外设的访问,实质上是对 IO接口/IO端口进行访问。

(四十一)I/O接口的作用是数据缓冲和 信号转换 。

(四十二)I/O端口的编址方式有两种,一种是 独立编址 ,另一种是 统一编制 。

(四十三)8086 CPU能访问的外部内存的地址空间为 1MB 。

2^20

(四十四)8086 CPU能访问的外部I/O接口的地址空间为64KB 。

2^16/64K

(四十五)在DMA、通道、中断、程序查询传送这四种数据传送方式中,占用CPU时间最长的传送方式是程序查询。

(四十六)8086 CPU 中断系统中的中断分内部中断和 外部中断 。

(四十七)8086 CPU接收外部中断的引脚有 NMI 和 INTR 两个;当CPU接到外部的可屏蔽中断后,决定是否响应该中断的标志位是 IF ,其响应信号由引脚送出去。

IF 中断允许位 响应INTA*

(四十八)8086 CPU的中断系统共有 256 个中断类型码。

(四十九)某一中断程序入口地址值填写在中断向量表的 0060H — 0063H 存储单元中,则该中断对应的中断类型号一定是 24/18H 。

60H与60不一样 =96/4=24

计算题

(一)将下列逻辑地址转换为物理地址。

3100H:4100H

90H:1AH

0A100H :280EH

段地址加偏移量

CS左移四个二进制位补0

段地址 【前】+偏移量【后】=物理地址

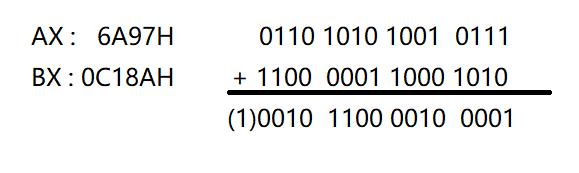

(二)

mov ax, 6A97H

mov bx, 0C18AH

add ax,bx

执行上面三条指令后,ax中的值是多少?CF、OF、SF、ZF分别是多少?请给出ax和bx对应的16个二进制位加法式子。

AX=2C21H

可以列16进制位加法/二进制位加法,16进制位加法看不出来,列二进制序列

汇编SF、CF、 OF 、ZF、 PF

CF=1 进位标志

OF=0 溢出标志 结果的最高位与次高位做异或 0010中的00异或为0

SF=0 符号标志 16位的最高位决定 0010 中的0

ZF=0 零标志 ax结果不是0

(三)8086 CPU的中断系统中,15号中断的中断向量保存在物理地址为多少开始的4个连续字节空间?如果其内容从低地址开始依次是10H、53H、80H、0A2H,则其中断服务程序的首地址是多少?

15*4=60 60D=3CH

60号 : 10H 61号 : 53H 62号 : 80H 62号 : 0A2H

CS:0A280H

IP: 5310H 相加0A7B10H

中断服务程序的首地址: 0A280H : 5310H

简答题

(一)一般的I/O接口电路安排有哪三类寄存器?它们各自的作用是什么?

接口芯片内部包含:数据寄存器、状态寄存器、控制寄存器

数据寄存器:保存处理器与外设之间交换的数据。

状态寄存器:保存接口电路和外设当前的工作状态信息。

控制寄存器:保存处理器控制接口电路和外设操作的相关信息。

(二)8259内部包含3个中断控制寄存器IRR、ISR、IMR,简要说明各自功能。

IRR:中断请求寄存器,用来存放来自外设的中断请求信号

ISR:中断服务寄存器,用来存放正在处理的中断

IMR:中断屏蔽寄存器,用来保存对中断请求信号IR的屏蔽状态

(三)全译码与部分译码

全译码方式,使用全部微处理器地址总线进行译码,低位地址与存储器芯片地址引脚相连,高位地址经译码与存储器芯片片选引脚相连。

特点:存储单元和储存地址一一对应,组成的存储器地址空间连续,译码电路较复杂。

部分译码方式,只使用部分微处理器地址总线进行译码,没有使用的地址信号对存储器芯片的工作不产生影响。

特点:存在地址重复,译码电路比较简单。

(四)接口芯片的作用

数据缓冲:匹配快速的微处理器与相对慢速的外设的数据交换

信号变换:把信号相互转换为适合计算机和外设双方的形式

(五)什么是局部性原理?

处理器访问存储器时,所访问的存储单元在一段时间内部趋向于一个较小的连续区域中。包括时间局部性和空间局部性。

分析题

(一)某CPU地址线20根,数据线8根,其16-13号引脚分别对应多路复用的AD3-AD0,当前CS=12ACH,IP=007DH,DS=31A0H。

假设IP当前所指向的指令为mov DS:[5],AX ,该指令在内存中占3个字节,AX中的值为5A7BH;

假设CPU所连接的总线的频率是100HZ,它内部的数据总线的宽度是8,利用该总线传送16位数据时,先传送低8位,再传送高8位。

T = 1S中传数据

回答下列问题:

1、该CPU执行IP所指向的这条指令的过程中,取指+执行总共需要几次访问内存?

取指访问3次内存+执行2次=5次

该指令在内存中占3个字节 + 它内部的数据总线的宽度是8,利用该总线传送16位数据时,先传送低8位,再传送高8位2字节

2、在取指对应的总线周期的T1中,16-13号引脚(即A3-A0)的值分别是多少?

CS寄存器左移4位补0+IP寄存器后 取最低四位:D = 1 1 0 1

3、在取指对应的总线周期中,M/IO* 引脚=?RD* 引脚=? WR* 引脚=?

存储器读总线操作

M/IO* 引脚= 1

RD* 引脚 = 0

WR* 引脚 = 1

4、在执行指令对应的第一个总线周期的T1中,16-13号引脚(即A3-A0)的值分别是多少?

DS: 31A0H,左移4位补0+偏移量5 = 31A05H

20位地址的最低4位 算出来是5

0 1 0 1

5、在执行指令对应的第一个总线周期的T2-T4中,16-13号引脚(即D3-D0)的值分别是多少?

第一次传AX低8位,7B中的低四位 1 0 1 1

6、在执行指令对应的第二个总线周期的T2-T4中,16-13号引脚(即D3-D0)的值分别是多少?

第二次传AX高8位,5A中的低四位 1 0 1 0

7、在执行指令对应的总线周期中,M/IO* 引脚=?RD* 引脚=? WR* 引脚=?

存储器写总线操作

M/IO* 引脚= 1

RD* 引脚 = 1

WR* 引脚 = 0

8、这条指令的指令周期是多少秒?

CPU所连接的总线的频率是100HZ

T0 = 1/f = 1/100 = 0.01s

用3+2次总线 ,访问内存就是读/写,用总线传递要往内存写的信息或者读取的信息

T = 5*T0 = 0.05s

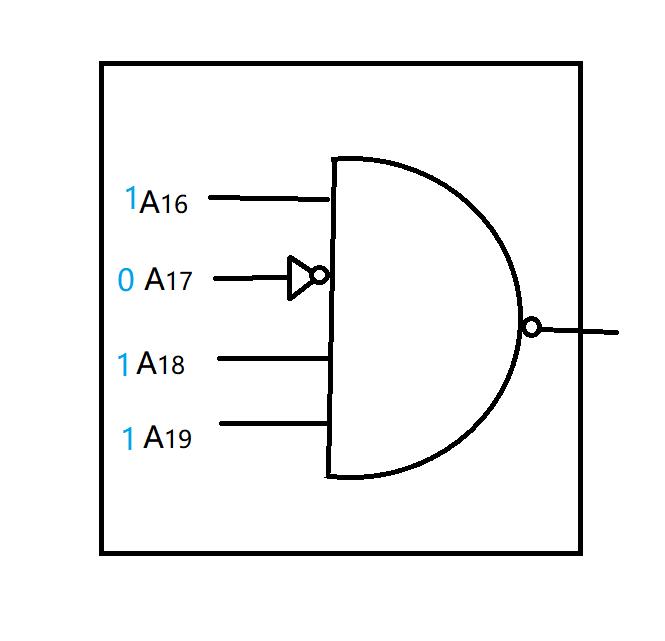

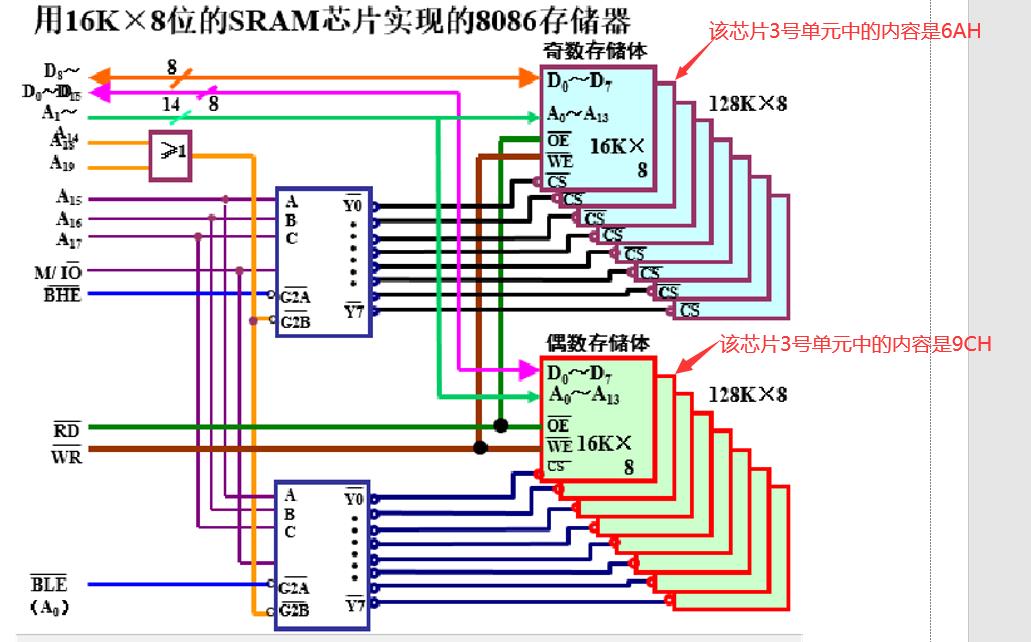

(二)某CPU的外部内存结构图如下,请回答下列问题:

1、偶存储体中红色箭头所指的内存芯片中的3号单元,其在CPU处的物理地址是多少?如果CPU想从该地址处取两个字节到AX中,此时BHE*引脚的值必须为0还是1?

咱也不明白啥是奇偶体,百度了一个👉计算机组成原理 奇偶体

A[Address] D[Data]

物理地址就是按照图示分析A19-A0这20根地址线什么情况下选中偶存储体中第二块芯片的三号单元

A0(BLE*)连的是38译码器的使能端,看图低电平有效,所以A0接0

A1~A14是用来片内寻址的选中第3号单元,所以A1 ~ A14为3

A15~A17是用来选芯片的,选第二片,第二片是Y1也就是001,38译码器A为低位

A18A19做或运算的结果应该为0才能让译码器工作,所以A18A19为00

A19A18A17A16 A15A14A13A12 A11A10A9A8 A7A6A5A4 A3A2A1A0

0000 1000 0000 0000 0110

如果CPU想从该地址处取两个字节到AX中,此时BHE* 引脚的值必须为0

因为他要读取两个自己,高低同时选中,BHE* 是高,BLE* 是低,BHE* 是低电平有效

2、取完两个字节后,AX的值是多少?

6A9CH

由图可以看到BHE[high]连的是奇存储体存高字节,BL[low]E连的是偶存储体存低字节

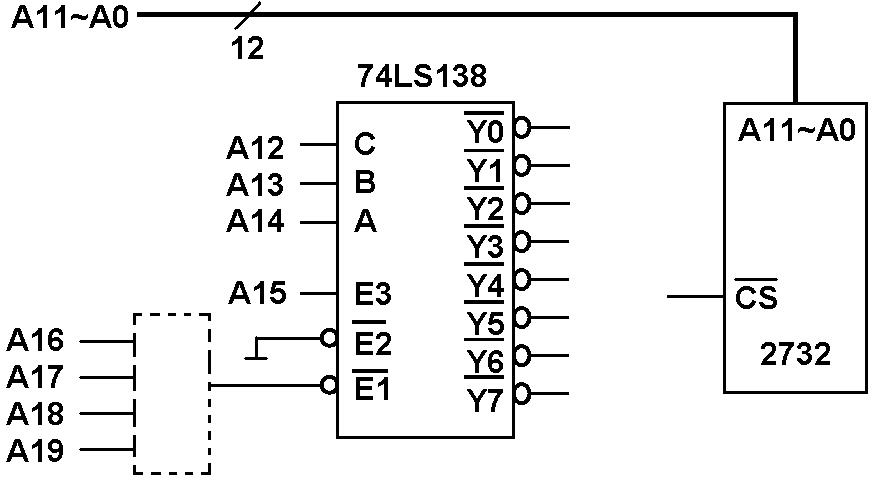

(三)设计一个存储器接口电路,其中部分电路给出如下图所示,要求该存储系统的地址范围为0D9000H~0D9FFFH,可增加的器件可以是基本门电路(与门、或门、非门、与非门、或非门),完成74LS138同CS的连接,画出虚线框中门电路。

D=13=8+4+1=(1101)B

【0D9000H,0为16进制字母打头的标志】

A19A18A17A16 A15A14A13A12 A11A10A9A8 A7A6A5A4 A3A2A1A0

1101 1001 0000 0000 0000

【0D9FFFH,0为16进制字母打头的标志】

A19A18A17A16 A15A14A13A12 A11A10A9A8 A7A6A5A4 A3A2A1A0

1101 1001 1111 1111 1111

看CBA100=Y4连通

A19A18A17A16=1101

(四)在8086 CPU处理器系统中,假设地址总线A19~A14输出011010时译码电路产生一个有效的片选信号,选中一个存储器芯片,A13~A0用作片内寻址。请计算出这个芯片对应的主存空间的物理地址范围?这个芯片容量是多大?

20根地址线 : 高6位片选信号 ,低14位片内寻址

0110 1000 0000 0000 0000

0110 1011 1111 1111 1111

【物理地址范围】68000H~6BFFFH

片内寻址14 ,2^14个单元,16K个字节,16K*8个二进制位

(五)现有一种存储芯片容量为512×4b,若要用它组成2KB的存储系统,需多少这样的存储芯片(列出算式)?每块芯片需多少寻址线(列出算式)?而2KB存储系统最少需多少寻址线,其中几根用作片选,几根用作片内寻址?

存储系统容量2K=2^11 B/ 512×4 = 2 ^11 b 1B/1b = 8, 需8片这样的存储芯片

2^9=512 每块芯片需9根寻址线

2K=2^11 11根线

2^9=512 9根片内寻址

11-9=2 2根片选

2KB存储系统最少需11根寻址线,其中2根用作片选,9根用作片内寻址

编程题

(一)编写一个子程序,用来以无符号十进制形式显示BX中的数据。(需要压栈出栈)

DATAS SEGMENT

;此处输入数据段代码

DATAS ENDS

STACKS SEGMENT

;此处输入堆栈段代码

STACKS ENDS

CODES SEGMENT

ASSUME CS:CODES,DS:DATAS,SS:STACKS

START:

MOV AX,DATAS

MOV DS,AX

MOV BX,1234 ;入口参数

CALL OUTPUT ;call调用参数

MOV AH,4CH

INT 21H

OUTPUT PROC

PUSH AX ;防止主程序中的数被覆盖

PUSH CX

PUSH DX

MOV AX,BX

MOV CL,10 ;做除数

MOV BH,0 ;记录压栈次数

REDIV:

DIV CL ;div默认用AX做被除数,这里我选择用CL做除数

PUSH AX ;把余数AH和商AL一并压栈,最少压两字节,目的压AH保存AH

ADD BH,1 ;压栈次数加一

CMP AL,0 ;判断当前商是否为0

JE PRINT ;等于0跳去输出

MOV AH,0 ;让AX=AL商

JMP REDIV

PRINT:

CMP BH,0

JE OUTPUTOVER

POP DX ;让栈顶元素出栈

MOV DL,DH ;DH里放的AH余数,只输出余数就ok

ADD DL,48

SUB BH,1 ;每出一次栈计数器就--

MOV AH,2

INT 21H

JMP PRINT

OUTPUTOVER:

POP DX

POP CX ;将原来压栈的主程序中的数弹出

POP AX ;注意顺序 先入后出

RET ;返回

OUTPUT ENDP

CODES ENDS

END START

(二)编写程序,统计变量a1中10个字节型数据中正数和负数的个数,分别存放到ch和cl中。

字节型数据:byte/db 指针+1

DATAS SEGMENT

A1 DB -123,-12,13,14,156,189,-111,-123,-234,-23

DATAS ENDS

STACKS SEGMENT

;此处输入堆栈段代码

STACKS ENDS

CODES SEGMENT

ASSUME CS:CODES,DS:DATAS,SS:STACKS

START:

MOV AX,DATAS

MOV DS,AX

MOV BH,0 ;计数器

MOV CH,0 ;正数

MOV CL,0 ;负数

MOV SI,OFFSET A1

FORBH:

MOV AX,[SI]

AND AX,8000H ;8000h就是最高位为1的数,ax和8000h按位与,结果存回ax

CMP AX,0 ;判正负数取最高位0正1负

JZ ZHENGSHU ;0正1负

INC CL

AGAIN:

INC BH

INC SI

CMP BH,10

JZ OVER

JMP FORBH

ZHENGSHU:

INC CH

JMP AGAIN

OVER:

MOV DL,CH

ADD DL,48

MOV AH,2

INT 21H

MOV DL,CL

ADD DL,48

MOV AH,2

INT 21H

MOV AH,4CH

INT 21H

CODES ENDS

END START

(三)一个条件传送的输出接口由两个端口组成,其数据端口、状态端口的地址分别为310H和311H,用状态端口311H的D3位为高电平表示输出设备就绪,利用上述接口电路把数据区中的字节型变量BUF1中的1000个字节输出,要求如果当前字符是小写字母,需要把其转换为大写字母输出,其它字符原样输出。编写程序段实现上述功能(A的ACSII码是65,a的ASCII码是97)。

;输出设备,课本7-8输入设备

DATAS SEGMENT

;此处输入数据段代码

BUFFER1 DB 1000 DUP(?)

DATAS ENDS

STACKS SEGMENT

;此处输入堆栈段代码

STACKS ENDS

CODES SEGMENT

ASSUME CS:CODES,DS:DATAS,SS:STACKS

START:

MOV AX,DATAS

MOV DS,AX

MOV SI,OFFSET BUFFER1

MOV CX,0

L0:

MOV DX,311H ;置状态口

AGAIN: ;循环检测状态口

IN AL,DX ;读状态口

AND AL,0000 1000B ;检测状态口是否READY

JZ AGAIN

MOV AL,[SI] ;READY后取下一个数

CMP AL,'a'

JB L1

CMP AL,'z'

JA L1

SUB AL,32 ;是a~z之间的减32

L1: ;不是a~z之间到L1输出到数据口

MOV DX,310H

OUT DX,AL

ADD SI,1 ;指针后移

ADD CX,1 ;计数器+1

CMP CX,1000

JE OVER

JMP L0

OVER:

MOV AH,4CH

INT 21H

CODES ENDS

END START

以上是关于微机原理与汇编语言考点总结的主要内容,如果未能解决你的问题,请参考以下文章

微机原理 汇编语言 小舅子考试问我些编程问题,在下实在不会,求各路英雄赐教解困。谢谢!