ASIC-WORLD Verilog第一个Verilog代码

Posted 孤独的单刀

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ASIC-WORLD Verilog第一个Verilog代码相关的知识,希望对你有一定的参考价值。

写在前面

在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的Verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。

这是网站原文:Verilog Tutorial

介绍

如果你去看任何有关编程语言的书籍,就会发现它们的第一个例子几乎都是“Hello World”程序。一旦你学会了这个程序,就可以说你已经对这种语言入门了。

接下来我会先展示如何在 Verilog 语言中编写“hello world”程序,然后再介绍一个稍微复杂点的“计数器”程序。

Hello World

下面是一个在Verilog中打印“hello world”的程序。

//-----------------------------------------------------

// 这是我的第一个Verilog程序

// 设计名: hello_world

// 文件名: hello_world.v

// 功能 : 这个程序会打印'hello world'

// 作者 : Deepak

//-----------------------------------------------------

module hello_world ;

initial begin

$display ("Hello World by Deepak");

#10 $finish;

end

endmodule

Verilog 的程序都以保留字 “module” 开头,后面跟上设计者自定义的模块名 。在上面的示例中,第 8 行即包含“module hello_world”。

第 10 行包含initial块:它只在仿真开始后执行一次,即仿真时间 = 0 (0ns)时。initial块中有两条语句,它们被第 10 行的 begin 和第 13 行的 end 包围起来了。在 Verilog 中,如果一个块中有多行,则需要使用 begin 和 end。

模块以“endmodule”保留字作为结尾,即本例的第 15 行。

这是程序打印的结果:

Hello World By Deepak

计数器

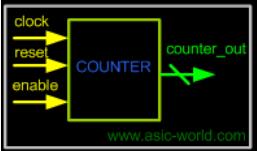

这是要设计的计数器的框图:

它的预期设计规格是这样的:

- 4 位同步递增计数器

- 高电平有效的同步复位信号

- 高电平有效的使能信号

预期的计数器设计Verilog程序如下:

//-----------------------------------------------------

// 这是我的第二个Verilog程序

// 设计名: first_counter

// 文件名: first_counter.v

// 作者 : Deepak

// 功能 : 这是一个4位宽的递增计数器

// 高有效的同步复位;高有效的使能信号

//-----------------------------------------------------

module first_counter (

clock , // 时钟

reset , // 高有效的同步复位

enable , // 高有效的使能信号

counter_out // 计数器输出

);

//-------------Input Ports-----------------------------

input clock ;

input reset ;

input enable ;

//-------------Output Ports----------------------------

output [3:0] counter_out ;

//-------------Input ports Data Type-------------------

// 输入必须是wire变量

wire clock ;

wire reset ;

wire enable ;

//-------------Output Ports Data Type------------------

// 输出可以是wire或者reg

reg [3:0] counter_out ;

//------------Code Starts Here-------------------------

// 这个计数器是时钟上升沿有效的

always @ (posedge clock)

begin : COUNTER // Block名

//在每一个时钟上升沿,如果复位有效,则输出是4'b0000

if (reset == 1'b1) begin

counter_out <= #1 4'b0000;

end

//如果使能有效,则输出递增

else if (enable == 1'b1) begin

counter_out <= #1 counter_out + 1;

end

end

endmodule

任何数字电路,无论复杂与否都需要进行测试以验证其功能的正确性。

对于计数器,我们需要提供时钟和复位信号。一旦计数器不在复位状态,我们将启用输入切换到计数器,并检查波形以查看计数器是否在正确计数。

这是在 Verilog 的 testbench 中完成的。对于这个计数器,我们设计的testbench是这样的:

`include "first_counter.v"

module first_counter_tb();

//声明输入(reg)与输出(wire)

reg clock, reset, enable;

wire [3:0] counter_out;

//初始化所有变量

initial begin

$display ("time\\t clk reset enable counter");

$monitor ("%g\\t %b %b %b %b",

$time, clock, reset, enable, counter_out);

clock = 1; // 初始化时钟信号

reset = 0; // 初始化复位信号

enable = 0; // 初始化使能信号

#5 reset = 1; // 置位复位信号

#10 reset = 0; // 失效复位信号

#10 enable = 1; // 置位使能信号

#100 enable = 0; // 失效使能信号

#5 $finish; // 结束仿真

end

// 生成时钟信号

always begin

#5 clock = ~clock; // 每5个单位时钟翻转一次

end

// 被测模块

first_counter U_counter (

clock,

reset,

enable,

counter_out

);

endmodule这个testbench由时钟发生器(clock gen)、复位控制(reset logic)、使能控制(enable logic)和监控/验证逻辑(monitor/checker)组成。

这是仿真完成后打印的结果,可以看到计数器的工作是符合预期的。

time clk reset enable counter

0 1 0 0 xxxx

5 0 1 0 xxxx

10 1 1 0 xxxx

11 1 1 0 0000

15 0 0 0 0000

20 1 0 0 0000

25 0 0 1 0000

30 1 0 1 0000

31 1 0 1 0001

35 0 0 1 0001

40 1 0 1 0001

41 1 0 1 0010

45 0 0 1 0010

50 1 0 1 0010

51 1 0 1 0011

55 0 0 1 0011

60 1 0 1 0011

61 1 0 1 0100

65 0 0 1 0100

70 1 0 1 0100

71 1 0 1 0101

75 0 0 1 0101

80 1 0 1 0101

81 1 0 1 0110

85 0 0 1 0110

90 1 0 1 0110

91 1 0 1 0111

95 0 0 1 0111

100 1 0 1 0111

101 1 0 1 1000

105 0 0 1 1000

110 1 0 1 1000

111 1 0 1 1001

115 0 0 1 1001

120 1 0 1 1001

121 1 0 1 1010

125 0 0 0 1010

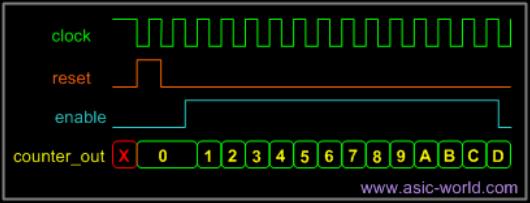

看数据多少有点不够直观,那我们也可以直接来看仿真的波形:

从波形图可以看到:首先复位;复位完成后从0开始依次递增计数。

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

VERI-ZEXE: Decentralized Private Computation with Universal Setup

1. 引言

Espressosy团队开发了一种去中心化隐私计算系统(Decentralized Private Computation,DPC)——VERI-ZEXE,其支持universal setup。具体见Alex Luoyuan Xiong 2022年论文《VERI-ZEXE: Decentralized Private Computation with Universal Setup》。

开源代码见:

为便于 与Aleo SnarkVM testnet2早期版本(不包含testnet3及之后的版本)之前的DPC模型 对比,2022年论文《VERI-ZEXE: Decentralized Private Computation with Universal Setup》第4章中,阐述了对SnarkVM的代码进行了修改,对比发现,VERI-ZEXE生成交易的速度比SnarkVM快约9倍,使用的内存少约2.6倍。

VERI-ZEXE将用于CAPE的后续版本中,在保持可配置资产隐私性的同时,可支持任意用户自定义资产策略。

2. ZEXE背景知识及不足

现有的智能合约系统,如以太坊和Solona,为Web3创新的绝佳温床。但是,这些系统均受限于隐私或(和)可扩展性。为确保公开可验证下,所有的 程序状态和状态变化都是公开透明的,牺牲了隐私,所有的(全)节点都需要重新执行所有的交易或计算,影响了扩展性。

2019年,Bowe等人提出了一种名为decentralized private computation(DPC,去中心化隐私计算)的方案:

- 用户可在链下执行任意计算,使用ZKP来向链上提交一笔交易以证明该计算的正确性。

为实例化该DPC方案,Bowe等人实现了名为ZEXE(zk-execution)的系统,可解决以上隐私性和扩展性的问题。大体上,ZEXE是“programmable ZCash”,由 单一应用系统 到 智能合约系统 过渡的同时,保留了隐私属性。

2.1 ZEXE VS. ZK-Rollup

ZEXE 链下计算、链上验证计算完整性证明,听起来与zk-rollup类似。

- ZEXE中的用户生成交易有效性证明,将交易直接发送到链上

- zk-rollup中的用户将交易发送给rollup validators,由rollup validators生成zk proof发送到链上。

从技术上说,ZEXE并不关心链下计算是如何完成的——是由单个用户,还是由多用户MPC协议,或者是以rollup-server形式完成的。为此,可认为ZEXE和zk-rollup是2种互补的方案。

2.2 ZEXE显著特性

ZEXE的显著特性有:

- 1)数据隐私以及函数隐私:ZEXE可隐藏所有函数状态,以及函数调用的输入/输出(数据隐私),以及每笔交易具体触发了哪个函数/程序(函数隐私)。即使后续有多种隐私智能合约方案,ZEXE仍是唯一可实现函数隐私的方案。

- 2)可编程性:ZEXE用户可为某record附加任意policies/predicates(所谓record,类似Bitcoin Script),record可指定相关程序状态的变更规则。Bowe等人还展示了如何在ZEXE模式下编程实现用户自定义资产、DEXes以及监管合规的稳定币。

- 3)简洁验证:链上validators无需重新执行该计算。相反,链上validators仅需验证该short transaction validity proof,无论链下计算多复杂,链上验证时间均为contant time。

现有的实现(SnarkVM testnet1 和 SnarkVM testnet2)除具有以上特性之外,还存在以下待改进之处:

- 1)circuit-specific setup:ZEXE(SnarkVM testnet1)使用类似GM17和Groth16的non-universal SNARK来证明合约执行的正确性,需要为每个应用/程序做一个trusted setup,几乎不具备实用性。

- 2)性能:具有universal SNARK的ZEXE(SnarkVM testnet2),其性能有大幅下降——由于通用SNARK验证逻辑的复杂性更高,以及ZEXE需为编码了SNARK校验逻辑的statement生成SNARK证明。

3. VERI-ZEXE: universal setup without performance loss

VERI-ZEXE:

- 在保持了原始ZEXE所有特性和属性的前提下,引入了一些优化措施,降低了universal SNARK verifier gadget的circuit复杂性。

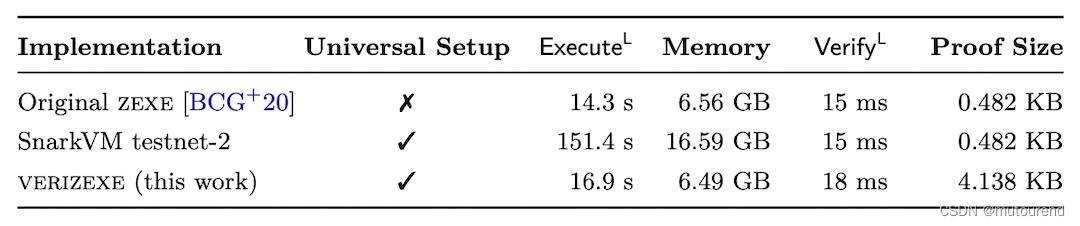

首先,将VERI-ZEXE与ZEXE进行了对比,如以2-input-2-output交易为例,在AMD EPYC 7R13 at 2.65 GHz with 64 cores and 128 GB of RAM上的性能对比(交易生成时间(即Execute算法执行时间)、内存使用情况、交易有效性证明size)为:【交易生成速度要快将近9倍,而内存使用改进了约2.6倍。】

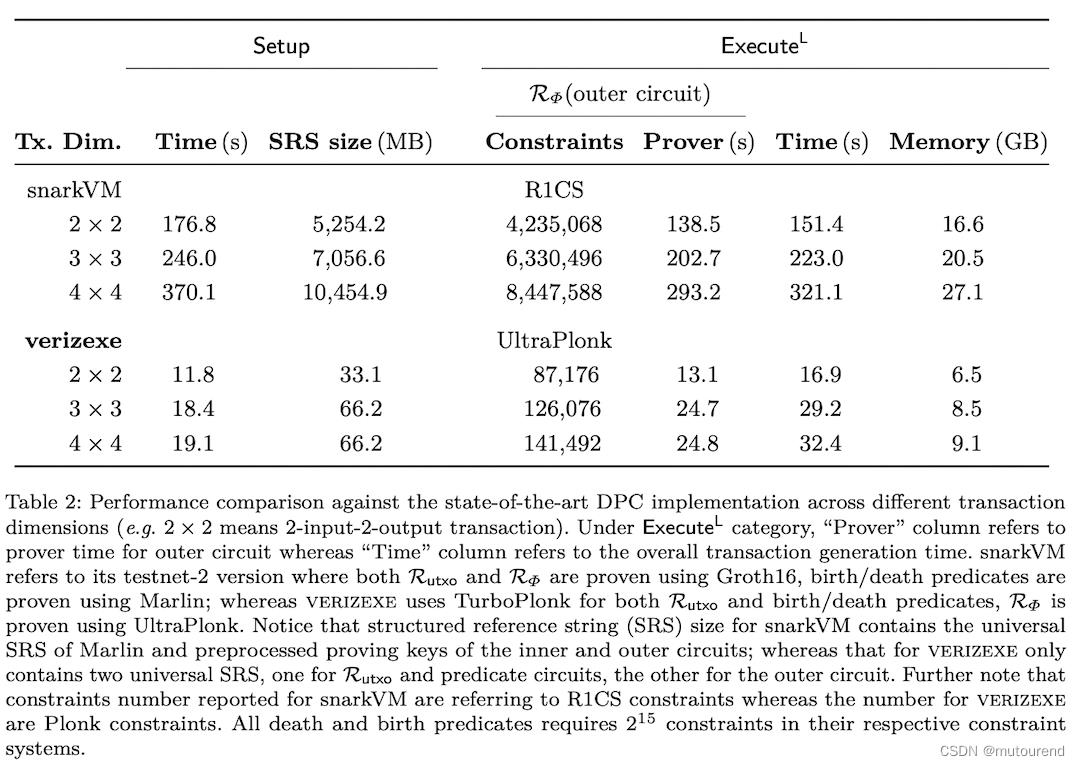

其次,将VERI-ZEXE与SnarkVM testnet2进一步对比,outer circuit(用于depth-2 proof composition) size要小很多,使得prover time能快一个量级,从而具有更快的交易生成:

最后,espressosys团队实现了TurboPlonk和UltraPlonk约束系统,并将其作为基石用于VERI-ZEXE中,可大幅降低约束开销。

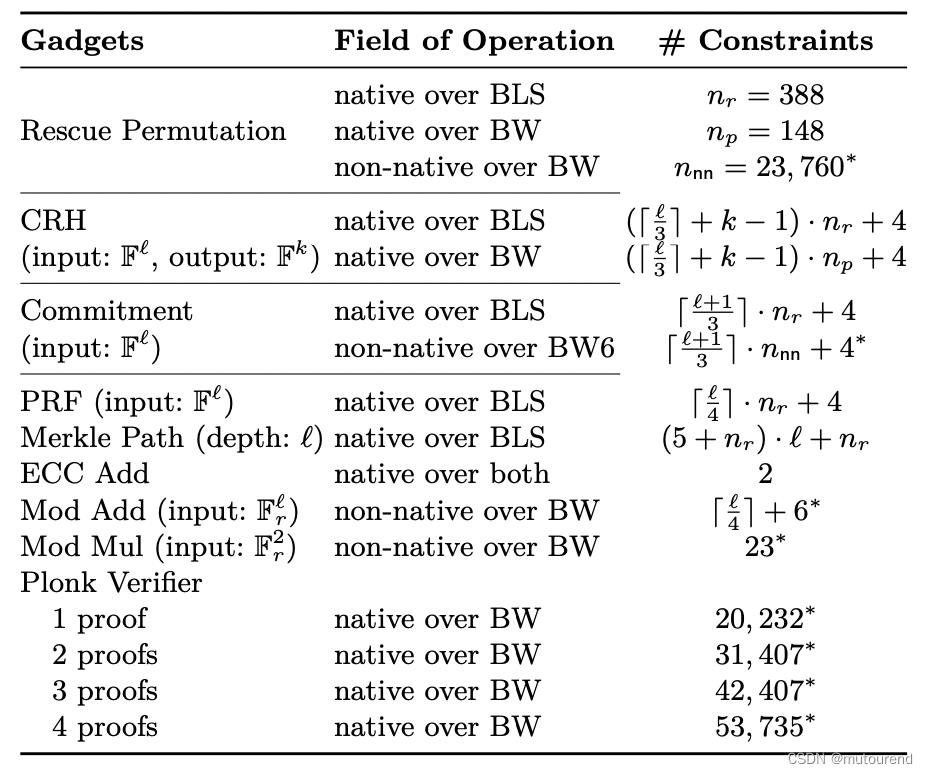

基于TurboPlonk设计,各主要密码学基石和代数运算的PLONK约束数为:

4. VERI-ZEXE + CAPE: customizable asset policy

ZEXE仍存在一些挑战,如:

- 并发问题(当多个用户试图同时变更某共享状态)

- 原子性组合能力(在ZEXE中实现类似Flashloan这样的应用需要名为“in-bundle accumulation”技术,需要对ZEXE的record nano-kernel(RNK)进行小调整)

- 在UTXO模式下进行predicate programming的难度(现有方案,如Chialisp)

由于ZEXE存在以上问题,其并不是隐私智能合约设计的银弹,对于用户间具有最小共享状态,并采用UTXO模式的情况下,采用ZEXE可具有高并发性和低交易依赖项的优势。CAPE就是一个很好的例子。

当前,CAPE协议中仅支持预定义的资产策略集合(如,启动minting、匿名转账、冻结公钥、委托查看策略等),而不是动态的、用户自定义的资产策略。假设你想创建一种新的“concert token”,总供应量为1000,只能对指定的地址付款后才能mint,这种关联新concert token的新minting策略,超过了当前CAPE的能力范围。而未来VERI-ZEXE可使其成为可编程性可能。

参考资料

[1] VERI-ZEXE: Decentralized Private Computation with Universal Setup

附录A. Aleo的SnarkVM

Aleo的SnarkVM经历过多轮迭代:

- 1)Aleo的testnet1为S&P19论文中ZEXE的忠实实现,其需要application-specific trusted setup。

- 2)Aleo的testnet2早期版本中:将生成brith/death predicates proof的证明系统由GM17转换为Marlin,不再是application-specific trusted setup,而成为了“universal” setup。

- 3)Aleo的testnet2后期及之后版本中:改变了其原有的DPC模型,通过简化模型但限制了其可编程性(如,不允许inter-program call)。

- 4)Aleo的testnet3:采用了简化并限制后的DPC模型。

以上是关于ASIC-WORLD Verilog第一个Verilog代码的主要内容,如果未能解决你的问题,请参考以下文章