EDA仿真测试 Modelsim仿真 .vt文件法仿真 .v文件法仿真

Posted 海绵小青年

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了EDA仿真测试 Modelsim仿真 .vt文件法仿真 .v文件法仿真相关的知识,希望对你有一定的参考价值。

一、本文内容

内容:通过两种方法,使用modelsim仿真Verilog程序

版本:Quartus II 13.1(64-bit)

二、通过 “.vt文件” 测试仿真

1、准备工作

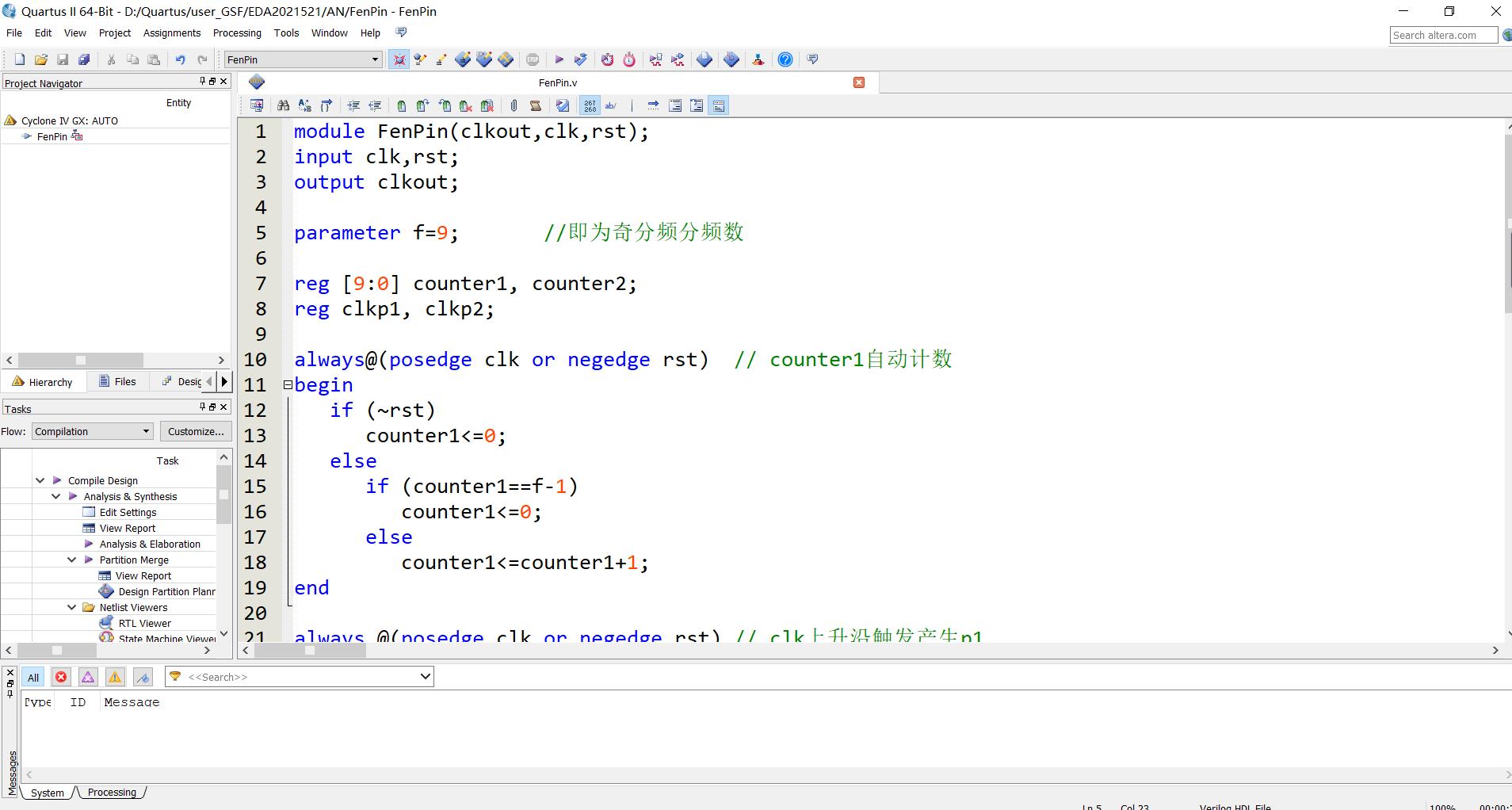

已建立好的工程文件

// 上述工程文件代码 实现奇数分频功能

module FenPin(clkout,clk,rst);

input clk,rst;

output clkout;

parameter f=9; //即为奇分频分频数

reg [9:0] counter1, counter2;

reg clkp1, clkp2;

always@(posedge clk or negedge rst) // counter1自动计数

begin

if (~rst)

counter1<=0;

else

if (counter1==f-1)

counter1<=0;

else

counter1<=counter1+1;

end

always @(posedge clk or negedge rst) // clk上升沿触发产生p1

begin

if(~rst)

clkp1<=0;

else

if(counter1==(f-1)/2 || counter1==f-1)

clkp1<=~clkp1;

end

always @(negedge clk or negedge rst)//counter2自动计数

begin

if(~rst)

counter2<=0;

else

if(counter2==f-1)

counter2<=0;

else

counter2<=counter1+1;

end

always @(negedge clk or negedge rst)//clk下降触发产生p2

begin

if(~rst)

clkp2<=0;

else

begin

if(counter2==(f-1)/2||counter2==f-1)

clkp2<=~clkp2;

end

end

assign clkout=clkp1|clkp2; //p1|p2使占空比等于50%

endmodule

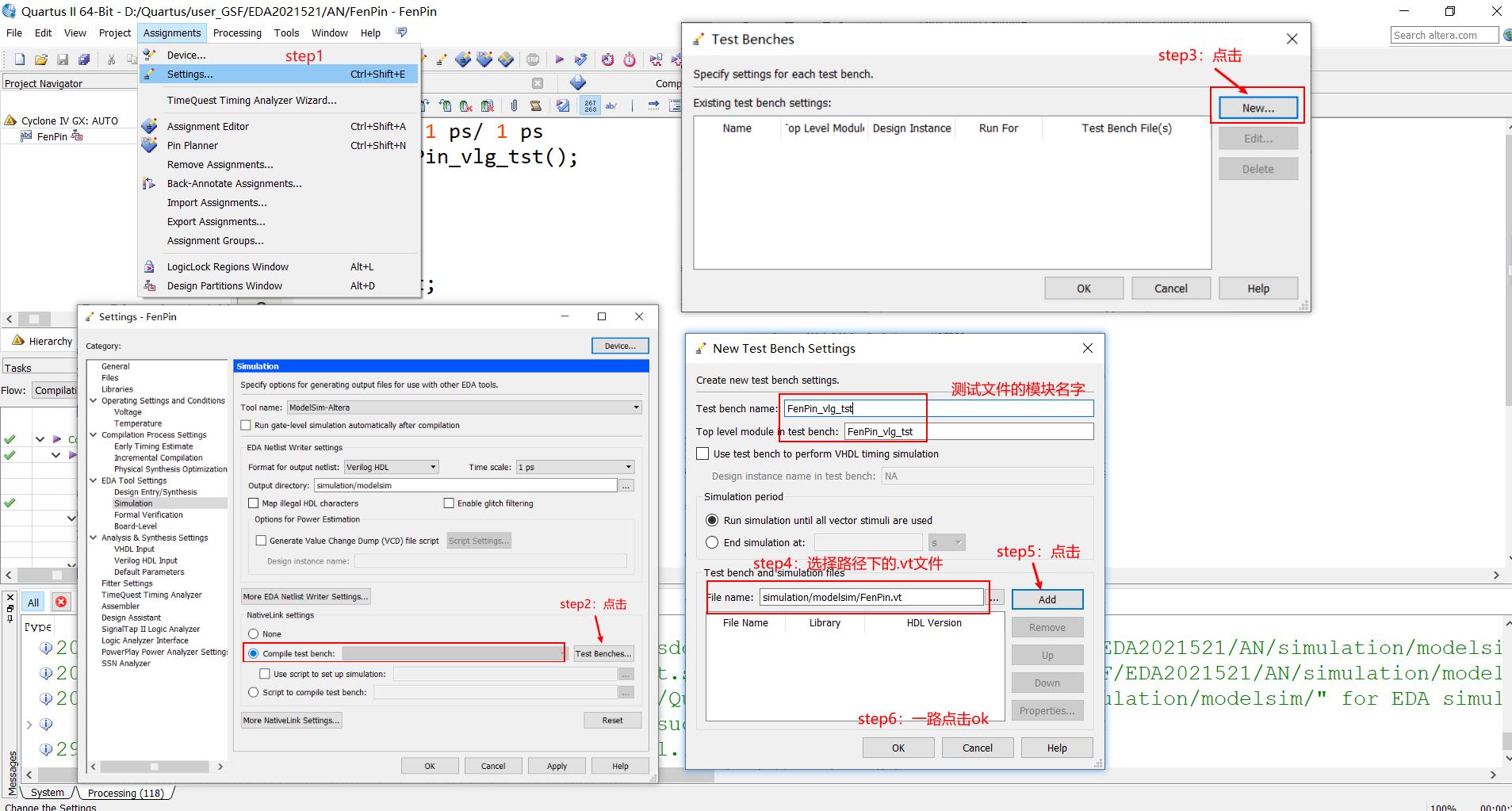

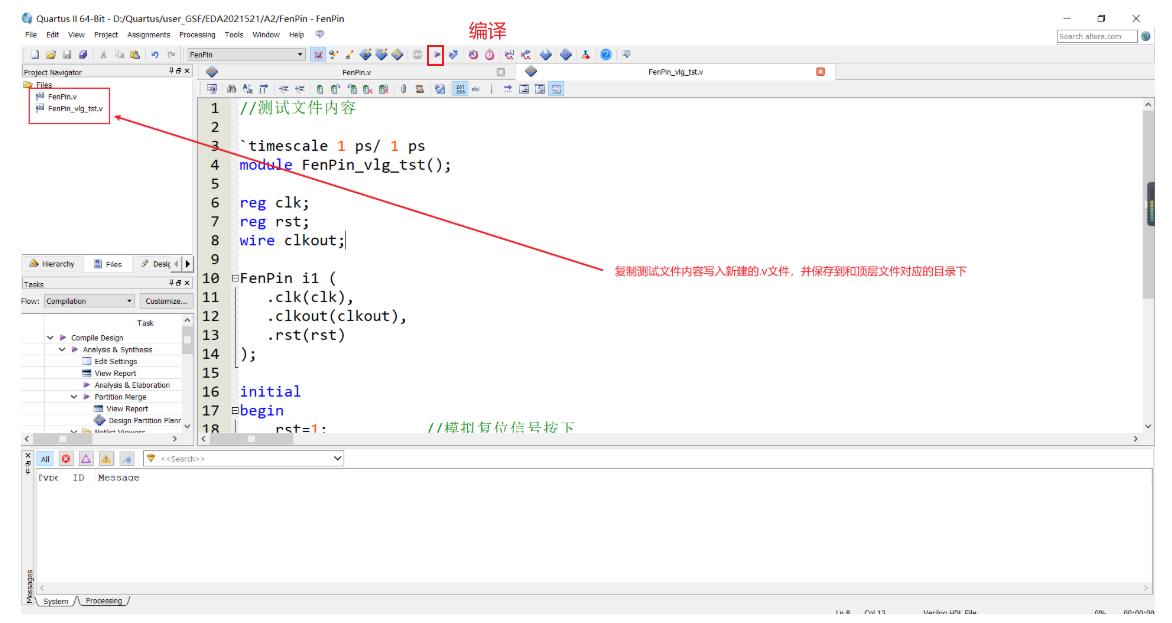

2、仿真步骤

3、编写测试文件

//测试文件内容

`timescale 1 ps/ 1 ps

module FenPin_vlg_tst();

reg clk;

reg rst;

wire clkout;

FenPin i1 (

.clk(clk),

.clkout(clkout),

.rst(rst)

);

initial

begin

rst=1; //模拟复位信号按下

#20 rst=0;

#20 rst=1;

#8000 $stop;

end

always

begin

#50 clk=1; //生成时钟信号

#50 clk=0;

end

endmodule

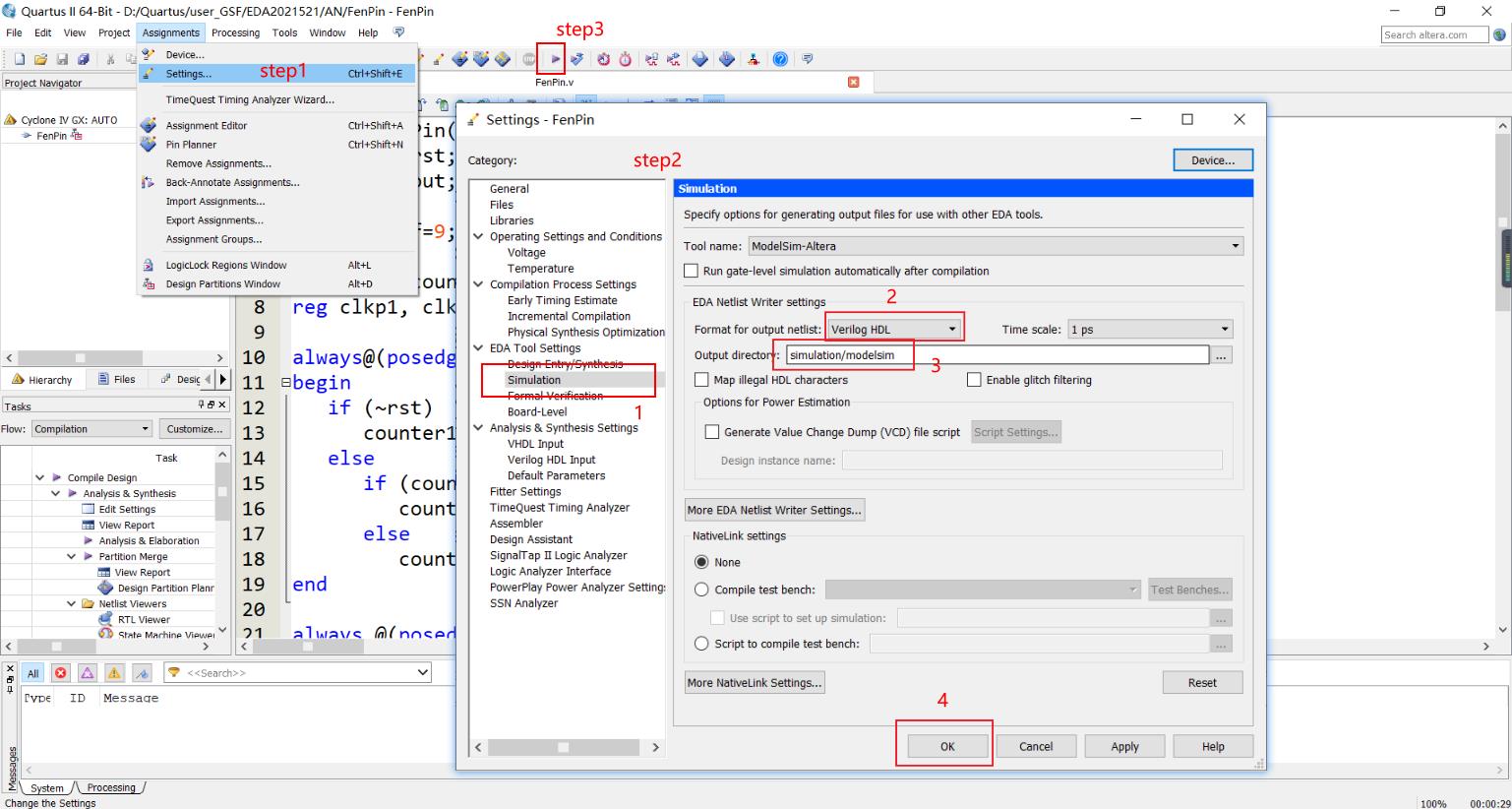

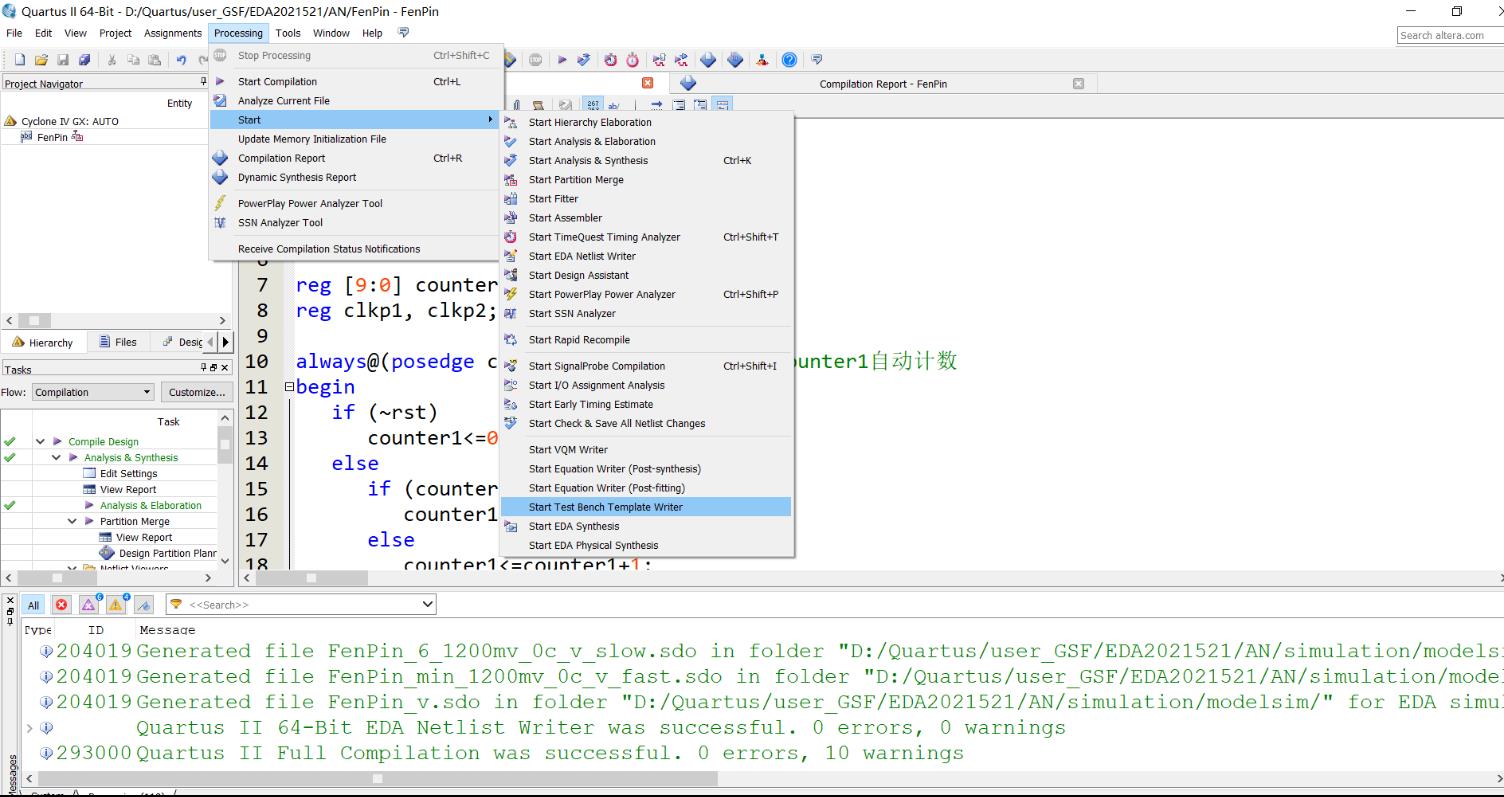

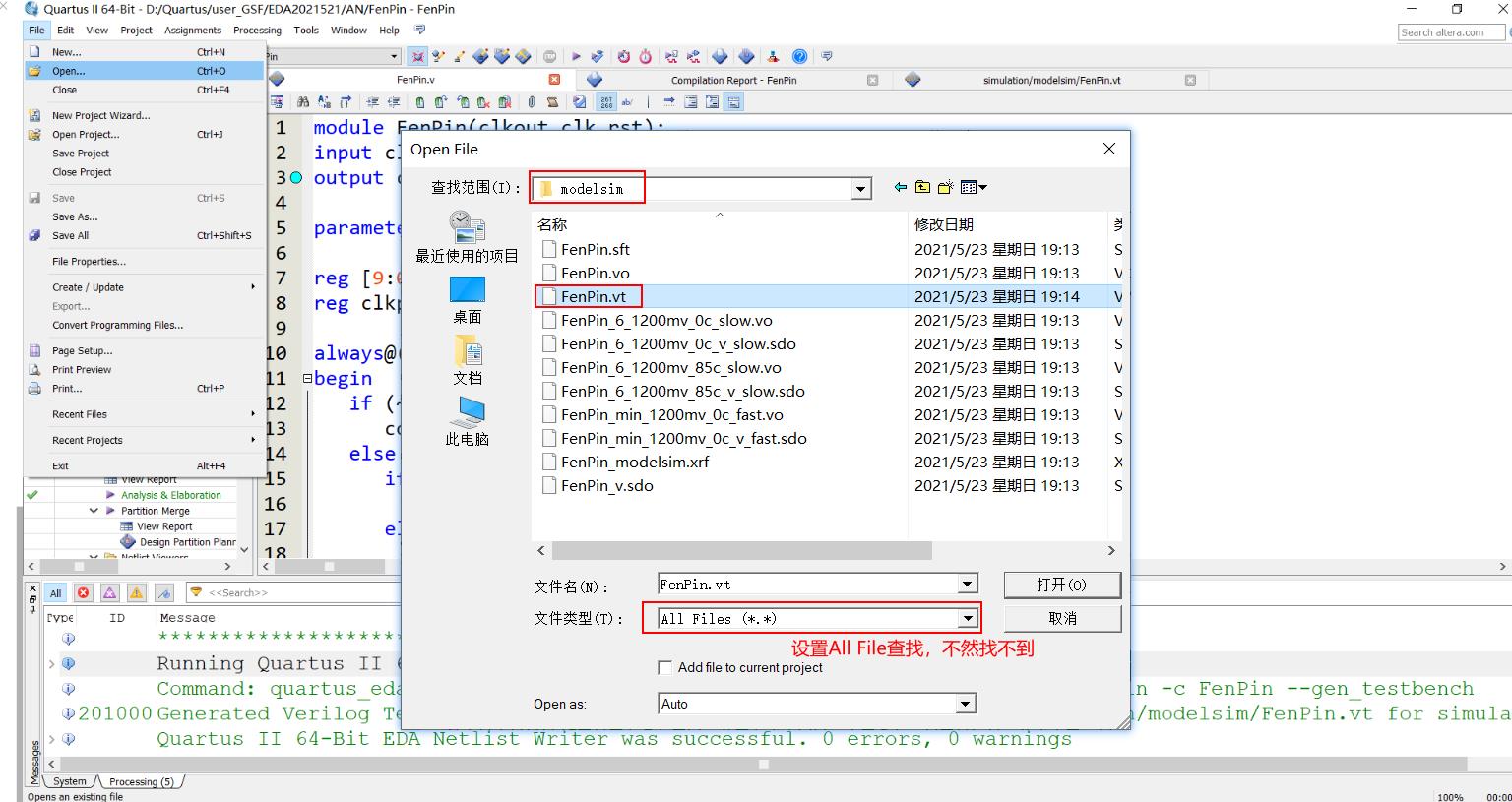

4、仿真前准备

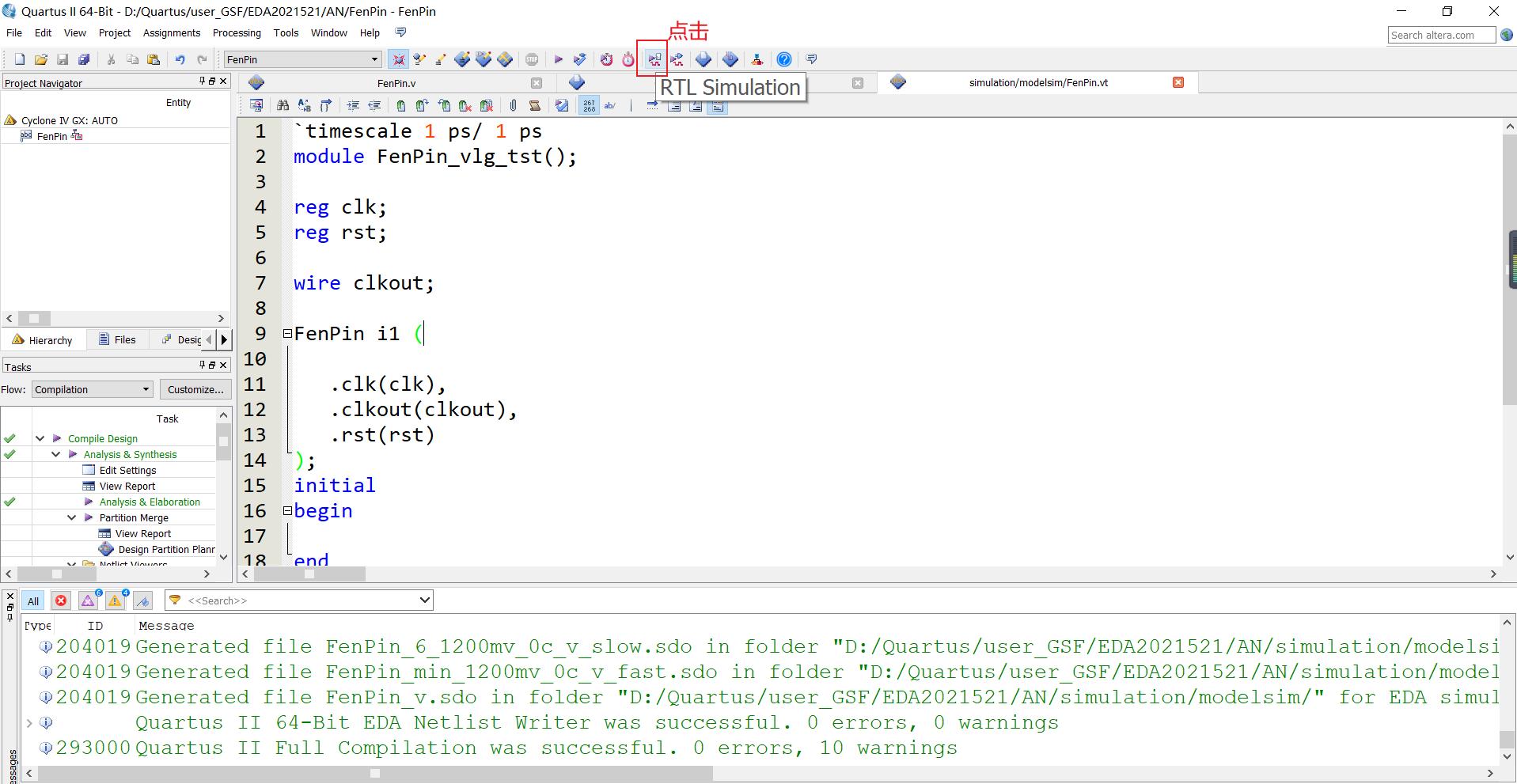

5、仿真

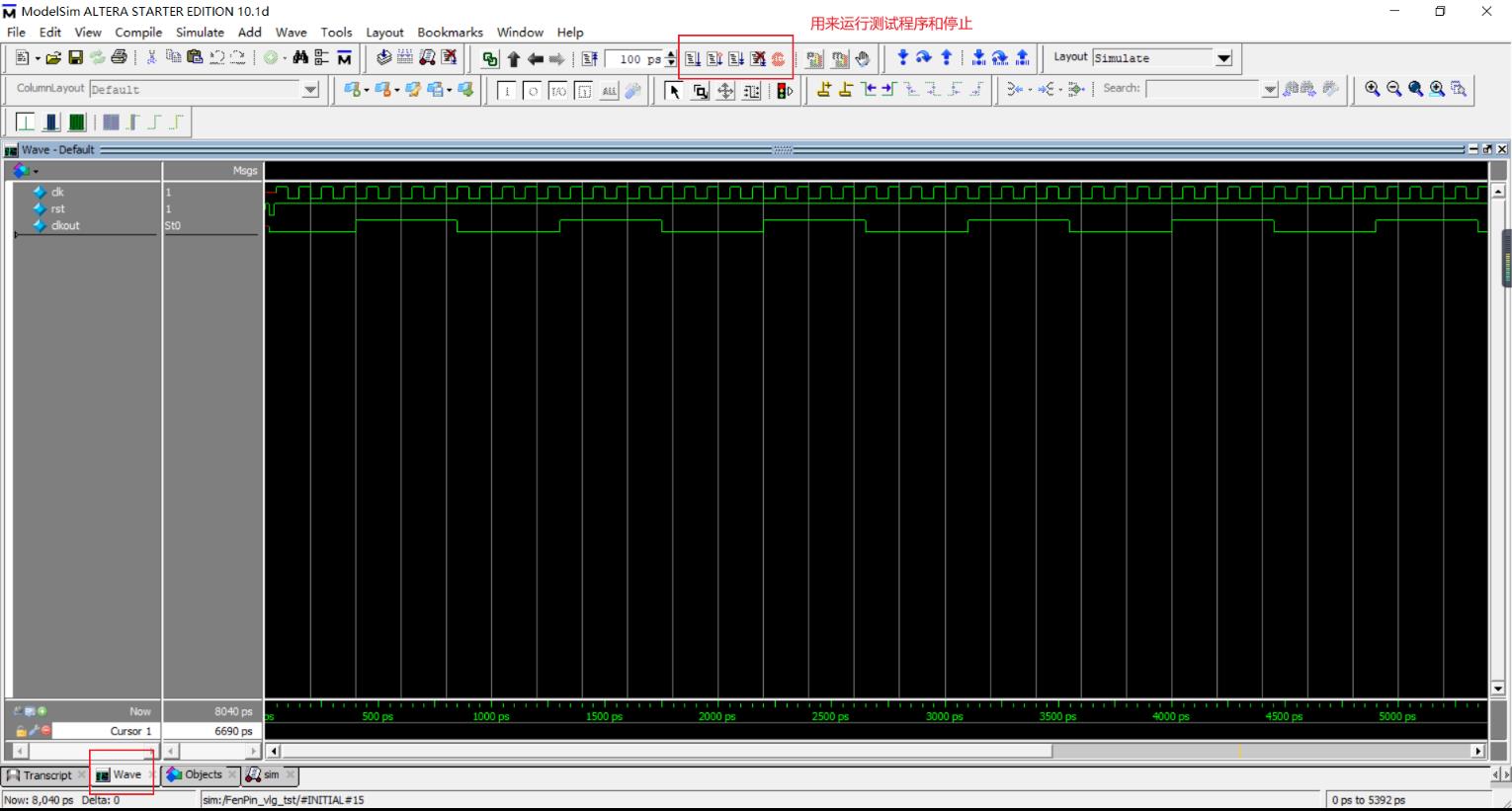

仿真完成

二、通过 “.v文件仿真”

1、准备工作

同于上述工程的代码

2、仿真文件编写

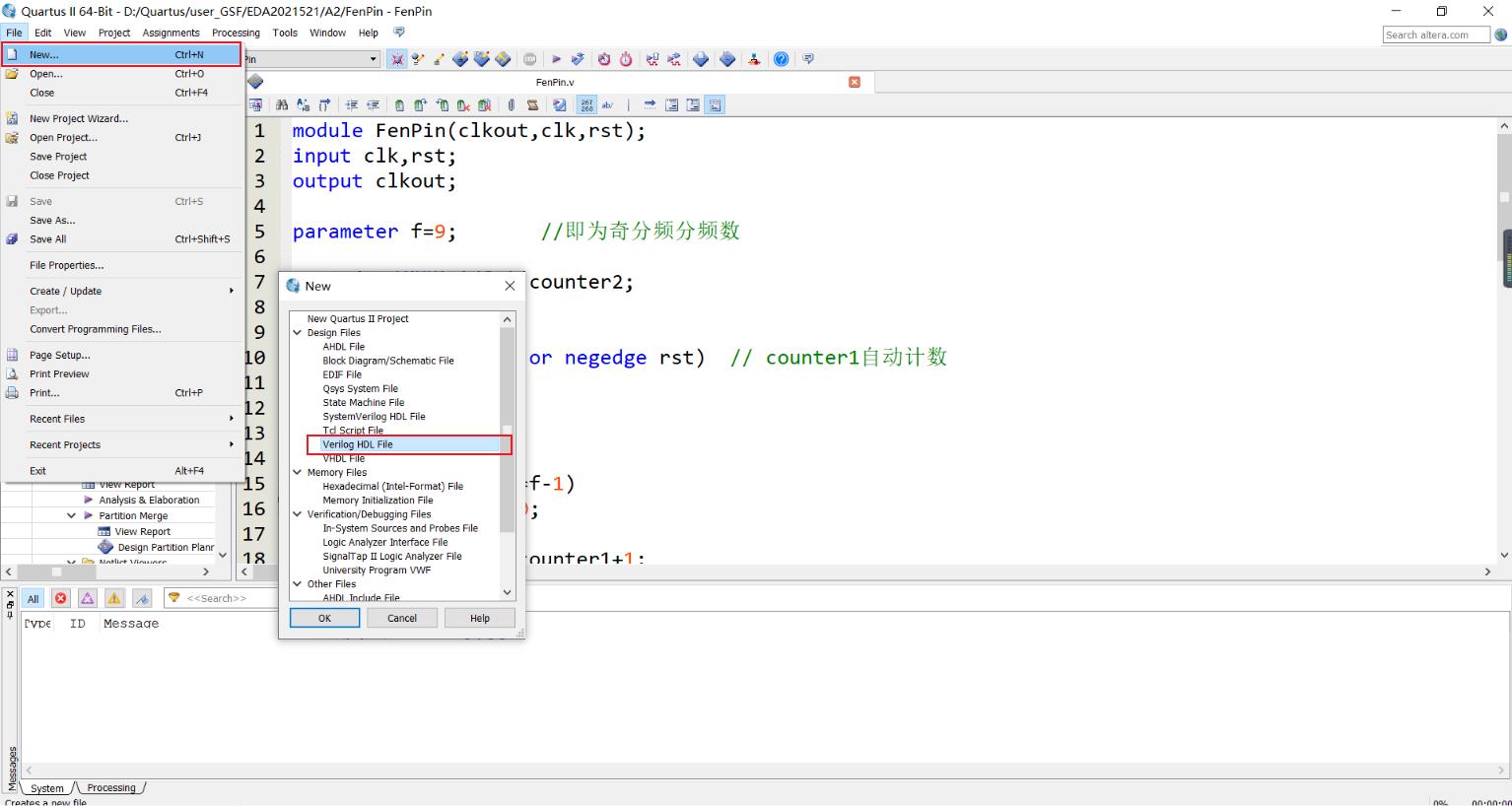

复制测试文件内容写入新建的.v文件,并保存到和顶层文件对应的目录下,编译整个工程

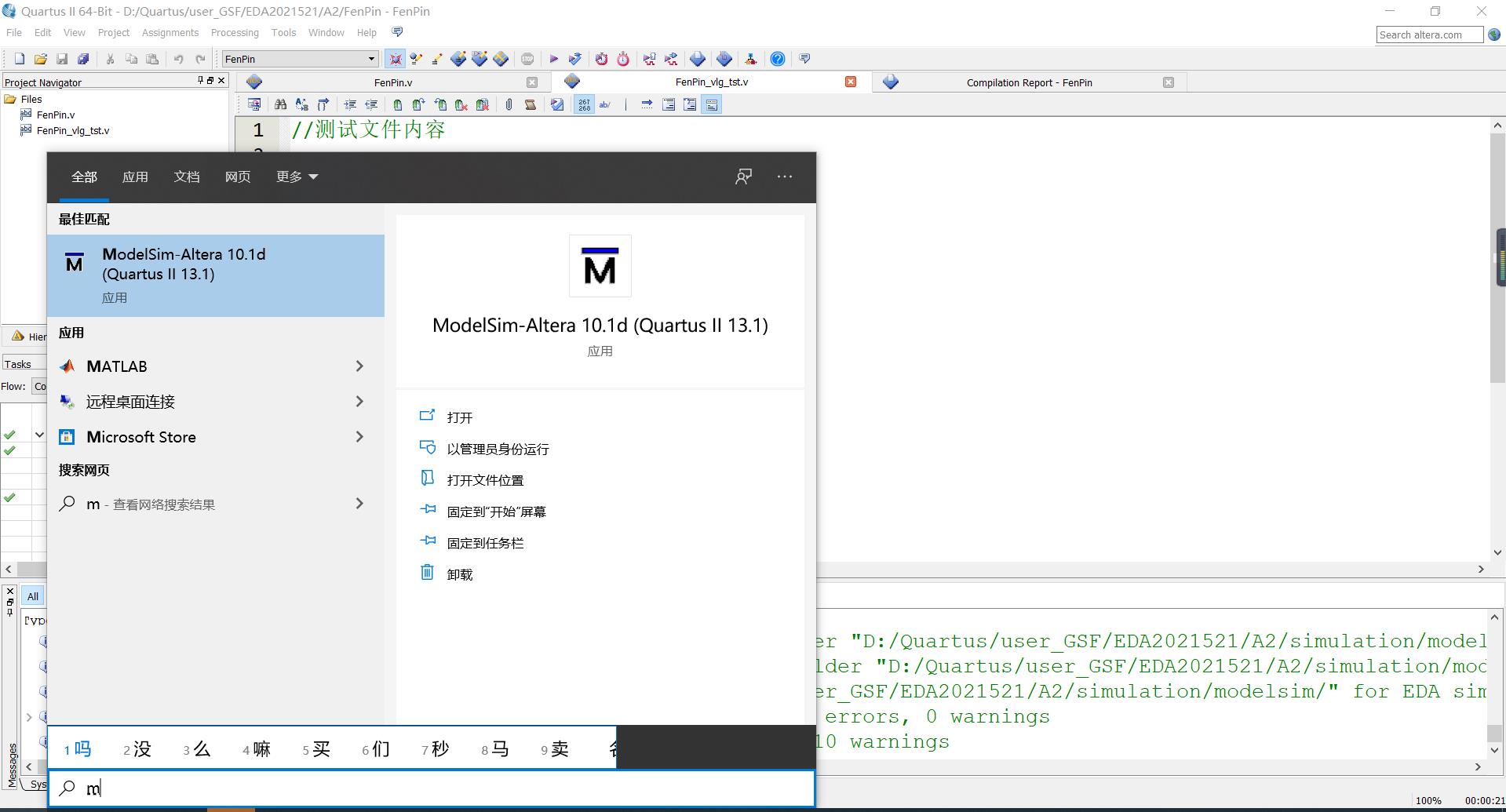

3、Modelsim软件准备

直接打开软件

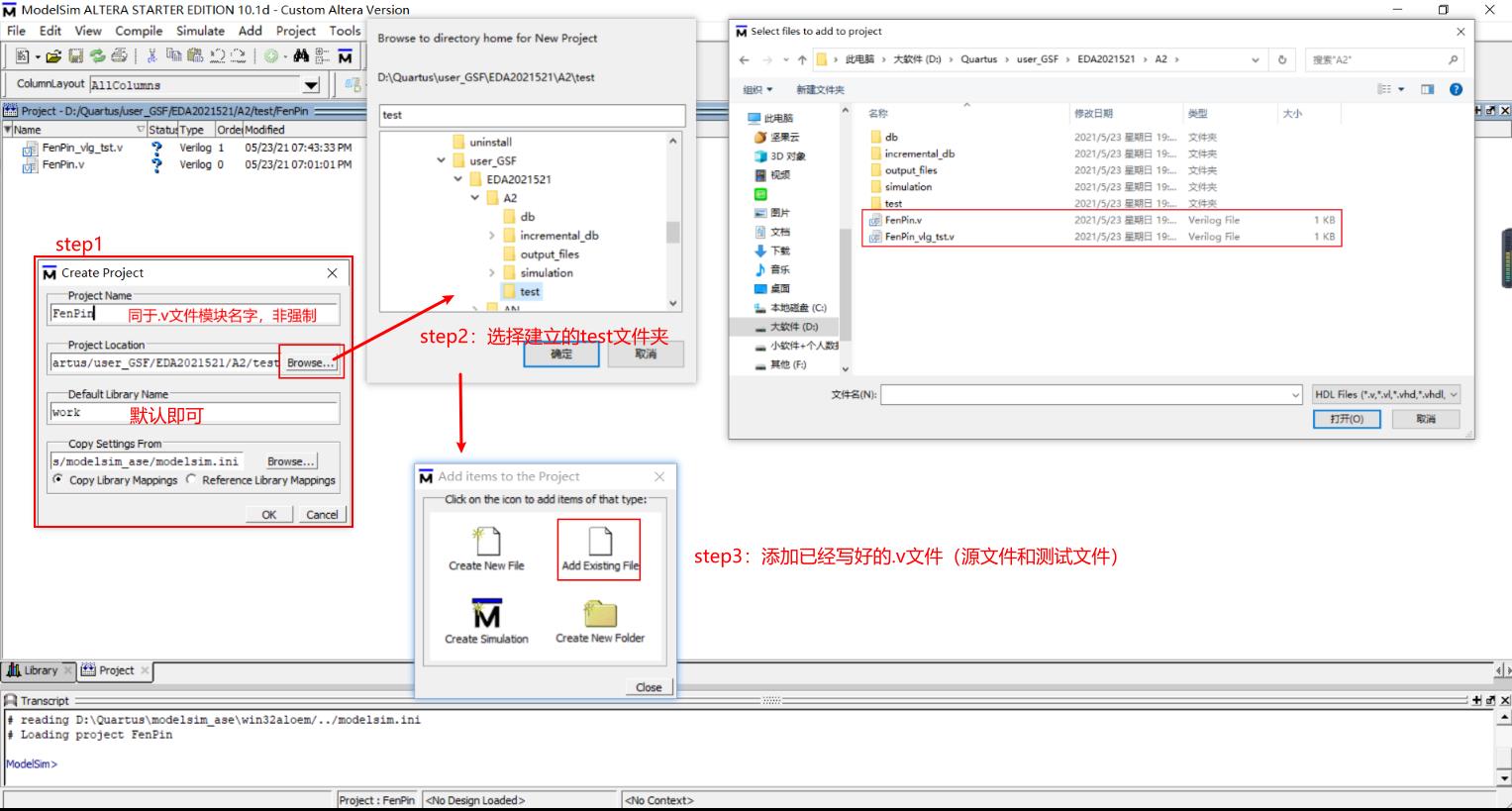

新建文件夹

新建测试文件工程

添加已写好的.v文件(源文件和测试文件)

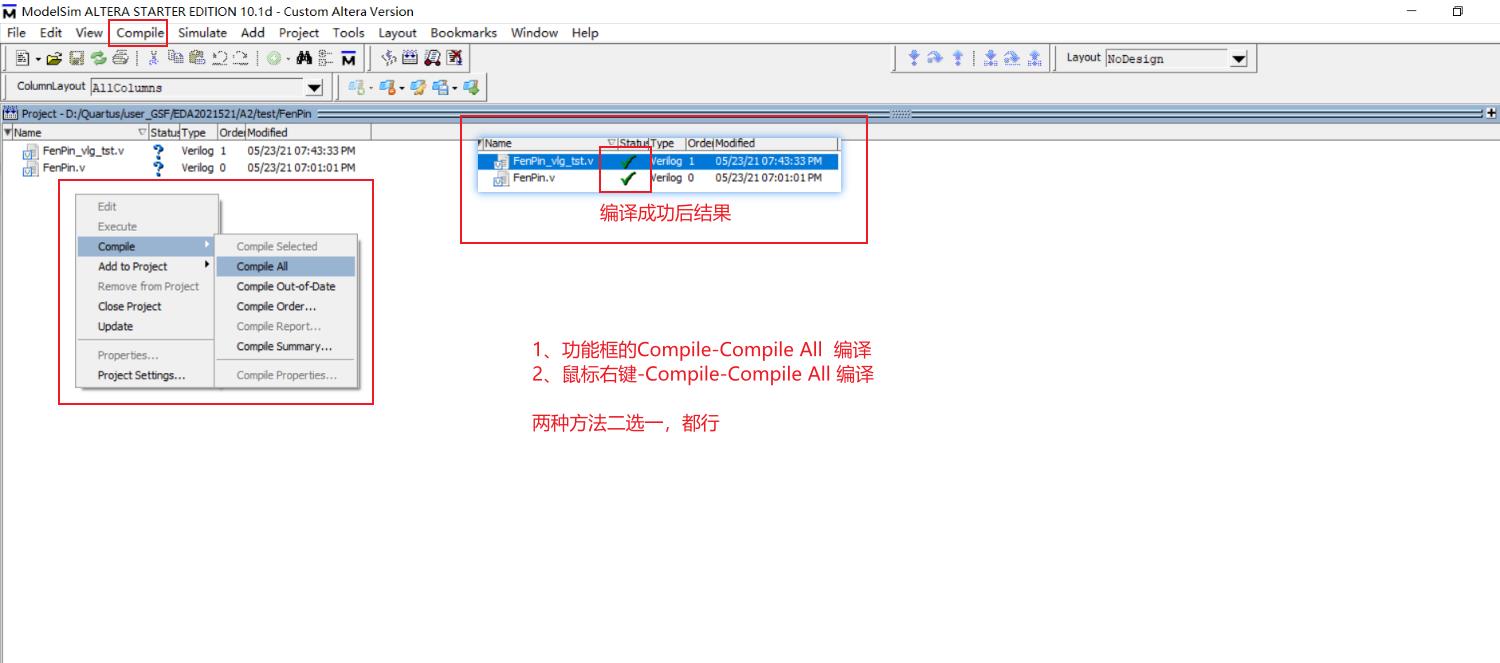

编译

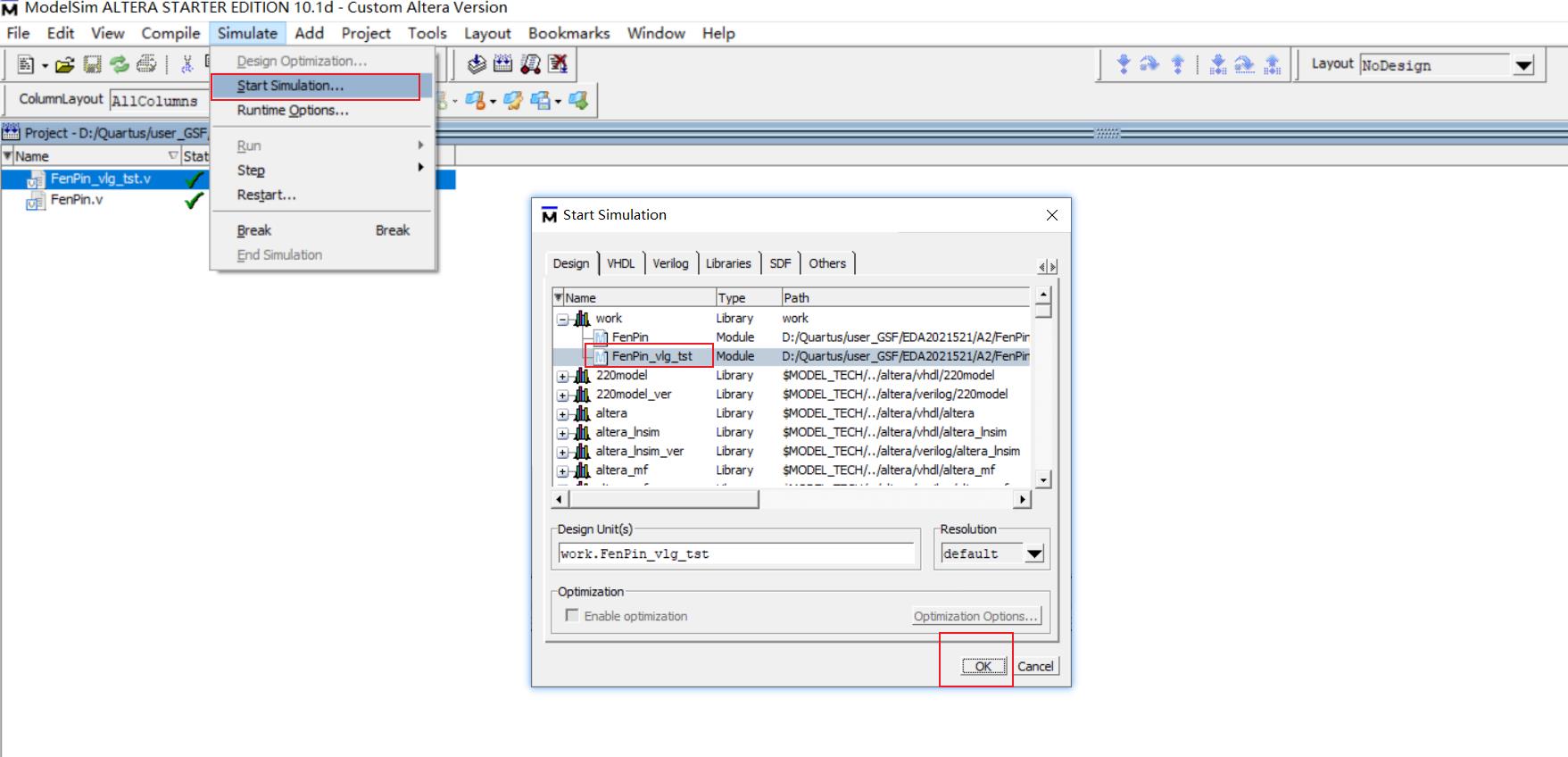

开始仿真

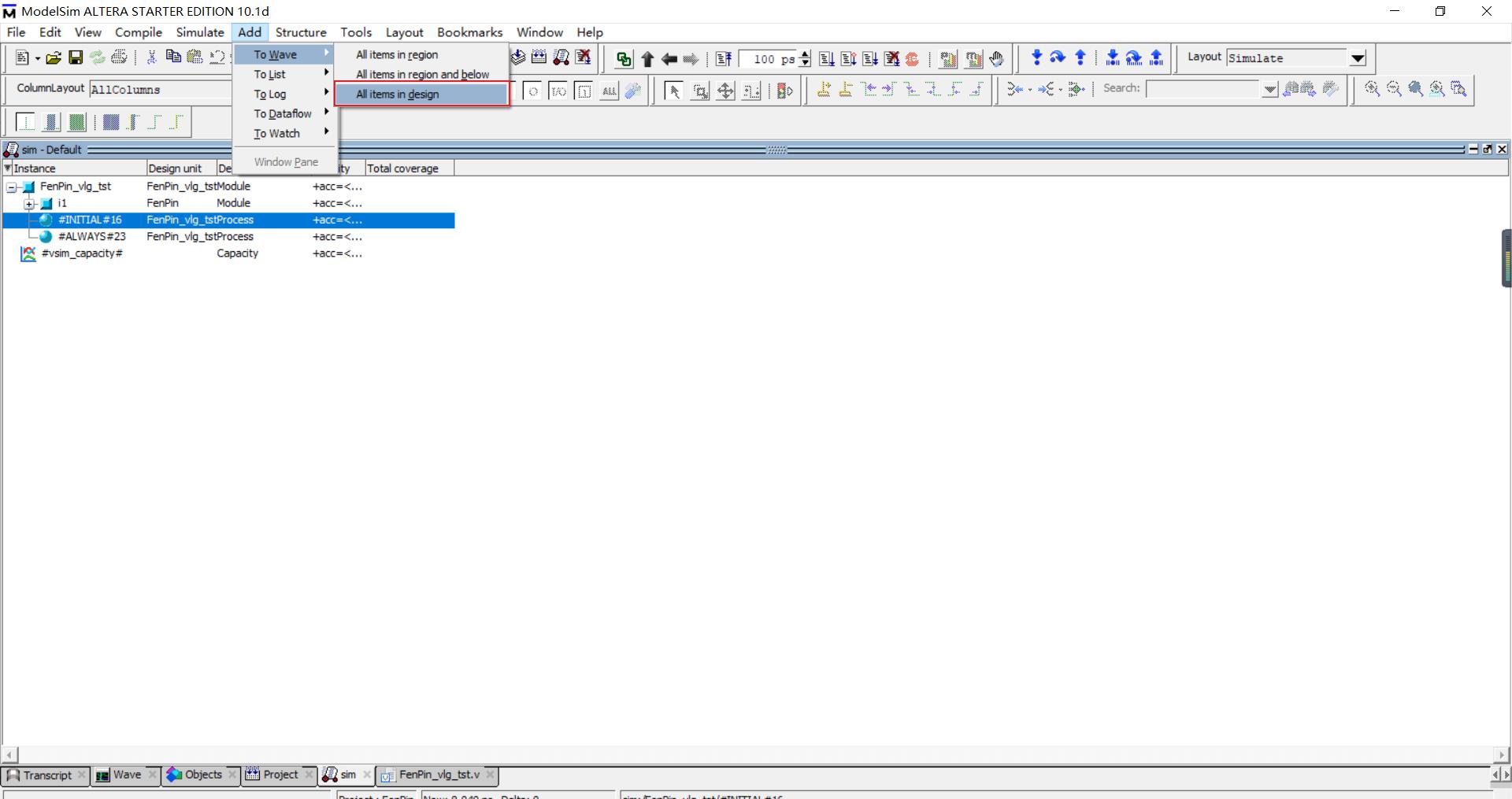

添加到波形仿真

仿真成功

注:最后一部分,不同人显示的界面可能多多少少不一样(多摸索摸索)

注

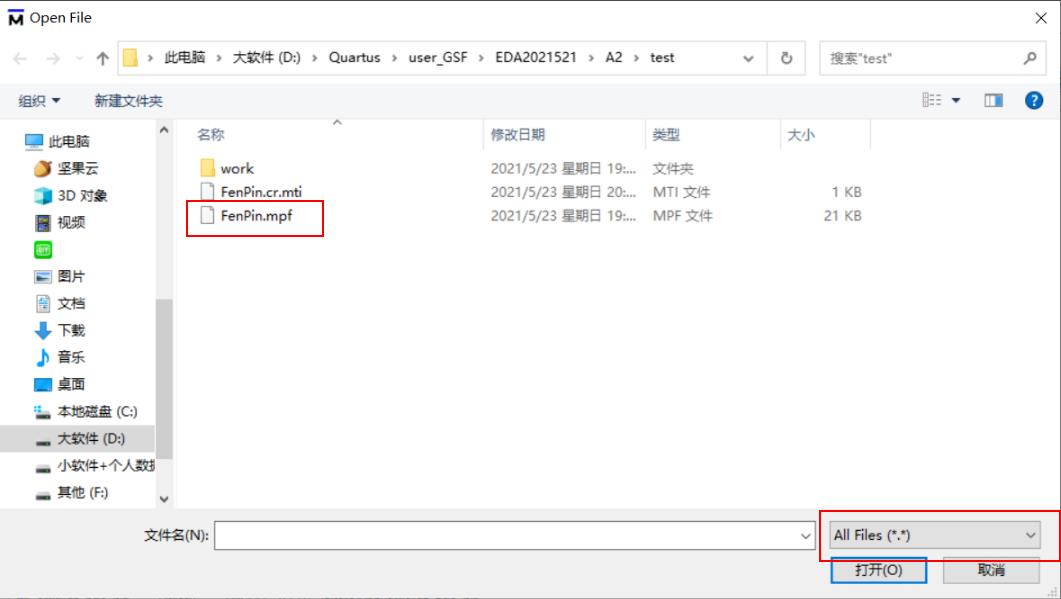

如果不小心关闭了工程,可以打开测试工程文件夹下面的 .mpf 文件来重新打开工程

以上是关于EDA仿真测试 Modelsim仿真 .vt文件法仿真 .v文件法仿真的主要内容,如果未能解决你的问题,请参考以下文章