AMD EPYC架构

Posted 造夢先森

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AMD EPYC架构相关的知识,希望对你有一定的参考价值。

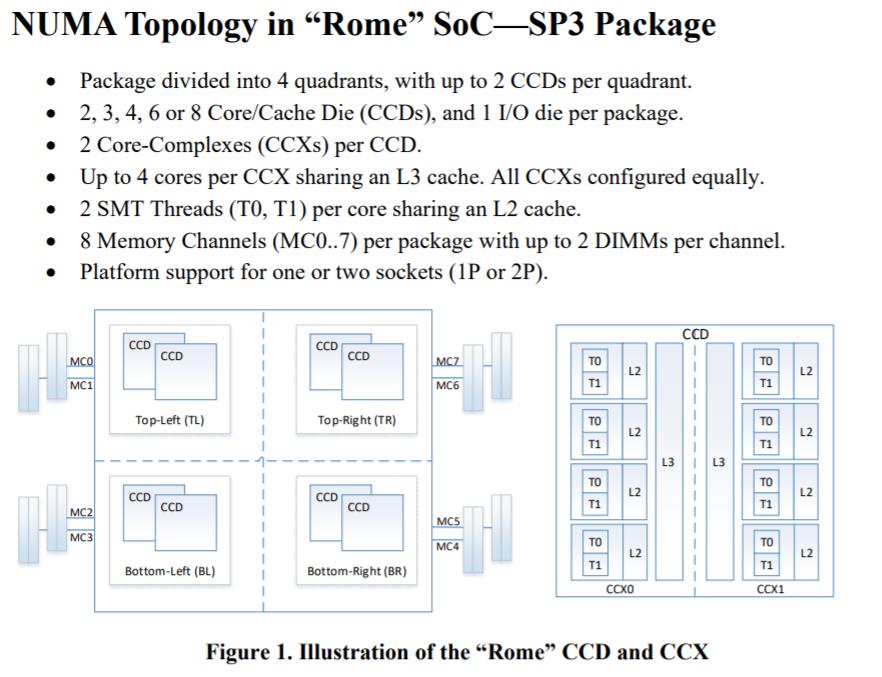

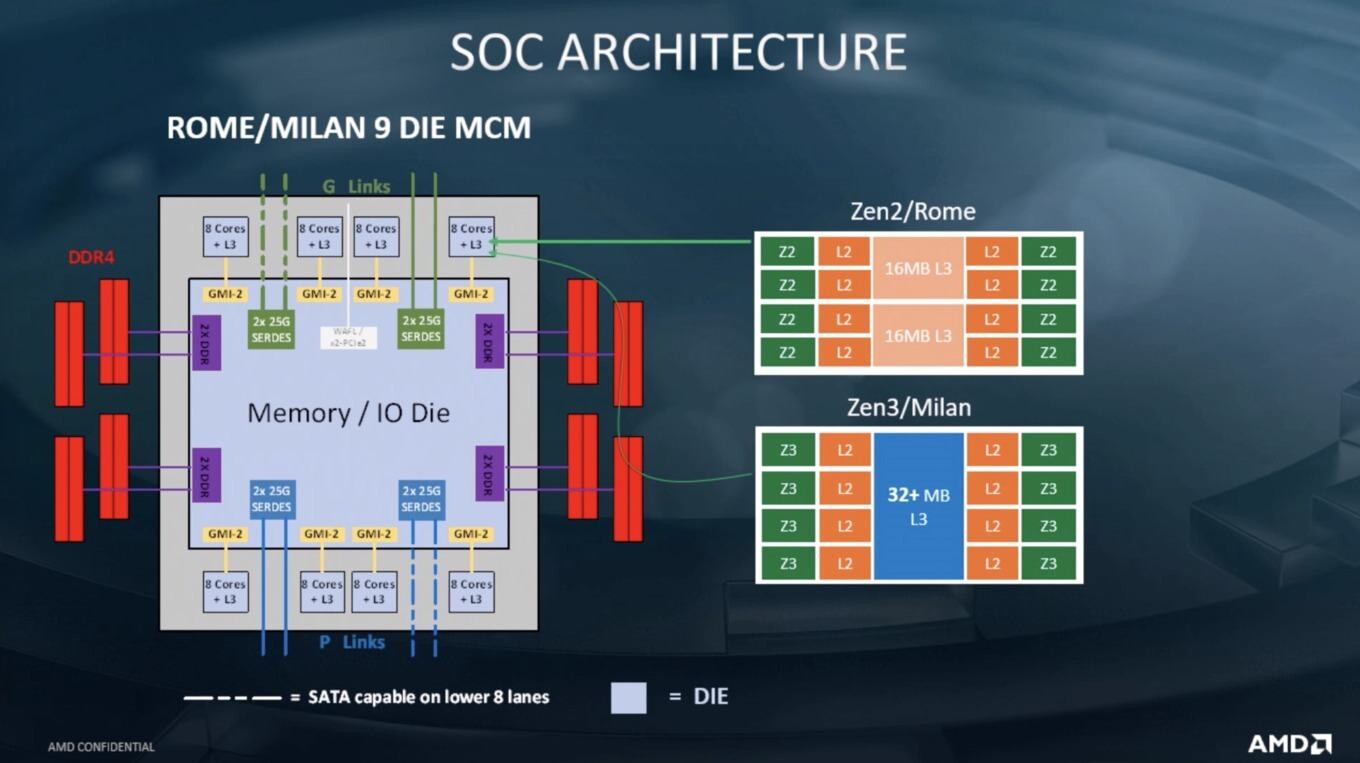

每个socket 8个CCD(Core Complex Die), 每个CCD:2 CCX(Core-Complex) x 4 Core x 2 Thread

从罗马到米兰,EPYC 处理器有哪些架构变化?

AMD EPYC 7742 64-Core Processor ----罗马

AMD EPYC 7T83 64-Core Processor ----米兰

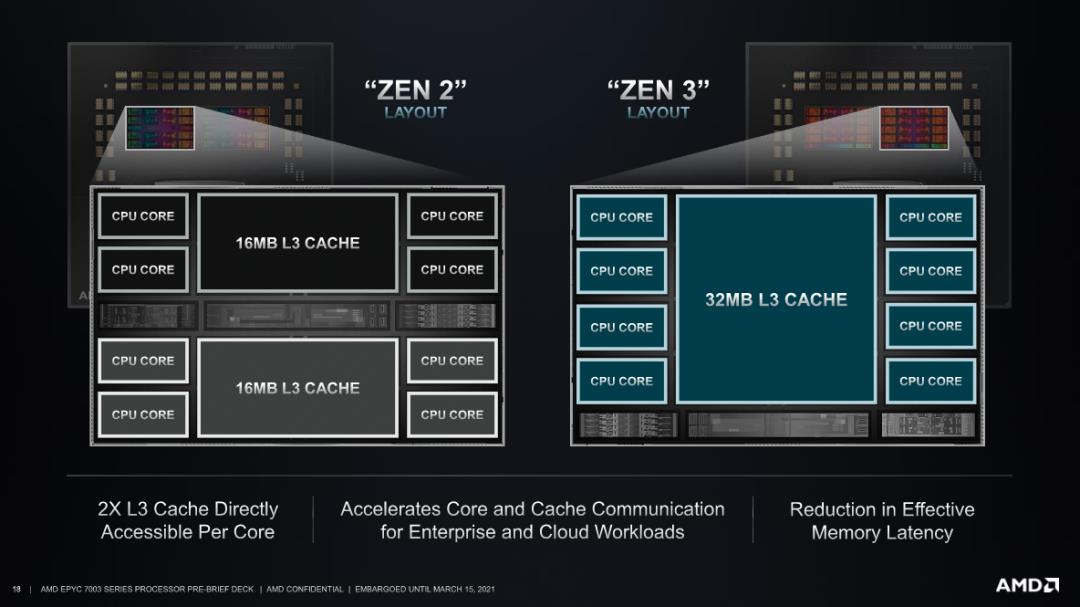

Rome CCX共享L3, Milan CCD共享L3。Zen 3 架构提供了比 Zen 2 更统一的 L3 缓存设计。Zen 2 / Rome 为每个四核组提供 16MiB L3 缓存,而 Zen 3 / Milan 为每个八核组提供 32MiB 的 L3 缓存,虽然每核的 L3 缓存还是 4MiB,但对于多核共享数据的工作负载而言,Zen 3 这种更统一的设计可以更好地节省缓存空间。

如果八核的 L3 缓存数据为 3MiB,则二代罗马处理器需要 6MiB,在每个四核组中它需要进行一次复制。而三代「米兰」处理器可以节省 3MiB 缓存,只用 3MiB 就可以服务八核,这也意味着单核可以处理更多 L3 缓存。其结果就是对于多核共享数据的工作负载而言,实现更快的内核与缓存通信,同时有效存储延迟也出现对应的降低。

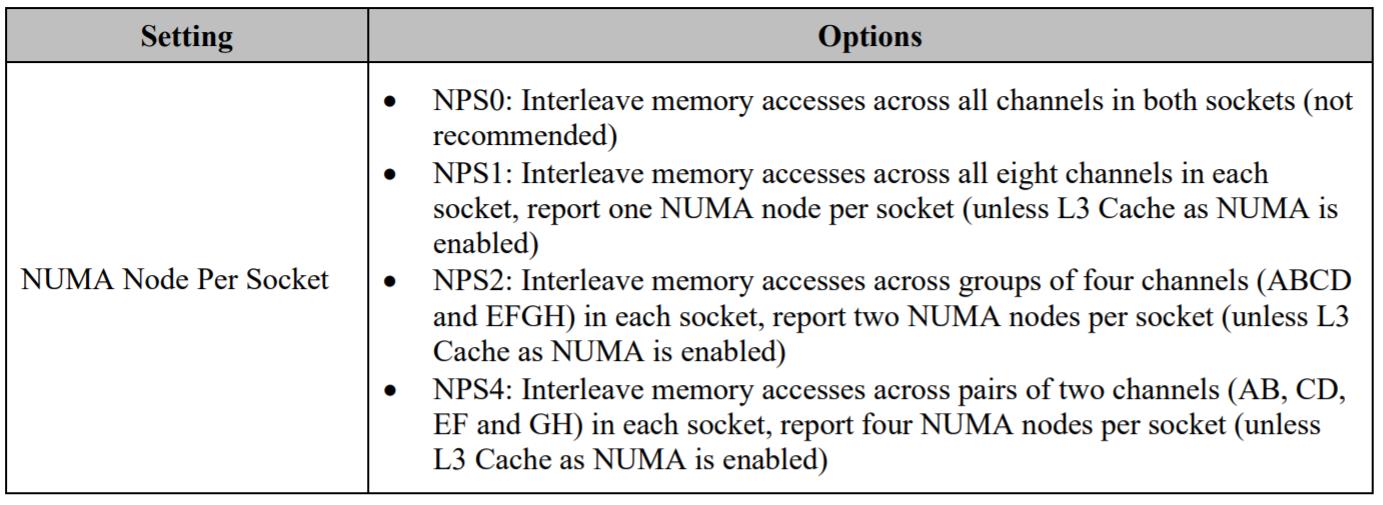

Numa Nodes Per Socket(NPSx):

The default configuration (one NUMA domain per socket) is recommended for most workloads.

NPS4 is recommended for HPC and other highly parallel workloads.

When using 200 Gbps network adapters, NPS2 may be preferred to provide a compromise between memory latency and memory bandwidth for the NIC.

This setting is independent of ACPI SRAT L3 Cache as NUMA Domain

参考资料:

High Performance Computing: Tuning Guide for AMD EPYC™ 7002 Series Processors

Socket SP3 Platform NUMA Topology for AMD Family 17h Models 30h–3Fh

Workload Tuning Guide for AMD EPYC 7002 Series Processor Based Servers

以上是关于AMD EPYC架构的主要内容,如果未能解决你的问题,请参考以下文章

AMD重回服务器:Oracle甲骨文宣布将使用AMD EPYC处理器