Simulink HDL Coder FPGA开发实践之 基本使用流程介绍

Posted 肆拾伍

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Simulink HDL Coder FPGA开发实践之 基本使用流程介绍相关的知识,希望对你有一定的参考价值。

前言: 本栏目除特别说明以外,均采用的黑金AX7103开发板,该开发板时钟频率为200M,并且是双端时钟,因此在每个项目中都有一段原语将双端时钟变成200MHz的单端时钟。文章仅作为学习记录,如有不足请在评论区指出,博主不会对各位的问题作出解答,请谅解。博主深知网络上关于HDL Coder的资料十分稀少,特别是中文资料几乎没有,并且官方给出的例子大多挺难不适合入门,因此将自己摸索的过程记录下来,希望给后人一些启发。

Simulink HDL Coder系列教程(一) Simulink实现计数器

本文根据Mathworks官方提供的范例,对HDL Coder的使用进行全流程的介绍,根据本文走一遍就基本知道如何将Simulink模型编译成HDL代码以及上板测试了。

一、一个简单的例程

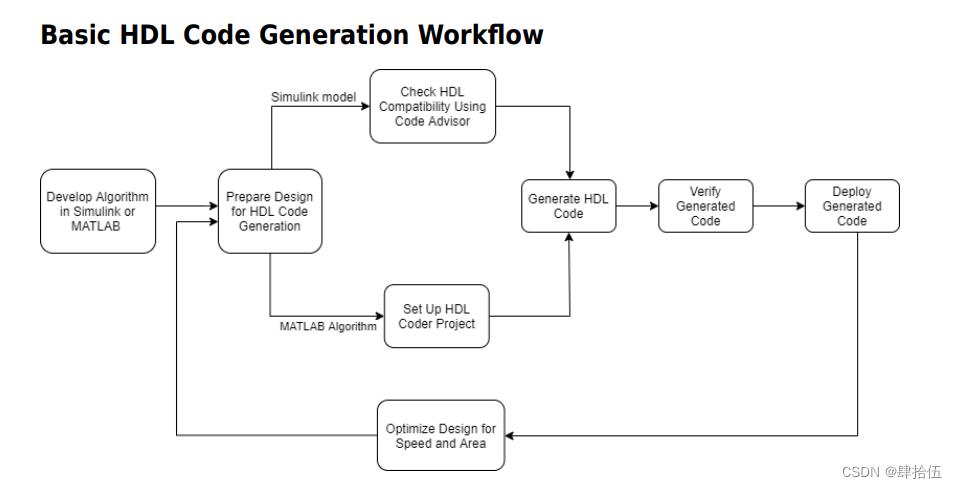

1.1 典型的设计流程图

1.2 新建HDL slx文件

打开simulink,新建文件,在HDL Coder下找到空白模板:

Mathworks 提供的各种范例参见:

cd (fullfile(matlabroot,'toolbox','hdlcoder','hdlcoderdemos'))

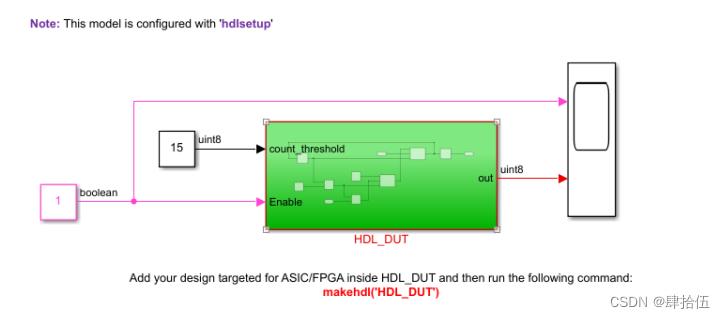

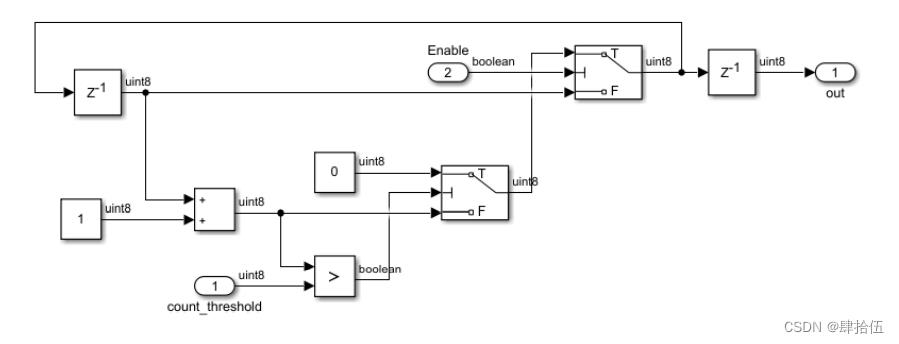

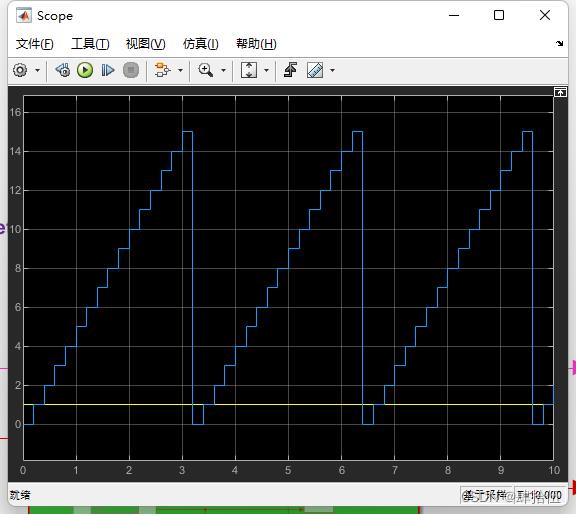

1.3 搭建好模型并进行仿真

按照上面提供的图片,可以搭建好模型,然后运行,可以在示波器中查看到结果,是一个计数器。还要记得改变模块输出变量类型。

二、生成代码和报告

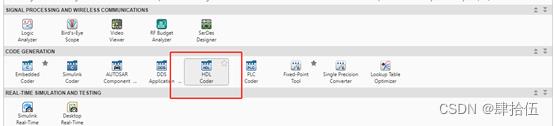

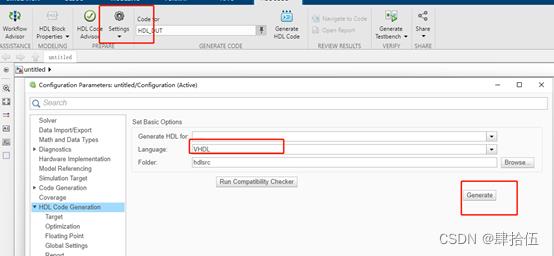

更改代码生成的设置: APP-> HDL Coder

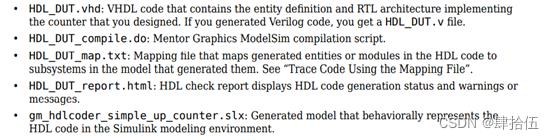

生成的文件格式:

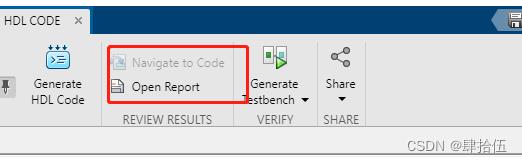

双向导航:

这个可以帮助我们定位代码和对应的模块。

这个可以帮助我们定位代码和对应的模块。

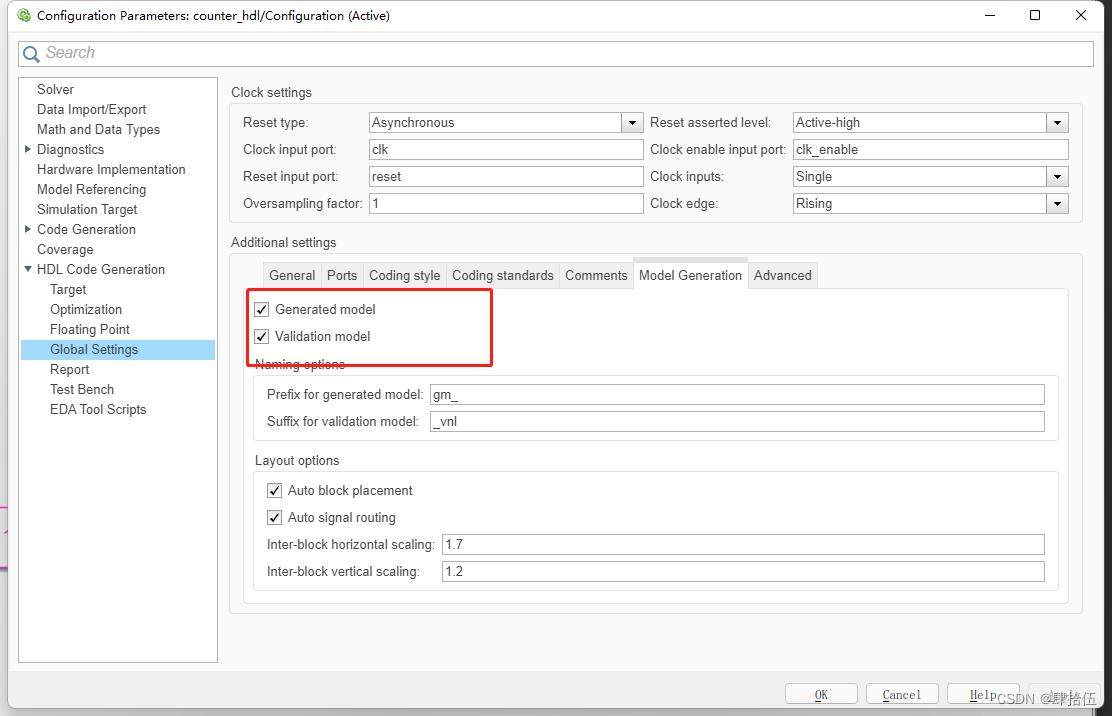

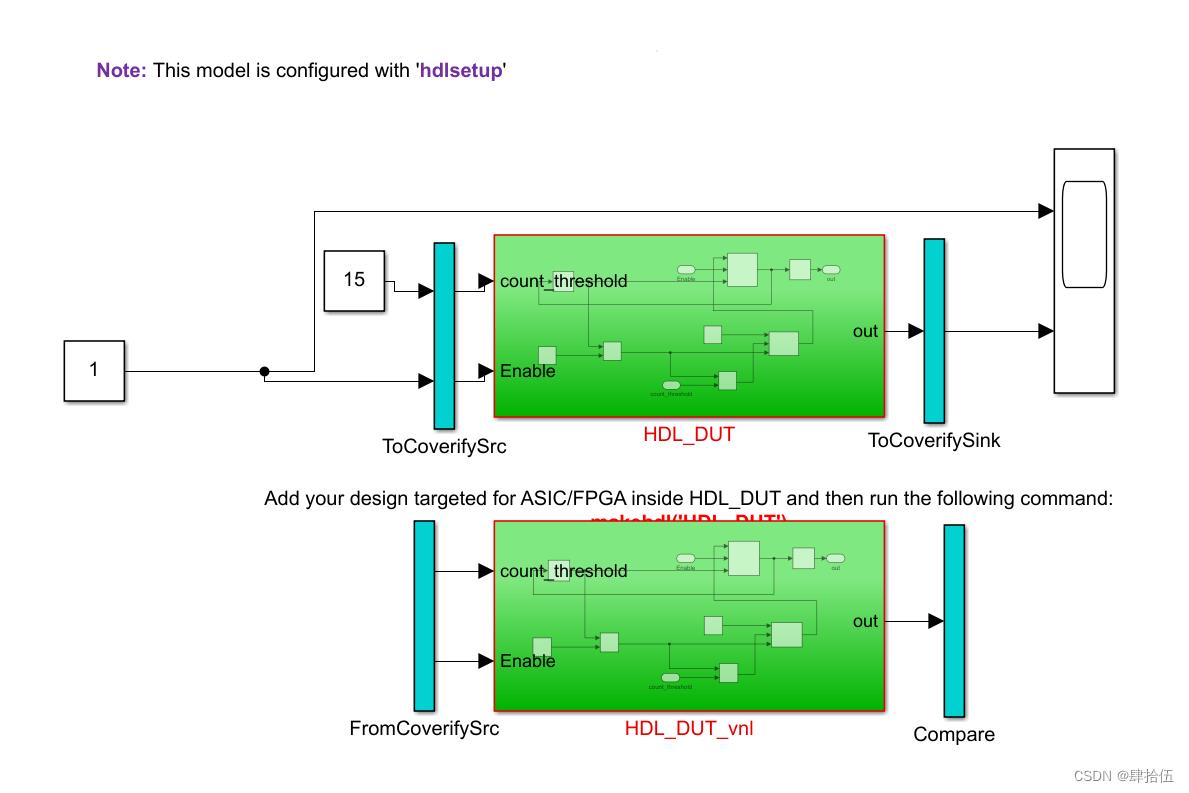

三、生成验证模型并进行对比

这一步实际上是两个模型进行数据对比,一个是原型,也就是自己搭建的模型,一个是验证模型,就是实际上生成HDL代码的模型,这个模型是经过Simulink优化成适合输出为HDL代码的模型,二者不一定是完全一致的。

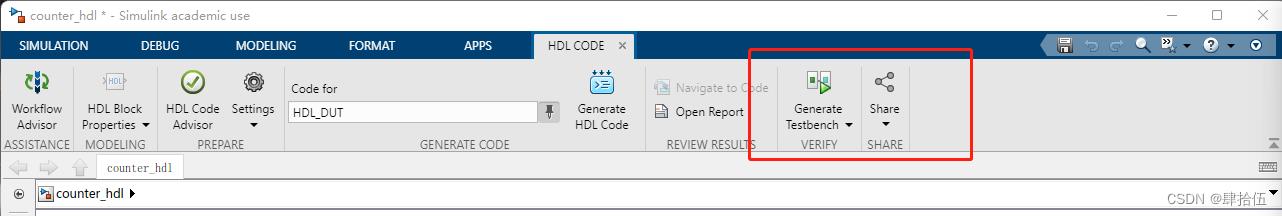

四、生成Testbentch

同时我们还可以在Simulink中查看Vivado的仿真结果,但是我一般不使用,都是只生成代码,然后仿真的步骤都在Vivado里面完成,想了解请参照官方文档。

本例程链接:

链接:https://pan.baidu.com/s/1vlacGBpB9kyP2FcWtZg3NQ?pwd=1111

提取码:1111

–来自百度网盘超级会员V6的分享

以上是关于Simulink HDL Coder FPGA开发实践之 基本使用流程介绍的主要内容,如果未能解决你的问题,请参考以下文章